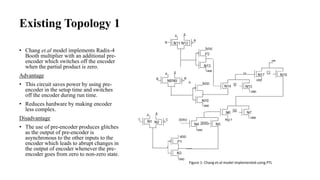

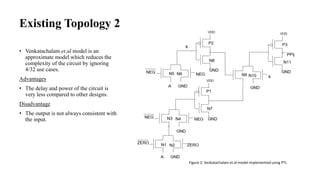

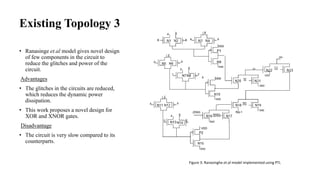

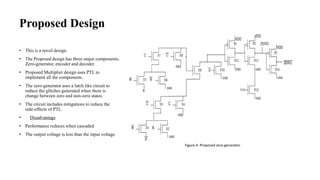

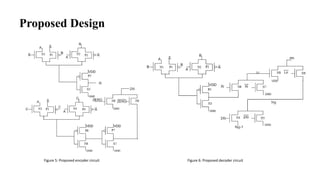

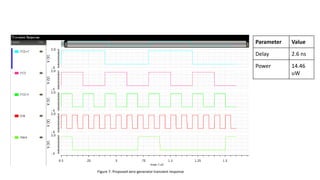

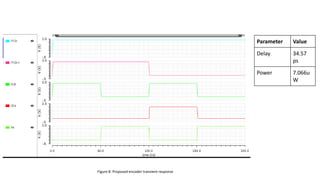

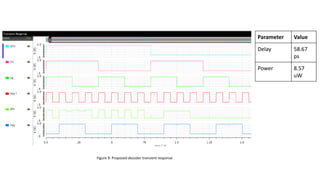

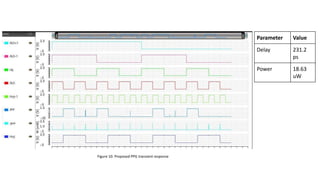

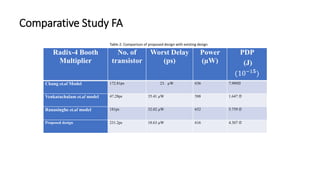

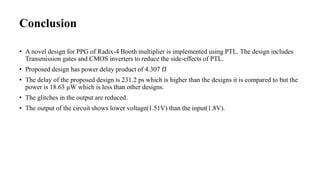

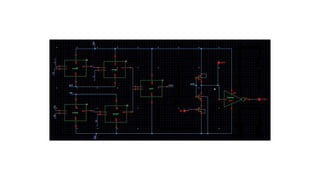

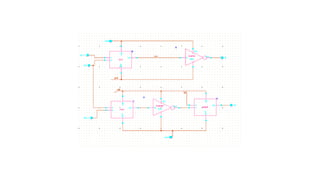

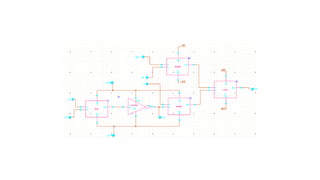

The document is a presentation on a study of a low power Radix-4 Booth multiplier using Pass Transistor Logic (PTL). It discusses existing Radix-4 Booth multiplier topologies and their limitations. It then proposes a novel design that uses PTL to implement the zero-generator, encoder, and decoder components of the partial product generator (PPG) in order to reduce glitches and power consumption. Simulation results show the proposed design has a power-delay product of 4.307 fJ, lower than the compared existing designs. While the delay is higher, the power is the lowest at 18.63 μW. The design thus achieves lower power consumption for the Radix-4 Booth multiplier PPG