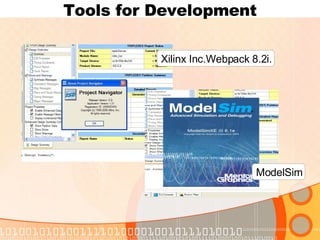

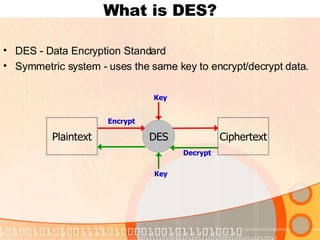

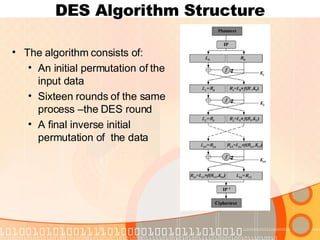

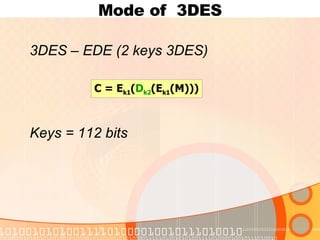

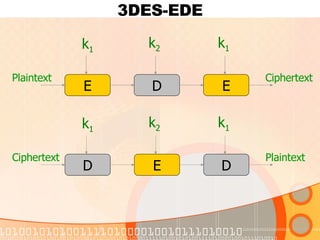

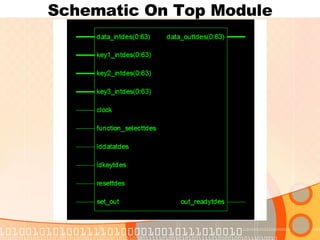

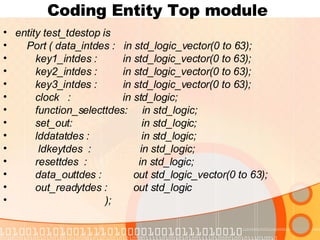

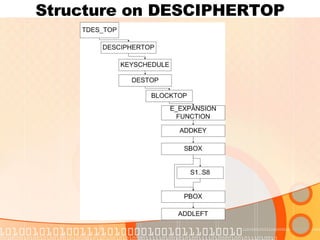

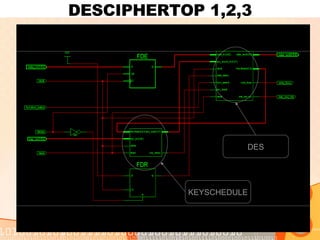

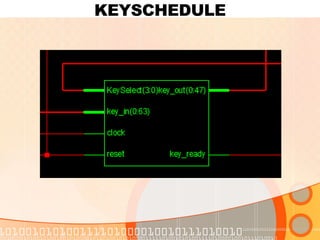

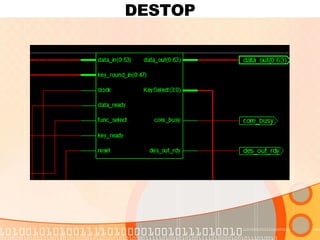

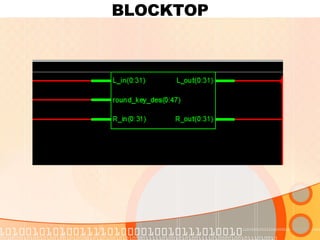

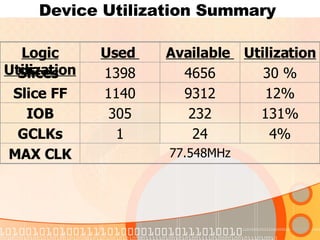

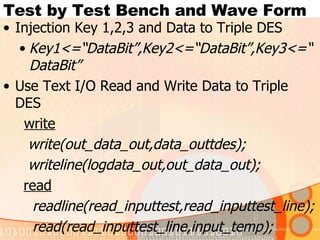

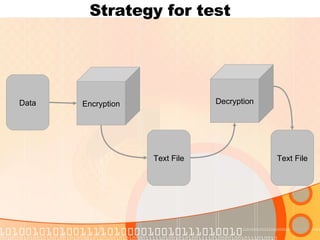

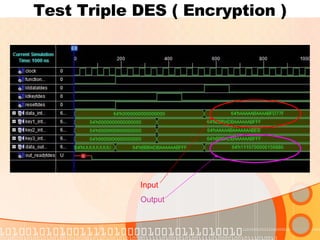

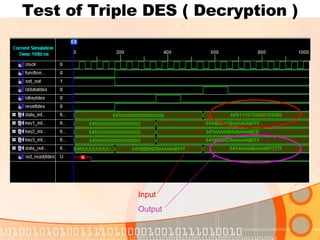

The document discusses the simulation of a Triple Data Encryption Standard (Triple DES) circuit using VHDL. It provides background on Triple DES, describes the design and structure of the Triple DES circuit in VHDL, and presents the results of testing the encryption and decryption functions of the circuit through simulation. Testing showed the circuit correctly performed encryption and decryption on input data using the Triple DES algorithm. The design utilized some FPGA resources but would require a clock generator and RAM for implementation on an actual FPGA board.