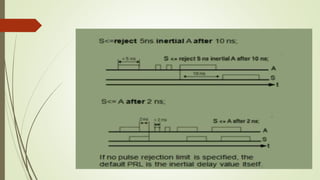

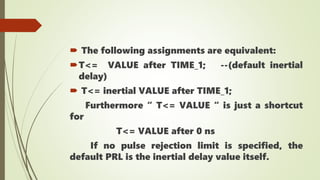

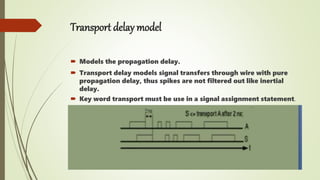

The document discusses delay models in VHDL, specifically inertial and transport delays. Inertial delay helps filter out noise in switching circuits, while transport delay models pure propagation without filtering. The conclusion emphasizes the usefulness of both models in modeling signal delays and propagation.