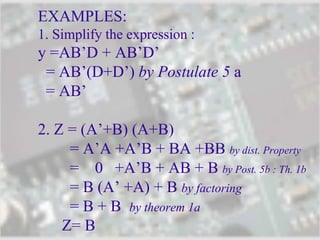

The document discusses logic circuits and summarizes key concepts including:

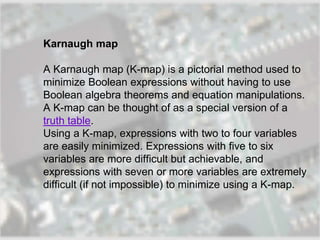

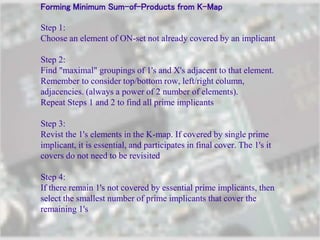

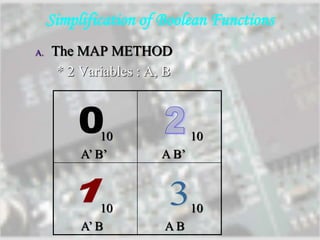

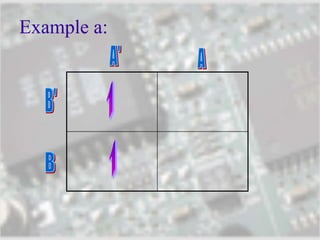

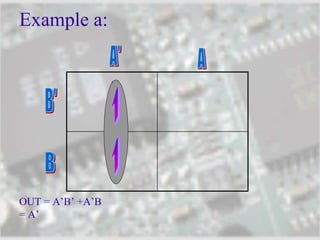

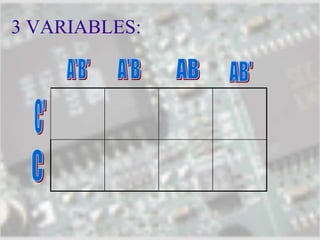

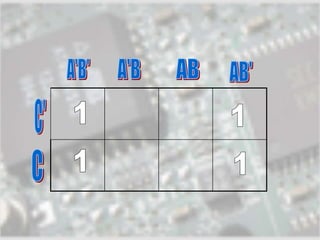

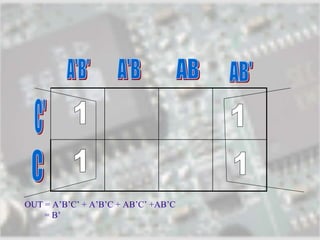

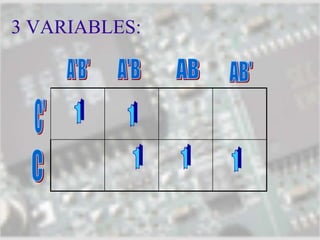

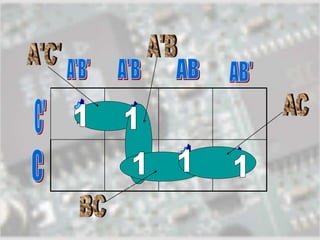

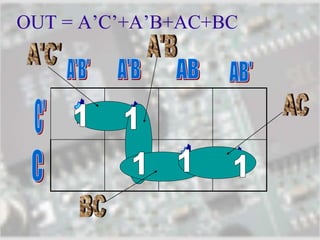

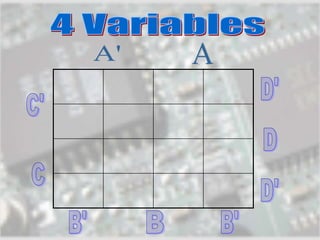

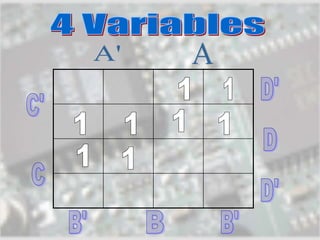

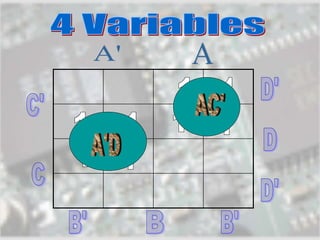

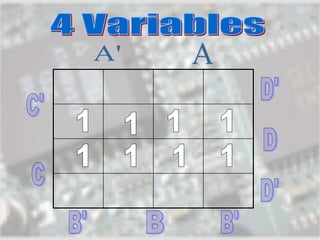

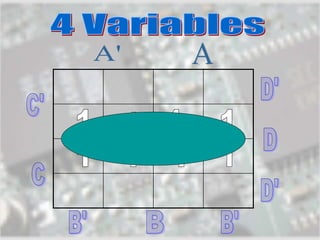

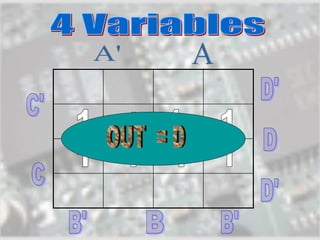

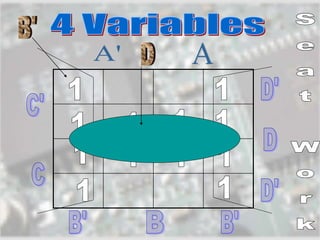

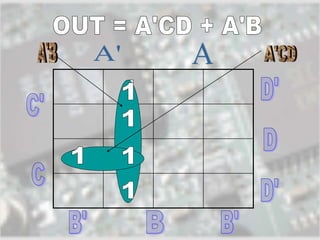

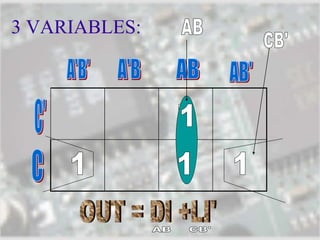

1. Karnaugh maps are used to minimize Boolean expressions without using algebra by grouping adjacent 1's and X's. They are useful for expressions with 2-4 variables.

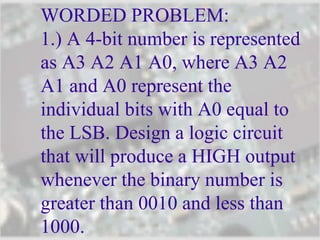

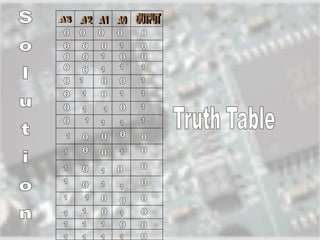

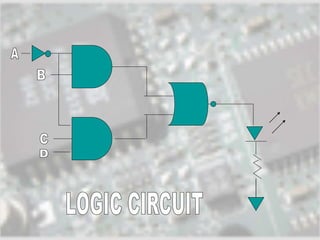

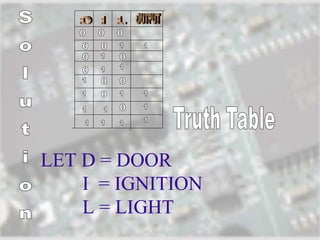

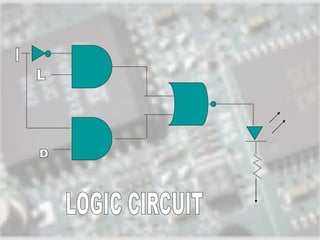

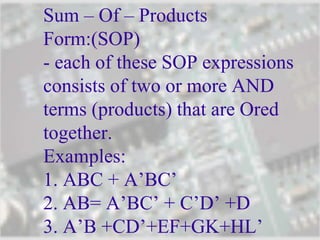

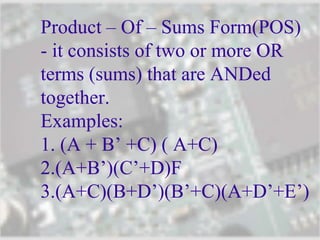

2. Truth tables and sum-of-products (SOP) form are introduced to represent logic expressions. Examples show converting between truth tables, SOP expressions, and logic circuits.

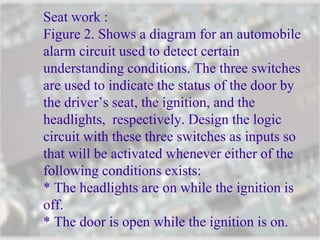

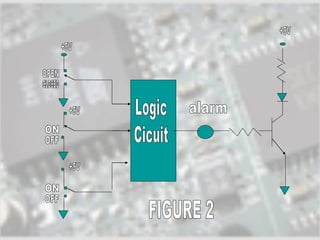

3. A worked example of a logic circuit is presented to detect conditions for an automobile alarm based on door, ignition, and headlight switches.

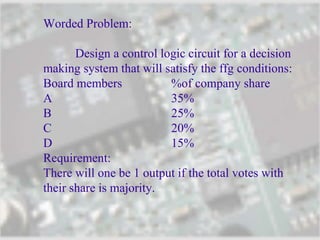

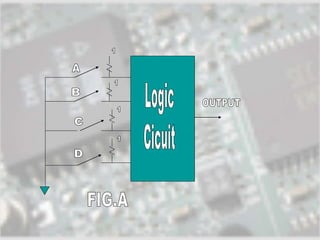

4. Objectives of an experiment on combinational logic circuits are outlined, including deriving and simplifying logic equations, converting

![3. Z = ( A + B’ +C )’

= A’ [ ( B’*C)’]

=A’ [ B’’+C’ ]

= A’ [ B + C’ ]

= A’B + A’C’](https://image.slidesharecdn.com/digl-elexday5recorded-lec-200716065400/85/D-igl-elex-day5_recorded-lec-8-320.jpg)

![4. W= [(A+BC)(D+EF)]’

= (A+BC)’ + (D+EF)’

= A’ (BC)’ + D’ (EF)’

= A’ ( B’+C’) + D’(E’+F’)

=A’B’ +A’C’ +D’E’ +D’F’](https://image.slidesharecdn.com/digl-elexday5recorded-lec-200716065400/85/D-igl-elex-day5_recorded-lec-10-320.jpg)