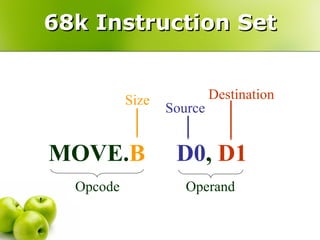

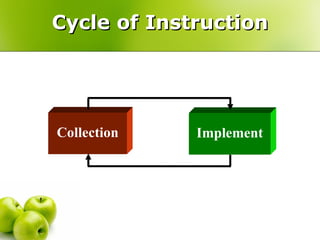

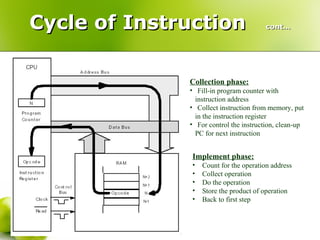

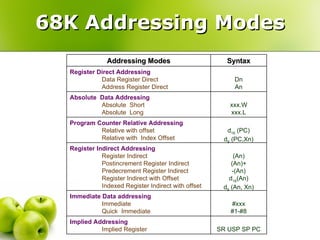

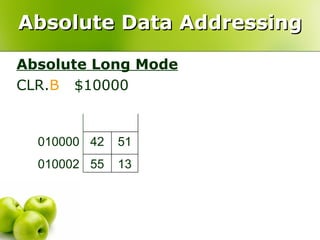

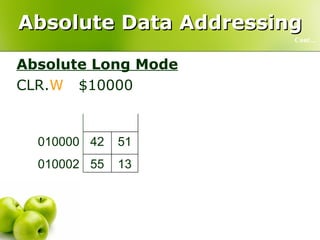

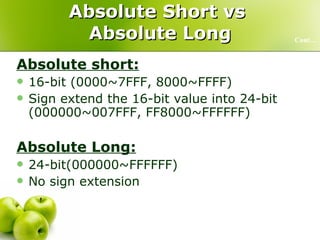

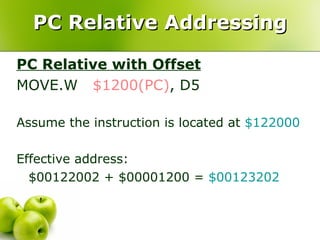

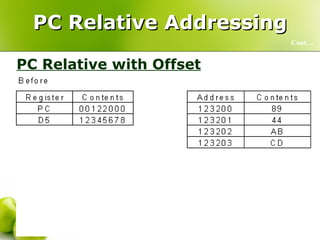

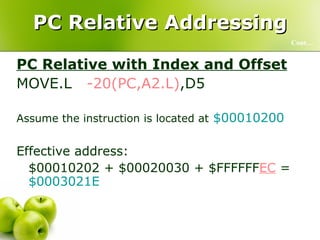

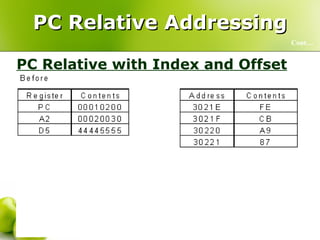

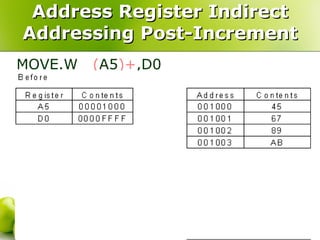

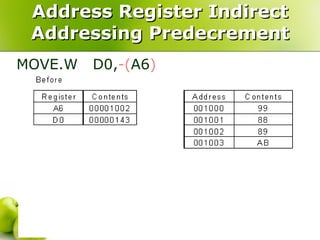

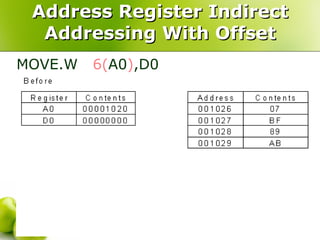

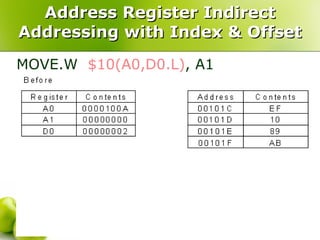

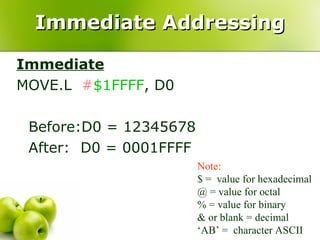

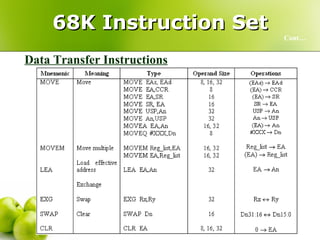

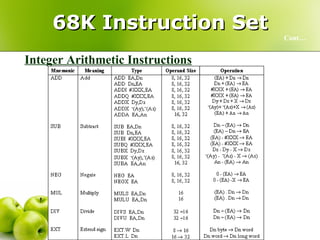

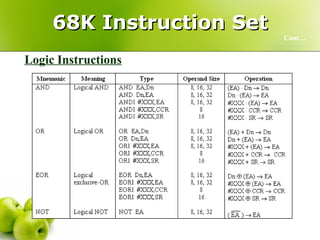

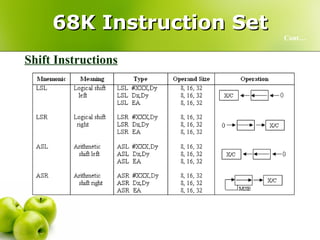

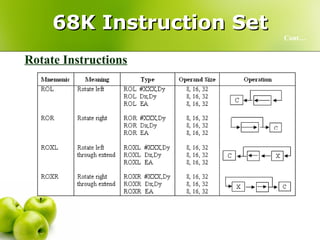

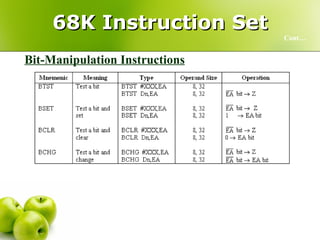

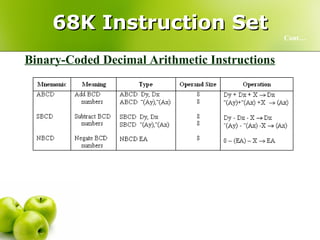

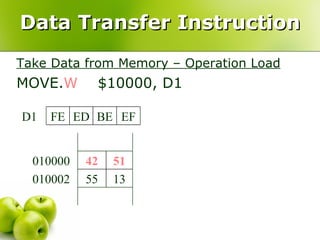

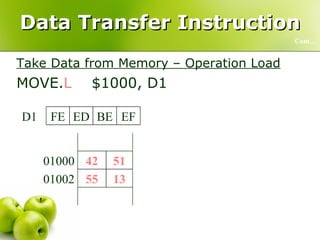

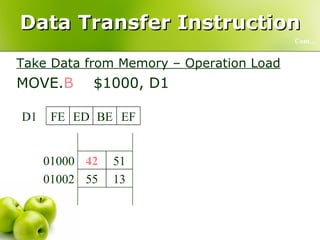

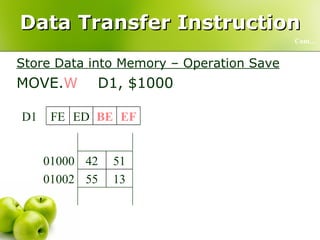

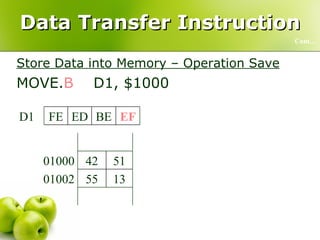

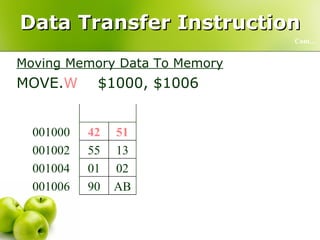

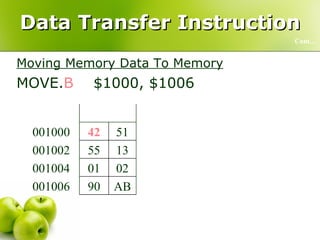

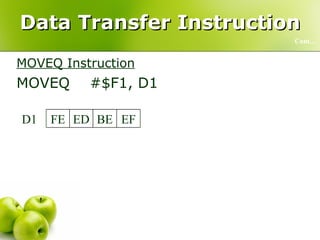

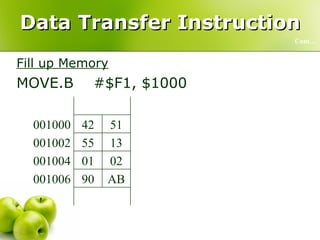

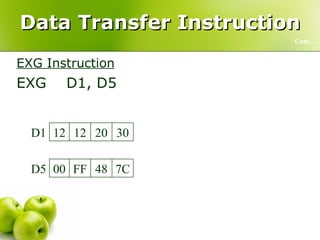

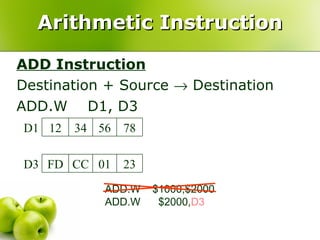

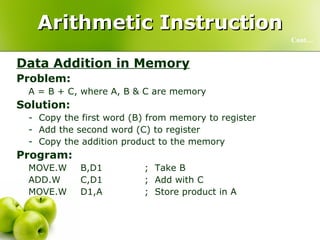

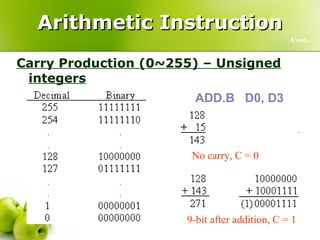

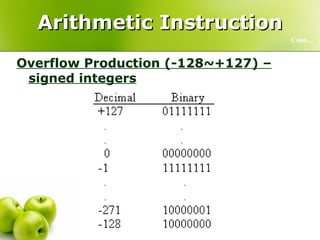

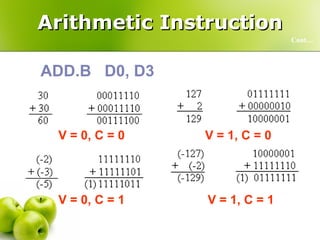

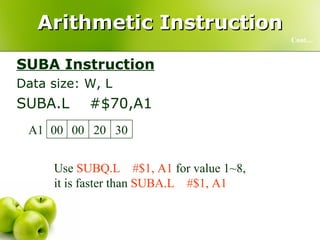

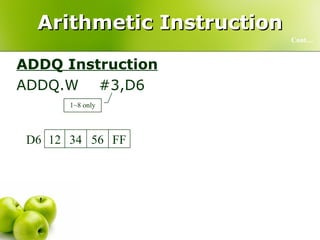

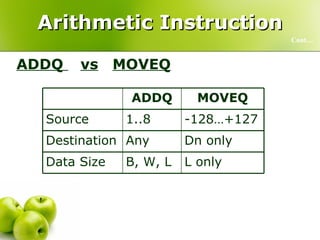

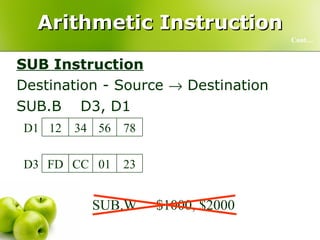

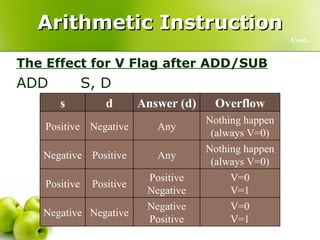

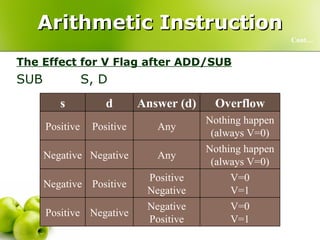

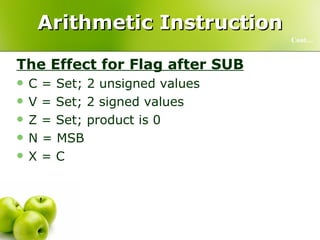

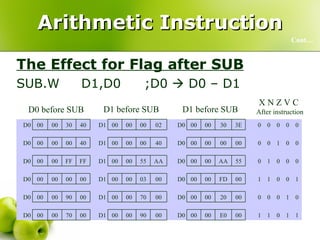

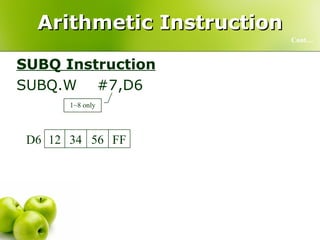

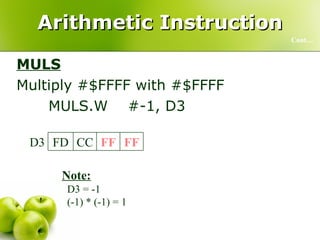

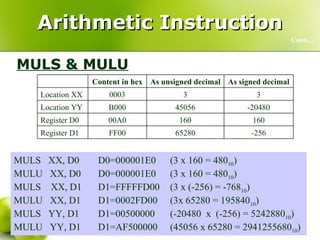

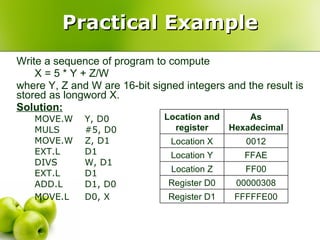

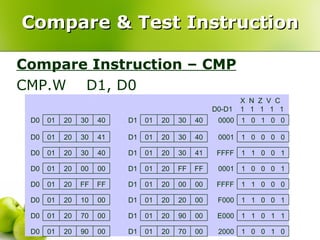

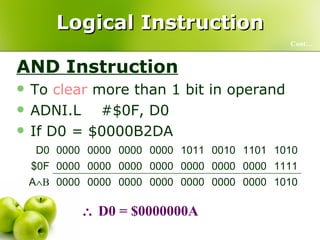

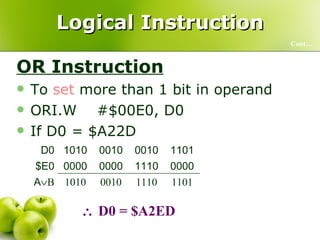

The document provides an introduction to the 68k microprocessor instruction set. It discusses the different types of instructions including data transfer, arithmetic, logical, and bit manipulation instructions. It describes the various addressing modes used by the 68k including register direct, absolute, PC relative, register indirect, and immediate addressing. Examples are given of instructions like MOVE, ADD, SUB, and MUL using different addressing modes and data sizes. The operation of the instruction cycle is explained, showing the fetch, decode, and execute phases for each instruction.