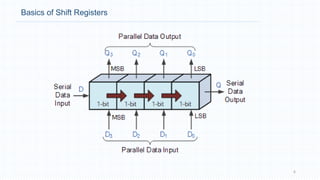

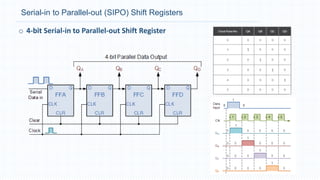

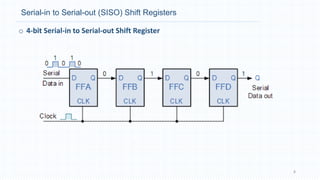

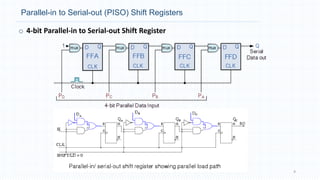

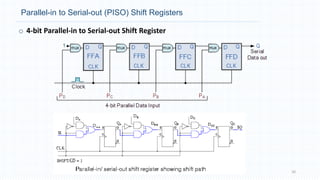

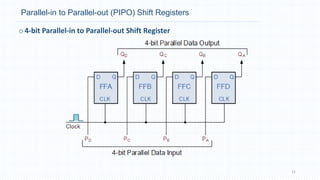

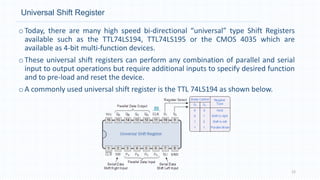

This document provides an overview of shift registers. It defines what a shift register is and discusses the basics, including that shift registers consist of flip-flops connected in a serial chain to store and transfer binary data. It describes the four main modes of operation for shift registers: serial-in parallel-out (SIPO), serial-in serial-out (SISO), parallel-in serial-out (PISO), and parallel-in parallel-out (PIPO). Diagrams are provided to illustrate examples of each type of shift register. The document concludes by mentioning universal shift registers, which can perform any input-output combination but require additional control inputs.