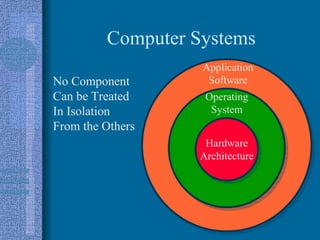

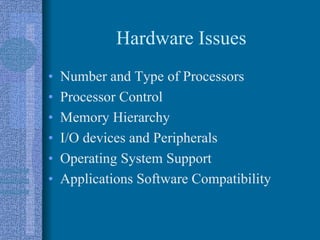

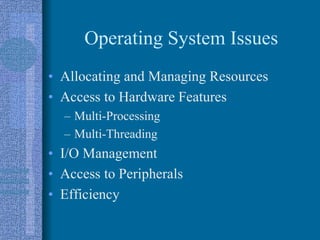

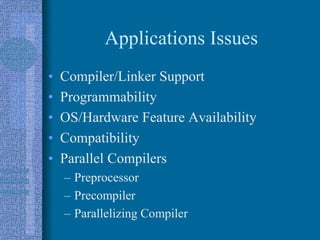

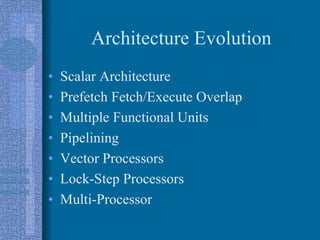

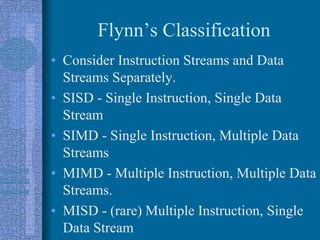

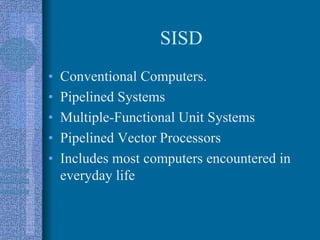

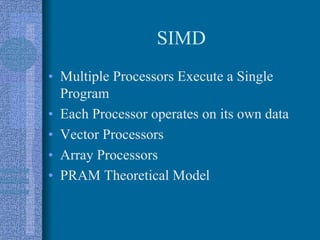

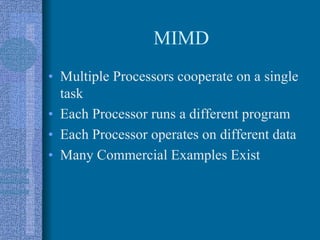

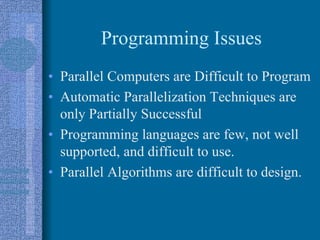

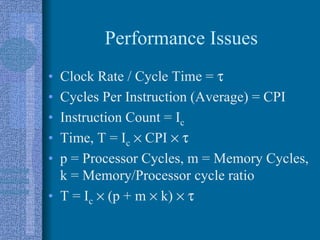

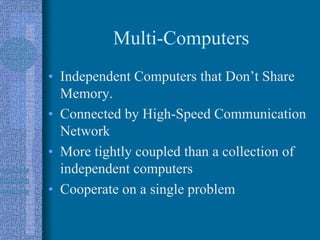

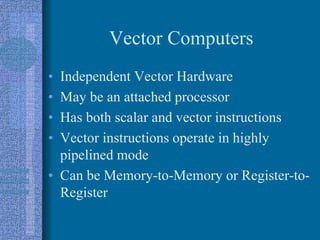

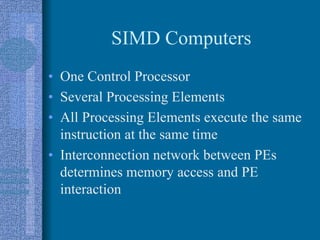

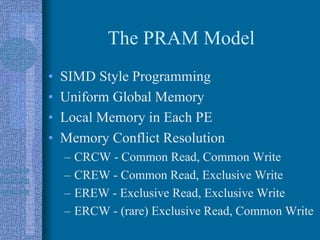

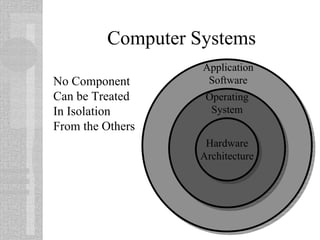

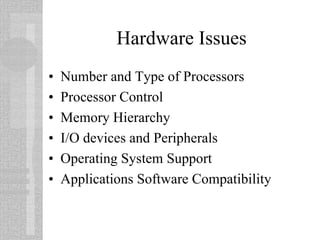

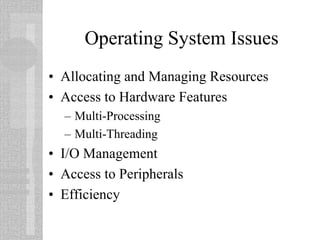

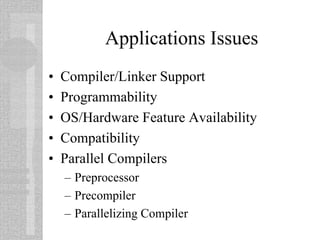

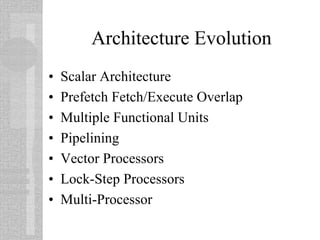

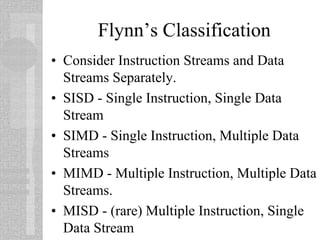

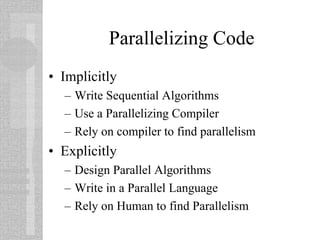

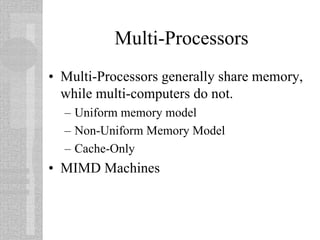

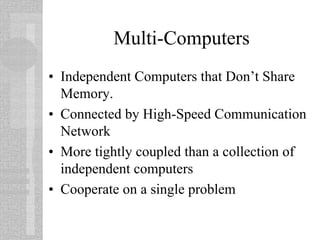

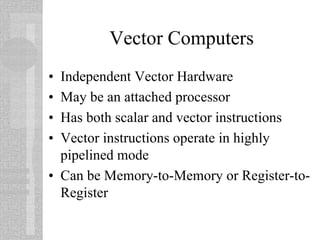

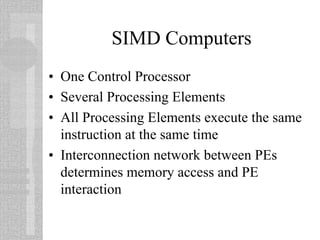

This document discusses the architecture of parallel computers. It covers hardware issues like the number and type of processors, memory hierarchy, and I/O devices. It also discusses operating system issues in managing resources and supporting hardware features. Programming issues are discussed, like difficulty in programming parallel computers. Flynn's classification of computer architectures is presented, including SISD, SIMD, MIMD, and MISD models. Different types of parallel computers are described such as multi-processors, multi-computers, vector computers, and SIMD computers.