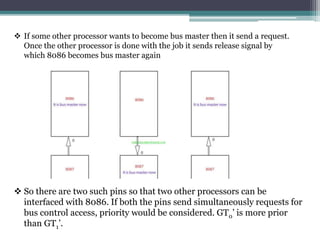

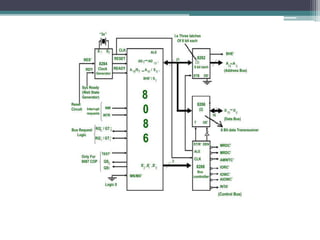

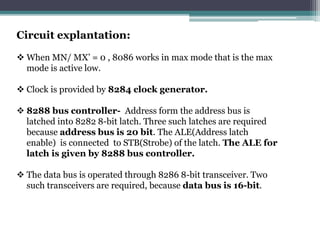

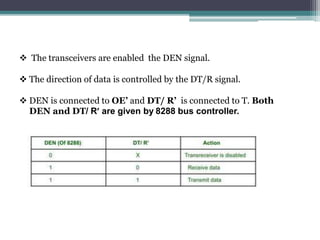

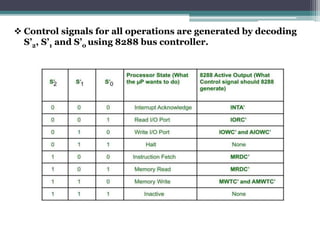

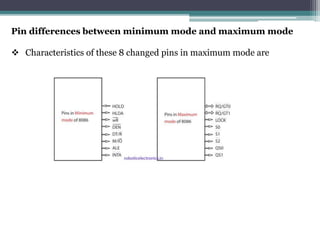

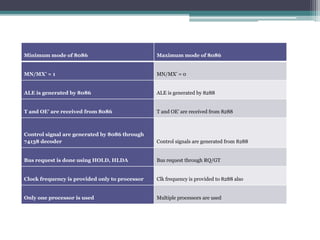

The document discusses the maximum mode of the 8086 microprocessor. In maximum mode, the 8086 is interfaced with other processors like the 8087 to boost performance through multiprocessing. The 8086 acts as the bus master and passes control to other processors via request pins. It uses an 8288 bus controller to generate control signals and latch addresses and data from the bus. Interfacing additional processors allows for floating point coprocessing and increased efficiency. The maximum mode has a more complex circuit than the minimum mode but enables multiprocessing capabilities.