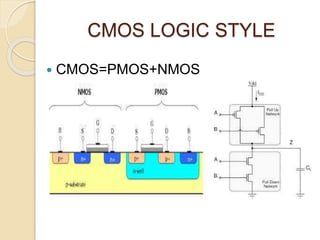

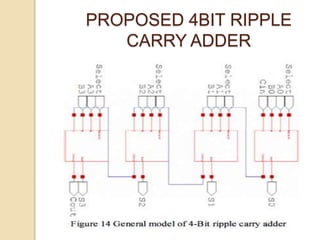

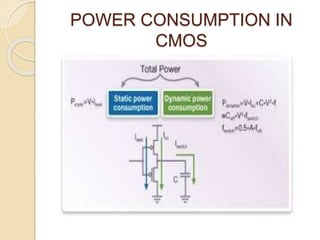

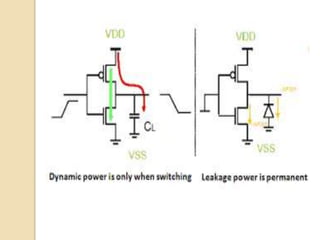

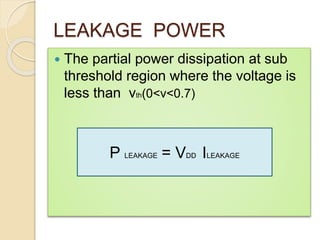

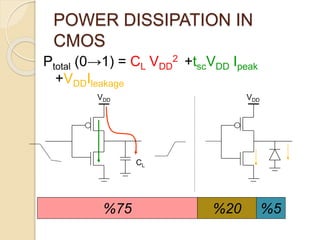

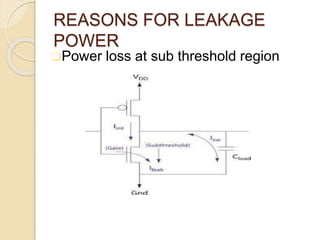

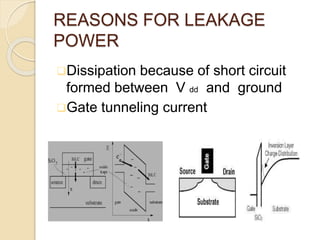

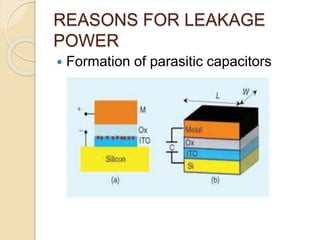

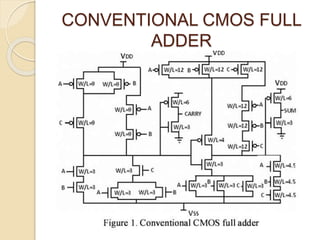

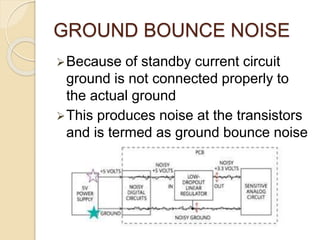

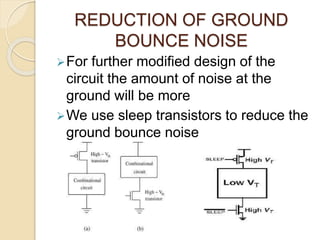

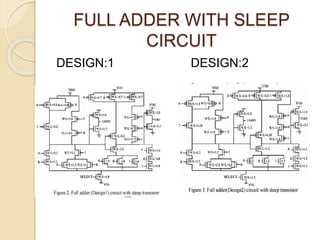

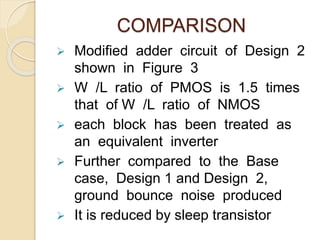

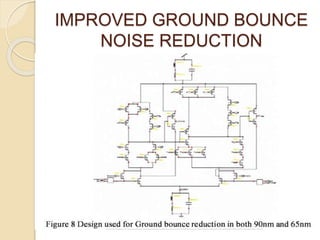

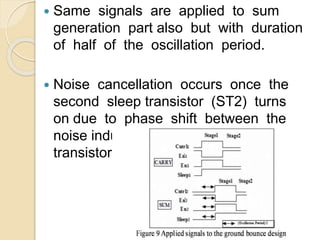

This document describes a proposed 4-bit CMOS full adder design with techniques to reduce leakage power and ground bounce noise. It introduces sleep transistors to improve upon conventional CMOS full adder designs. Simulation results show the modified design with sleep transistors reduces both standby leakage current and ground bounce noise compared to baseline designs without sleep transistors.