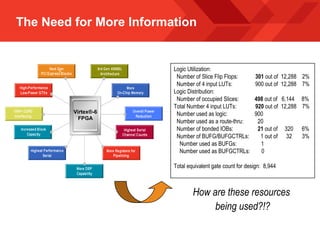

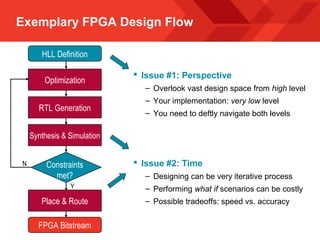

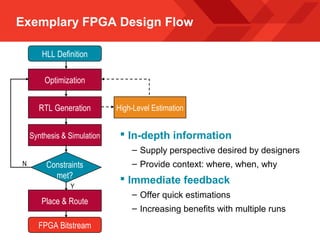

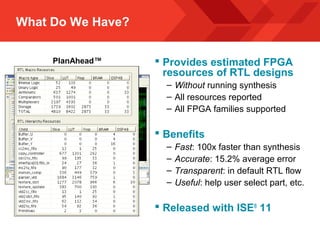

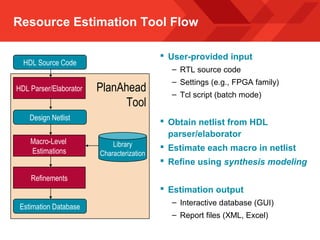

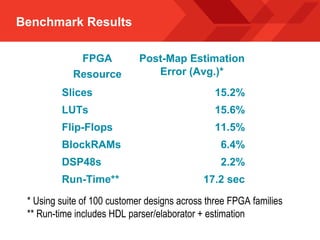

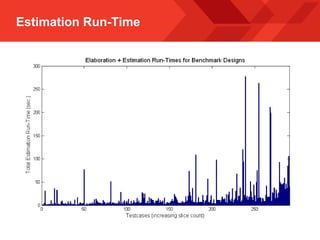

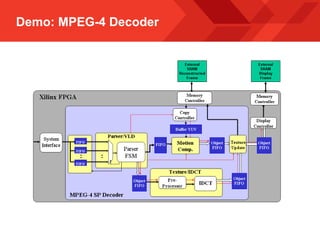

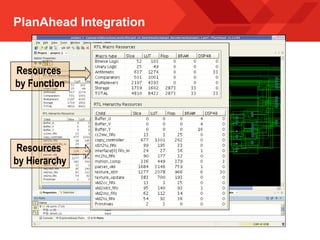

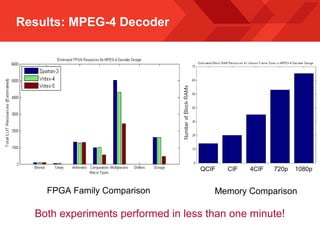

This document discusses a fast FPGA resource estimation tool that provides estimated resource usage for RTL designs without running full synthesis. It is on average 15.2% accurate and 100x faster than synthesis. The tool outputs detailed resource estimates that help designers quickly explore design space and optimize their implementations early in the design flow. A demo of the tool estimating resources for an MPEG-4 decoder design is also shown.