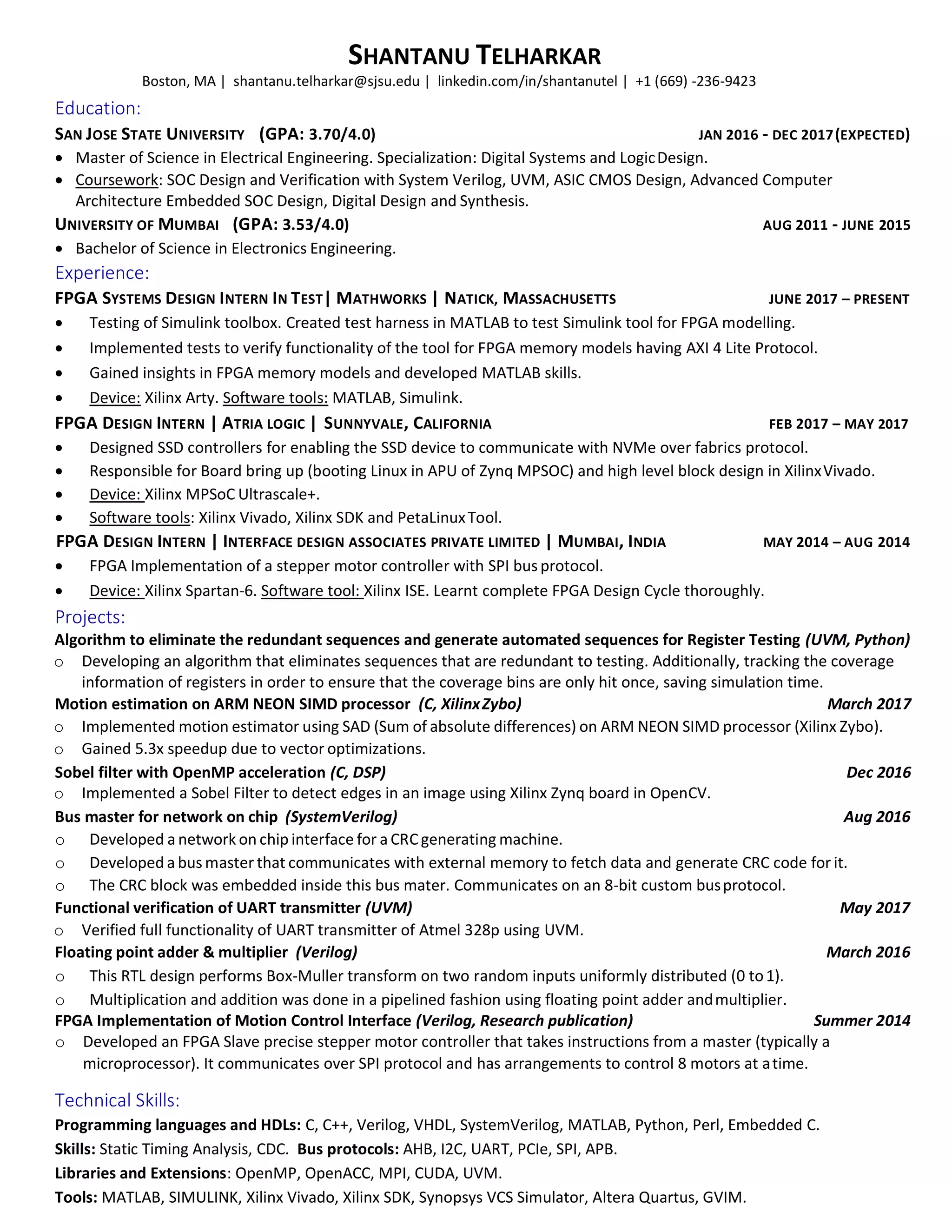

Shantanu Telharkar is pursuing a Master of Science in Electrical Engineering from San Jose State University with a specialization in digital systems and logic design. He has relevant experience as an FPGA systems design intern at MathWorks and as an FPGA design intern at Atria Logic and Interface Design Associates Private Limited. His technical skills include programming languages like C, C++, Verilog, VHDL, and SystemVerilog as well as tools like Xilinx Vivado, MATLAB, and SIMULINK.