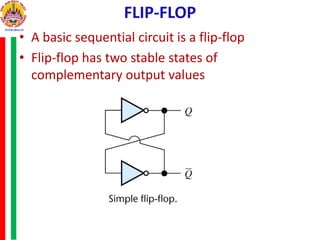

1. A flip-flop is a basic element of sequential circuits that has two stable states and whose output depends on both the current input and its previous state.

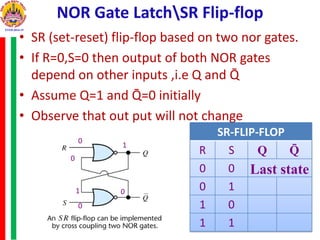

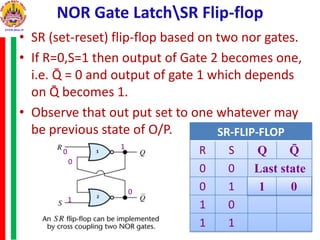

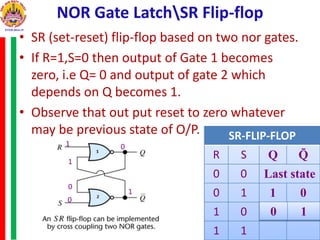

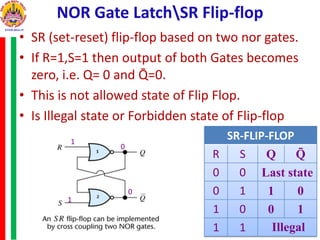

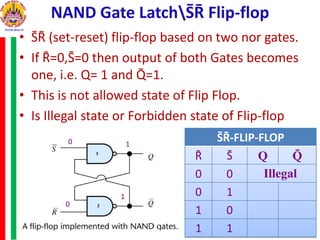

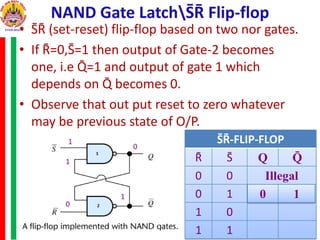

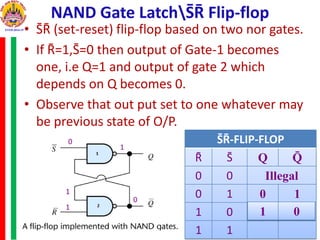

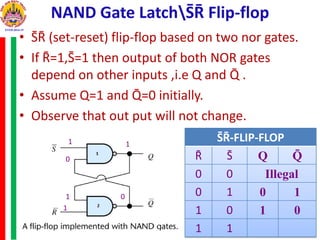

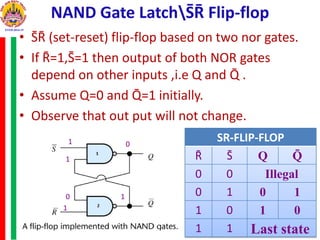

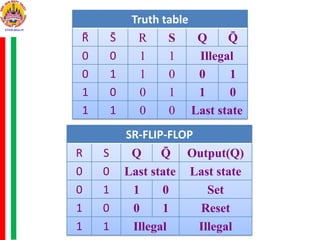

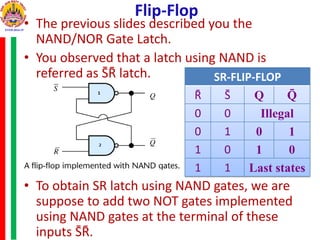

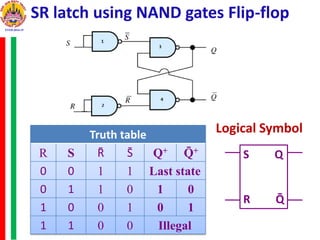

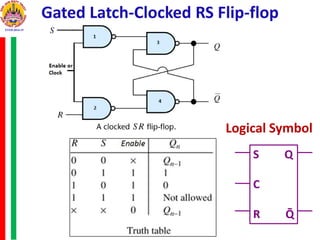

2. An SR flip-flop can be constructed using two NOR gates, with states that are set by a high S input and reset by a high R input.

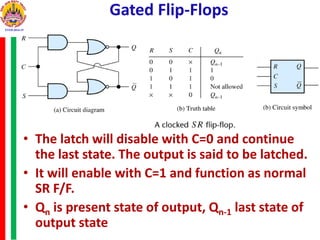

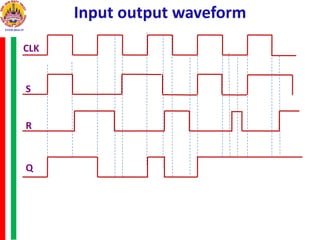

3. Gated flip-flops only change state in response to changes at the clock input, allowing the circuit response to be controlled at specific times.