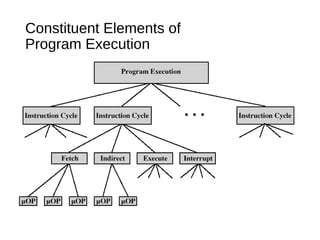

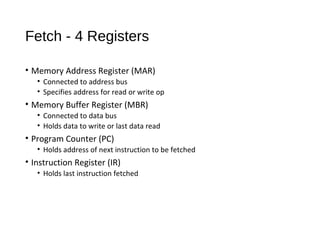

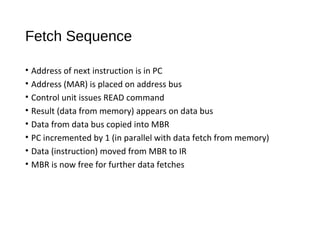

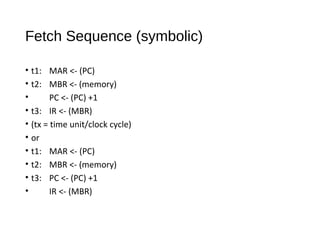

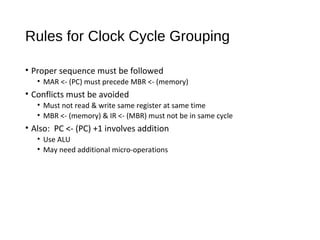

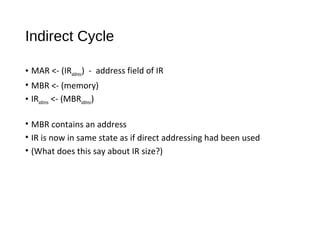

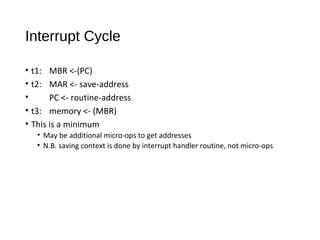

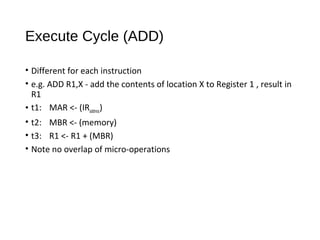

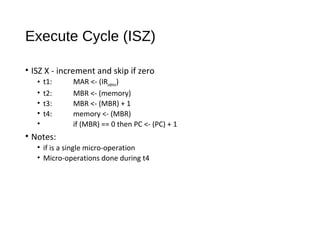

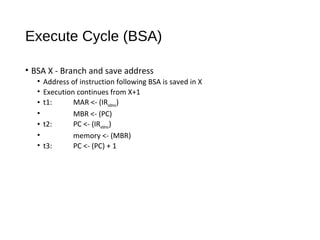

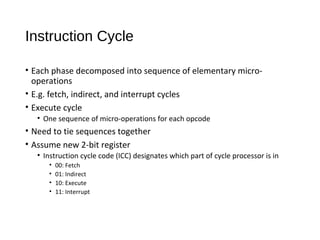

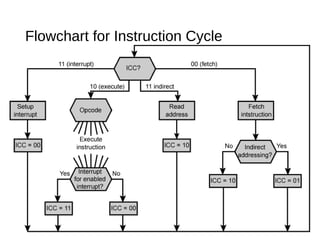

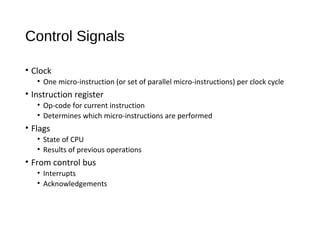

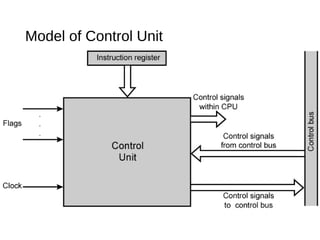

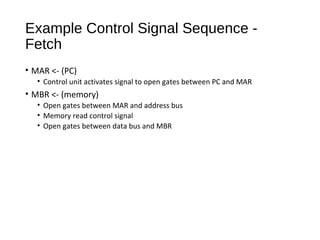

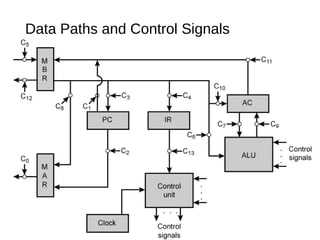

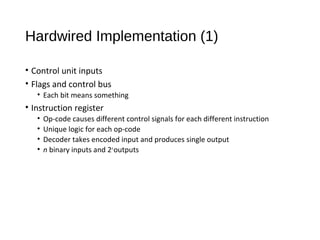

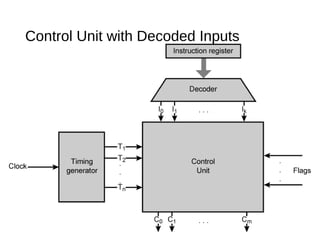

The document outlines the operation of a control unit in a computer, focusing on the fetch/execute cycle and its associated micro-operations. It details the processes involved in executing instructions, including fetching, indirect addressing, and interrupts, as well as the control signals that dictate the sequencing and execution of these operations. The discussion also highlights the challenges of hardwired control unit designs and the necessity for adaptable systems to accommodate new instructions.