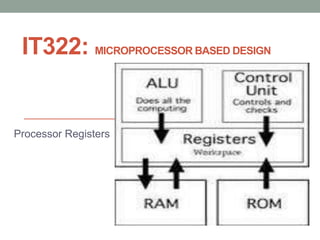

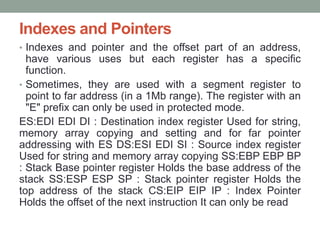

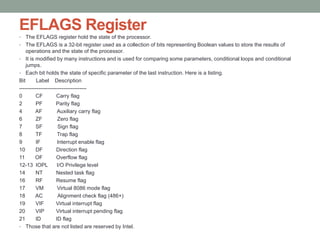

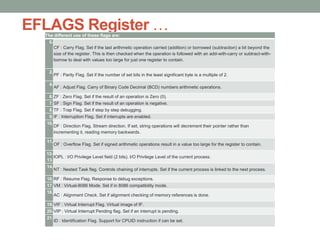

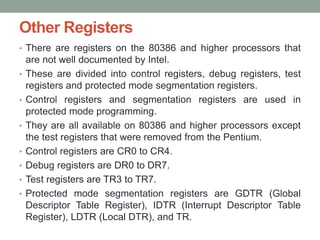

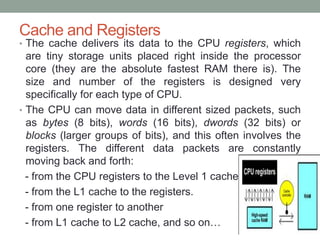

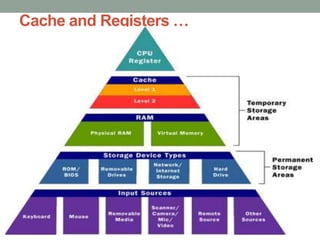

This document discusses processor registers and cache memory. It provides details on the various registers available on x86 processors including general purpose registers, segment registers, index/pointer registers, and other special purpose registers. It describes the main functions and uses of each register. The document also discusses how the cache works with registers to improve processor performance by keeping frequently used data and instructions close to the CPU in small amounts of fast memory.