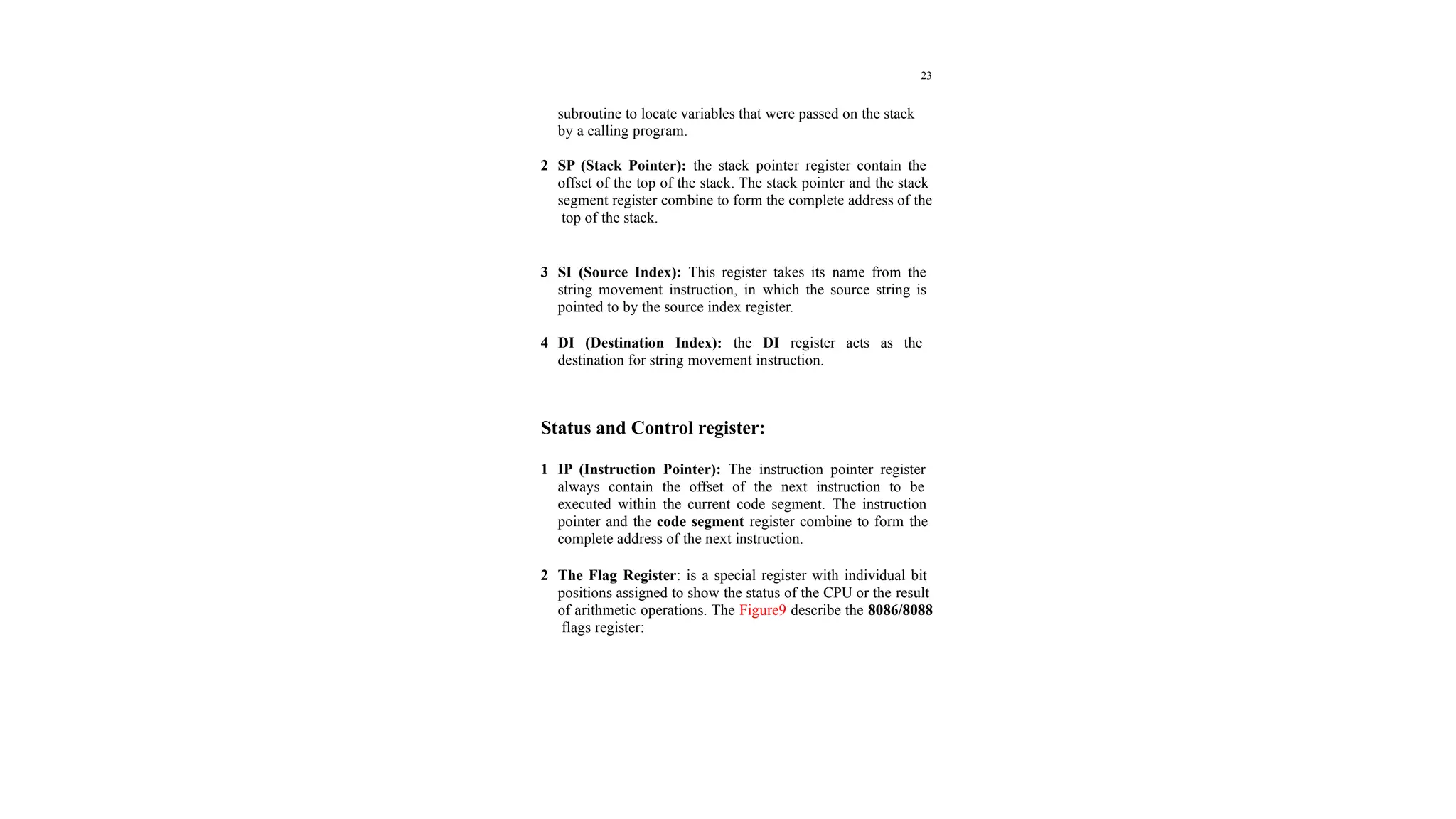

The document discusses memory segmentation and addressing in a computing context, particularly focusing on the 8086 processor architecture. It explains how segment registers are used to reference memory locations using segment and offset notations, and describes various types of registers, including general purpose, segment, index, and status/control registers. The document also outlines the attributes and roles of these registers in executing instructions and managing data within the CPU.