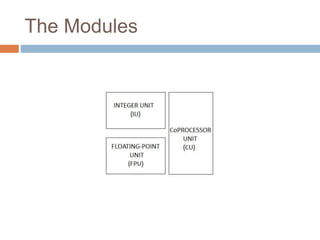

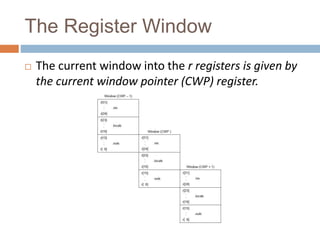

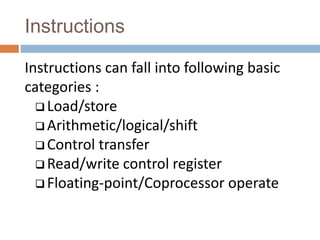

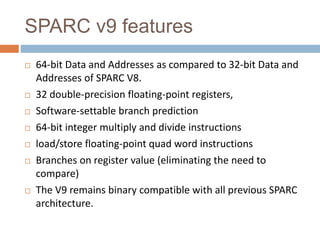

The document discusses the SPARC architecture, which was developed by Sun Microsystems in the 1980s as a RISC-based architecture. It outlines the design goals of being scalable and optimizable for compilers. The key components discussed are the integer unit, register window system, floating point unit, and optional coprocessor. The document provides a brief history of revisions to SPARC and describes features of the SPARC V9 64-bit extension such as larger registers and new instructions.