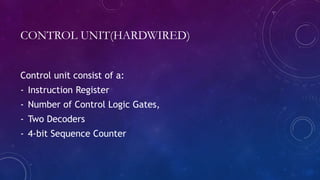

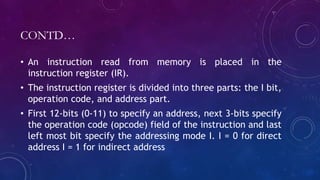

The control unit generates relevant timing and control signals to coordinate all operations in the computer. It directs the entire system to carry out instructions by communicating with the ALU and memory. Control units are implemented with either a hardwired or microprogrammed design. A hardwired control unit uses logic circuits to generate signals but is complex and difficult to modify. It works fast but changes require rewiring. A microprogrammed control unit uses a microprogram to generate signals and is easier to modify but slower.