Vlsi 2016 17--- m.tech-9581464142

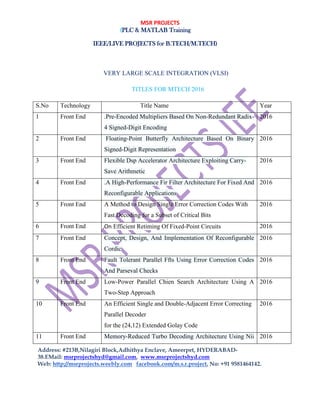

- 1. MSR PROJECTS (PLC & MATLAB Training IEEE/LIVE PROJECTS for B.TECH/M.TECH) Address: #213B,Nilagiri Block,Adhithya Enclave, Ameerpet, HYDERABAD- 38.EMail: msrprojectshyd@gmail.com, www.msrprojectshyd.com Web: http://msrprojects.weebly.com facebook.com/m.s.r.project, No: +91 9581464142. VERY LARGE SCALE INTEGRATION (VLSI) TITLES FOR MTECH 2016 S.No Technology Title Name Year 1 Front End .Pre-Encoded Multipliers Based On Non-Redundant Radix- 4 Signed-Digit Encoding 2016 2 Front End Floating-Point Butterfly Architecture Based On Binary Signed-Digit Representation 2016 3 Front End Flexible Dsp Accelerator Architecture Exploiting Carry- Save Arithmetic 2016 4 Front End .A High-Performance Fir Filter Architecture For Fixed And Reconfigurable Applications 2016 5 Front End A Method to Design Single Error Correction Codes With Fast Decoding for a Subset of Critical Bits 2016 6 Front End On Efficient Retiming Of Fixed-Point Circuits 2016 7 Front End Concept, Design, And Implementation Of Reconfigurable Cordic 2016 8 Front End Fault Tolerant Parallel Ffts Using Error Correction Codes And Parseval Checks 2016 9 Front End Low-Power Parallel Chien Search Architecture Using A Two-Step Approach 2016 10 Front End An Efficient Single and Double-Adjacent Error Correcting Parallel Decoder for the (24,12) Extended Golay Code 2016 11 Front End Memory-Reduced Turbo Decoding Architecture Using Nii 2016

- 2. MSR PROJECTS (PLC & MATLAB Training IEEE/LIVE PROJECTS for B.TECH/M.TECH) Address: #213B,Nilagiri Block,Adhithya Enclave, Ameerpet, HYDERABAD- 38.EMail: msrprojectshyd@gmail.com, www.msrprojectshyd.com Web: http://msrprojects.weebly.com facebook.com/m.s.r.project, No: +91 9581464142. Metric Compression 12 Front End Design for Testability of Sleep Convention Logic 2016 13 Front End A Novel Coding Scheme For Secure Communications In Distributed Rfid Systems 2016 14 Front End A High Throughput List Decoder Architecture for Polar Codes 2016 15 Front End A Modified Partial Product Generator For Redundant Binary Multipliers 2016 16 Front End A Cellular Network Architecture With Polynomial Weight Functions 2016 17 Front End A Normal I/O Order Radix-2 Fft Architecture To Process Twin Data Streams For Mimo 2016 18 Front End High Speed Hybrid Double Multiplication Architectures Using New Serial-Out Bit- Level Mastrovito Multipliers 2016 19 Front End Low-Cost High-Performance Vlsi Architecture For Montgomery Modular Multiplication 2016 20 Front End A High-Speed FPGA Implementation of an RSD-Based ECC Processor 2016 21 Front End VLSI Design for Convolutive Blind Source Separation 2016 22 Front End High-Speedand Energy-Efficient Carry Skip Adder Operating Under A Wide Rangeof Supply Voltage Levels 2016 23 Front End Input-Based Dynamic Reconfiguration Of Approximate Arithmetic Units For Video Encoding 2016

- 3. MSR PROJECTS (PLC & MATLAB Training IEEE/LIVE PROJECTS for B.TECH/M.TECH) Address: #213B,Nilagiri Block,Adhithya Enclave, Ameerpet, HYDERABAD- 38.EMail: msrprojectshyd@gmail.com, www.msrprojectshyd.com Web: http://msrprojects.weebly.com facebook.com/m.s.r.project, No: +91 9581464142. 24 Front End Hardware And Energy-Efficient Stochastic Lu Decomposition Scheme For Mimo Receivers 2016 25 Front End Hybrid Lut/Multiplexer Fpga Logic Architectures 2016 26 Front End Arithmetic algorithms for extended precision using floating-point expansions 2016 27 Back End A 28 nm Configurable Memory (TCAM/BCAM/SRAM) Using Push-Rule 6T Bit Cell Enabling Logic-in-Memory 2016 28 Back End Dual Use Of Power Lines For Design-For-Testability—A Cmos Receiver Design 2016 29 Back End Low-Power Variation-Tolerant Nonvolatile Lookup Table Design 2016 30 Back End Pns-Fcr: Flexible Charge Recycling Dynamic Circuit Technique For Low-Power Microprocessors 2016 31 Back End A Low Power Trainable Neuromorphic Integrated Circuit That Is Tolerant To Device Mismatch 2016 32 Back End A 55-Ghz-Bandwidth Track-And-Hold Amplifier In 28- Nm Low-Power Cmos 2016 33 Back End A Low-Power Incremental Delta–Sigma Adc For Cmos Image Sensors 2016 34 Back End Low-Power Ask Detector For Low Modulation Indexes And Rail-To-Rail Input Range. 2016

- 4. MSR PROJECTS (PLC & MATLAB Training IEEE/LIVE PROJECTS for B.TECH/M.TECH) Address: #213B,Nilagiri Block,Adhithya Enclave, Ameerpet, HYDERABAD- 38.EMail: msrprojectshyd@gmail.com, www.msrprojectshyd.com Web: http://msrprojects.weebly.com facebook.com/m.s.r.project, No: +91 9581464142. 35 Back End A Low-Power Robust Easily Cascaded Pentamtj-Based Combinational And Sequential Circuits 2016 36 Front End Improved Synthesis of Reversible Sequential Circuits 2016 37 Front End Squaring in Reversible Logic using Zero Garbage and Reduced Ancillary inputs 2016 38 Front End Low-Quantum Cost Circuit Constructions for Adder and Symmetric Boolean Functions 2016 39 Front End Design of Register File using Reversible Logic 2016 40 frontend High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2016 41 Front end Design Of Low Power, High Performance 2-4 And 4-16 Mixed-Logic Line Decoders 2016 42 Front end Design Of High Speed Multiplier Using Modified Booth Algorithm With Hybrid Carry Look-Ahead Adder 2016 43 Front end Energy-Aware Scheduling of FIR Filter Structures using a Timed Automata Model 2016 44 Front end An Improved Design of a Reversible Fault Tolerant LUT-Based FPGA 2016 45 Front end Design of high speed multiplier using Modified Booth Algorithm with hybrid carry look-ahead adder 2016 46 Front end Re-writing HDL Descriptions for Line-aware Synthesis of Reversible Circuits 2016 47 Front end A Parallel Decimal Multiplier Using Hybrid Binary Coded Decimal (BCD) Codes 2016

- 5. MSR PROJECTS (PLC & MATLAB Training IEEE/LIVE PROJECTS for B.TECH/M.TECH) Address: #213B,Nilagiri Block,Adhithya Enclave, Ameerpet, HYDERABAD- 38.EMail: msrprojectshyd@gmail.com, www.msrprojectshyd.com Web: http://msrprojects.weebly.com facebook.com/m.s.r.project, No: +91 9581464142. 48 Front end Floating-Point Butterfly Architecture Based on Binary Signed-Digit Representation 2016