BULK IEEE PROJECTS IN VLSI ,BULK IEEE PROJECTS, IEEE 2015-16 VLSI PROJECTS IN CHENNAI, 2015-16 VLSI PROJECTS IN PONDICHERRY,BULK IEEE PROJECTS FOR VLSI ,IEEE MATLAB PROJECTS IN PONDICHERRY,VLSI PROJECTS IN PONDICHERRY,

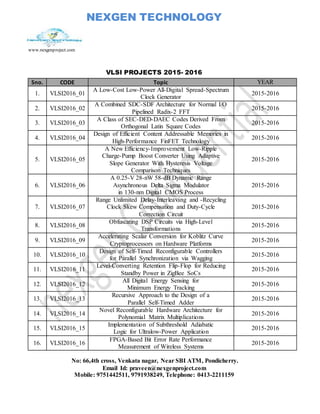

- 1. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 VLSI PROJECTS 2015- 2016 Sno. CODE Topic YEAR 1. VLSI2016_01 A Low-Cost Low-Power All-Digital Spread-Spectrum Clock Generator 2015-2016 2. VLSI2016_02 A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix-2 FFT 2015-2016 3. VLSI2016_03 A Class of SEC-DED-DAEC Codes Derived From Orthogonal Latin Square Codes 2015-2016 4. VLSI2016_04 Design of Efficient Content Addressable Memories in High-Performance FinFET Technology 2015-2016 5. VLSI2016_05 A New Efficiency-Improvement Low-Ripple Charge-Pump Boost Converter Using Adaptive Slope Generator With Hysteresis Voltage Comparison Techniques 2015-2016 6. VLSI2016_06 A 0.25-V 28-nW 58-dB Dynamic Range Asynchronous Delta Sigma Modulator in 130-nm Digital CMOS Process 2015-2016 7. VLSI2016_07 Range Unlimited Delay-Interleaving and -Recycling Clock Skew Compensation and Duty-Cycle Correction Circuit 2015-2016 8. VLSI2016_08 Obfuscating DSP Circuits via High-Level Transformations 2015-2016 9. VLSI2016_09 Accelerating Scalar Conversion for Koblitz Curve Cryptoprocessors on Hardware Platforms 2015-2016 10. VLSI2016_10 Design of Self-Timed Reconfigurable Controllers for Parallel Synchronization via Wagging 2015-2016 11. VLSI2016_11 Level-Converting Retention Flip-Flop for Reducing Standby Power in ZigBee SoCs 2015-2016 12. VLSI2016_12 All Digital Energy Sensing for Minimum Energy Tracking 2015-2016 13. VLSI2016_13 Recursive Approach to the Design of a Parallel Self-Timed Adder 2015-2016 14. VLSI2016_14 Novel Reconfigurable Hardware Architecture for Polynomial Matrix Multiplications 2015-2016 15. VLSI2016_15 Implementation of Subthreshold Adiabatic Logic for Ultralow-Power Application 2015-2016 16. VLSI2016_16 FPGA-Based Bit Error Rate Performance Measurement of Wireless Systems 2015-2016

- 2. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 17. VLSI2016_17 Algorithm and Architecture Design of the H.265/HEVC Intra Encoder 2015-2016 18. VLSI2016_18 Pre-Encoded Multipliers Based on Non-Redundant Radix-4 Signed-Digit Encoding 2015-2016 19. VLSI2016_19 A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications 2015-2016 20. VLSI2016_20 A Novel Photosensitive Tunneling Transistor for Near-Infrared Sensing Applications: Design, Modeling, and Simulation 2015-2016 21. VLSI2016_21 High-Throughput LDPC-Decoder Architecture Using Efficient Comparison Techniques & Dynamic Multi-Frame Processing Schedule 2015-2016 22. VLSI2016_22 A New Parallel VLSI Architecture for Real-time Electrical Capacitance Tomography 2015-2016 23. VLSI2016_23 Graph-Based Transistor Network Generation Method for Supergate Design 2015-2016 24. VLSI2016_24 A Relative Imaging CMOS Image Sensor for High Dynamic Range and High Frame-Rate Machine Vision Imaging Applications 2015-2016 25. VLSI2016_25 Low-Cost High-Performance VLSI Architecture for Montgomery Modular Multiplication 2015-2016 26. VLSI2016_26 Fully Pipelined Low-Cost and High-Quality Color Demosaicking VLSI Design for Real-Time Video Applications 2015-2016 27. VLSI2016_27 A Novel Area-Efficient VLSI Architecture for Recursion Computation in LTE Turbo Decoders 2015-2016 28. VLSI2016_28 Comparative Performance Analysis of the Dielectrically Modulated FullGate and Short-Gate Tunnel FET-Based Biosensors 2015-2016 29. VLSI2016_29 An Efficient Constant Multiplier Architecture Based on Vertical-Horizontal Binary Common Sub-expression Elimination Algorithm for Reconfigurable FIR Filter Synthesis 2015-2016 30. VLSI2016_30 VLSI-Assisted Nonrigid Registration Using Modified Demons Algorithm 2015-2016 31. VLSI2016_31 Fine-Grained Access Management in Reconfigurable Scan Networks 2015-2016

- 3. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 32. VLSI2016_32 A High-Throughput VLSI Architecture for Hard and Soft SC-FDMA MIMO Detectors 2015-2016 33. VLSI2016_33 Partially Parallel Encoder Architecture for Long Polar Codes 2015-2016 34. VLSI2016_34 Novel Block-Formulation and Area-Delay-Efficient Reconfigurable Interpolation Filter Architecture for Multi-Standard SDR Applications 2015-2016 35. VLSI2016_35 One Minimum Only Trellis Decoder for Non-Binary Low-Density Parity-Check Codes 2015-2016 36. VLSI2016_36 A Low-Cost Hardware Architecture for Illumination Adjustment in Real-Time Applications 2015-2016 37. VLSI2016_37 A 2.5-Gb/s DLL-Based Burst-Mode Clock and Data Recovery Circuit With 4× Oversampling 2015-2016 38. VLSI2016_38 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015-2016 39. VLSI2016_39 Reverse Converter Design via Parallel-Prefix Adders: Novel Components, Methodology, and Implementations 2015-2016 40. VLSI2016_40 Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications 2015-2016 41 VLSI2016_41 A Fast-Acquisition All-Digital Delay-Locked Loop Using a Starting-Bit Prediction Algorithm for the Successive-Approximation Register 2015-2016 42 VLSI2016_42 A Fully Digital Front-End Architecture for ECG Acquisition System With 0.5 V Supply 2015-2016 43 VLSI2016_43 A Low-Power Robust Easily CascadedPentaMTJ- Based Combinational and Sequential Circuits 2015-2016 44 VLSI2016_44 A Mixed-Decimation MDF Architecture for Radix- 2k Parallel FFT 2015-2016 45 VLSI2016_45 A SUC-Based Full-Binary 6-bit 3.1-GS/s 17.7-Mw Current-Steering DAC in 0.038 mm2 2015-2016 46 VLSI2016_46 Argo: A Real-Time Network-on-Chip Architecture With an Efficient GALS Implementation 2015-2016 47 VLSI2016_47 Design and Low-Complexity Implementation of Matrix–Vector Multiplier for Iterative Methods in Communication Systems 2015-2016 48 VLSI2016_48 Energy and Area Efficient Three-Input XOR/XN 2015-2016

- 4. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 ORs With Systematic Cell Design Methodology 49 VLSI2016_49 Fault Tolerant Parallel FFTs Using Error Correction Codes and Parseval Checks 2015-2016 50 VLSI2016_50 Graph-Based Transistor Network Generation Method for Supergate Design 2015-2016 51 VLSI2016_51 High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2015-2016 52 VLSI2016_52 High-Throughput Power-Efficient VLSI Architecture of Fractional Motion Estimation for Ultra-HD HEVC Video Encoding 2015-2016 53 VLSI2016_53 A Spread Spectrum Clock Generator Using a Programmable Linear Frequency Modulator for Multipurpose Electronic Devices 2015-2016 54 VLSI2016_54 Floating-Point Butterfly Architecture Based on Binary Signed-Digit Representation 2015-2016 55 VLSI2016_55 Further Desensitized FIR Halfband Filters 2015-2016 56 VLSI2016_56 A Modified Partial Product Generator for Redundant Binary Multipliers 2015-2016 57 VLSI2016_57 Implementation of Arithmetic Operations with Time- free Spiking Neural P Systems 2015-2016 58 VLSI2016_58 A Clock and Data Recovery Circuit With Programmable Multi-Level Phase Detector Characteristics and a Built-in Jitter Monitor 2015-2016 59 VLSI2016_59 Unfaithful Glitch Propagation in Existing Binary Circuit Models 2015-2016 60 VLSI2016_60 Early Skip Mode Decision for HEVC Encoder With Emphasis on Coding Quality 2015-2016 61 VLSI2016_61 Two-Step Optimization Approach for the Design of Multiplierless Linear-Phase FIR Filters 2015-2016 62 VLSI2016_62 Energy Consumption of VLSI Decoders 2015-2016 63 VLSI2016_63 Timing Error Tolerance in Small Core Designs for SoC Applications 2015-2016 64 VLSI2016_64 40-Gb/s 0.7-V 2:1 MUX and 1:2 DEMUX with Transformer-Coupled Technique for SerDes Interface 2015-2016 65 VLSI2016_65 Design and Analysis of Inexact Floating-Point Adders 2015-2016 66 VLSI2016_66 In-Field Test for Permanent Faults in FIFO Buffers of NoC Routers 2015-2016 67 VLSI2016_67 Low-Cost High-Performance VLSI Architecture for 2015-2016

- 5. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 Montgomery ModularMultiplication 68 VLSI2016_68 High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2015-2016 69 VLSI2016_69 Dual-Phase Tapped-Delay-Line Time-to-Digital Converter With On-the-Fly Calibration Implemented in 40 nm FPGA 2015-2016 70 VLSI2016_70 A Low Power and High Sensing Margin Non-Volatile Full Adder Using Racetrack Memory 2015-2016 71 VLSI2016_71 Signal Design for Multiple Antenna Systems With Spatial Multiplexing and Noncoherent Reception 2015-2016 72 VLSI2016_72 Synthesis of Genetic Clock with Combinational Biologic Circuits 2015-2016 73 VLSI2016_73 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015-2016 74 VLSI2016_74 Fault Tolerant Parallel Filters Based on Error Correction Codes 2015-2016 75 VLSI2016_75 Design and Analysis of Approximate Compressors for Multiplication 2015-2016 76 VLSI2016_76 Novel Design Algorithm for Low Complexity Programmable FIR Filters Based on Extended Double Base Number Systems 2015-2016 77 VLSI2016_77 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability 2015-2016 78 VLSI2016_78 Floating-Point Butterfly Architecture Based on Binary Signed-Digit Representation 2015-2016 79 VLSI2016_79 Implementation of Subthreshold Adiabatic Logic for Ultralow-Power Application 2015-2016 80 VLSI2016_80 Novel Block-Formulation and Area-Delay-Efficient Reconfigurable Interpolation Filter Architecture for Multi-Standard SDR Applications 2015-2016 81 VLSI2016_81 A High-Performance FIR Filter Architecture for Fixed and Reconfigurable Applications 2015-2016 82 VLSI2016_82 High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels 2015-2016 83 VLSI2016_83 Low-Power and Area-Efficient Shift Register Using Pulsed Latches 2015-2016 84 VLSI2016_84 Array-Based Approximate Arithmetic Computing: A 2015-2016

- 6. NEXGEN TECHNOLOGY www.nexgenproject.com No: 66,4th cross, Venkata nagar, Near SBI ATM, Pondicherry. Email Id: praveen@nexgenproject.com Mobile: 9751442511, 9791938249, Telephone: 0413-2211159 General Model and Applications to Multiplier and Squarer Design 85 VLSI2016_85 Recursive Approach to the Design of a Parallel Self- Timed Adder 2015-2016 86 VLSI2016_86 Further Desensitized FIR Half band Filters 2015-2016 87 VLSI2016_87 Design and Analysis of Inexact Floating-Point Adder 2015-2016 88 VLSI2016_88 Scalable Verification of a Generic End-Around-Carry Adder for Floating-Point Units by Coq 2015-2016 89 VLSI2016_89 An Efficient Constant Multiplier Architecture Based on Vertical-Horizontal Binary Common Sub-expression Elimination Algorithm for Reconfigurable FIR Filter Synthesis 2015-2016 90 VLSI2016_90 A Generalized Algorithm and Reconfigurable Architecture for Efficient and Scalable Orthogonal Approximation of DCT 2015-2016