New vlsi list 2015 only

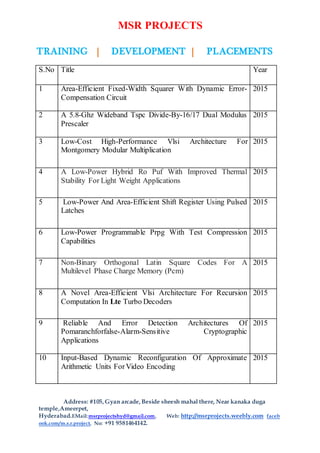

- 1. MSR PROJECTS TRAINING | DEVELOPMENT | PLACEMENTS Address: #105,Gyan arcade,Beside sheesh mahal there, Near kanaka duga temple,Ameerpet, Hyderabad.EMail:msrprojectshyd@gmail.com, Web: http://msrprojects.weebly.com faceb ook.com/m.s.r.project, No: +91 9581464142. S.No Title Year 1 Area-Efficient Fixed-Width Squarer With Dynamic Error- Compensation Circuit 2015 2 A 5.8-Ghz Wideband Tspc Divide-By-16/17 Dual Modulus Prescaler 2015 3 Low-Cost High-Performance Vlsi Architecture For Montgomery Modular Multiplication 2015 4 A Low-Power Hybrid Ro Puf With Improved Thermal Stability For Light Weight Applications 2015 5 Low-Power And Area-Efficient Shift Register Using Pulsed Latches 2015 6 Low-Power Programmable Prpg With Test Compression Capabilities 2015 7 Non-Binary Orthogonal Latin Square Codes For A Multilevel Phase Charge Memory (Pcm) 2015 8 A Novel Area-Efficient Vlsi Architecture For Recursion Computation In Lte Turbo Decoders 2015 9 Reliable And Error Detection Architectures Of Pomaranchforfalse-Alarm-Sensitive Cryptographic Applications 2015 10 Input-Based Dynamic Reconfiguration Of Approximate Arithmetic Units ForVideo Encoding 2015

- 2. MSR PROJECTS TRAINING | DEVELOPMENT | PLACEMENTS Address: #105,Gyan arcade,Beside sheesh mahal there, Near kanaka duga temple,Ameerpet, Hyderabad.EMail:msrprojectshyd@gmail.com, Web: http://msrprojects.weebly.com faceb ook.com/m.s.r.project, No: +91 9581464142. 11 A Generalized Algorithm And Reconfigurable Architectureforefficientandscalable Orthogonal Approximation Of Dct 2015 12 Energy And Area Efficient Three-Input Xor/Xnors With Systematic Cell Design Methodology 2015 13 Recursive Approach To The Design Of A Parallel Self- Timed Adder 2015 14 Fault Tolerant Parallel Ffts Using Error Correction Codes And Parseval Checks 2015 15 High Speed Fir Filter Designs Based On Booth Multipler 2015 16 Reliable And Error Detection Architectures Ofpomaranch For False-Alarm-Sensitive Cryptographic Applications 2015 17 A Generalized Algorithm And Reconfigurable Architecture For Efficient And Scalable Orthogonal Approximation Of Dct 2015 18 Methodology For Optimized Design Of Secure Differential Logic Gates For Dpa Resistant Circuits 2015 19 Reverse Converter Design Via Parallel-Prefix Adders: Novel Componentsmethodology, And Implementations 2015 20 A High-Performance Fir Filter Architecture For Fixed And Reconfigurable Applications 2015

- 3. MSR PROJECTS TRAINING | DEVELOPMENT | PLACEMENTS Address: #105,Gyan arcade,Beside sheesh mahal there, Near kanaka duga temple,Ameerpet, Hyderabad.EMail:msrprojectshyd@gmail.com, Web: http://msrprojects.weebly.com faceb ook.com/m.s.r.project, No: +91 9581464142. 21 An Area-Efficient Relaxed Half-Stochastic Decoding Architecture For Nonbinary Ldpc Codes 2015 22 High-Throughput Finite Field Multipliers Using Redundant Basis For Fpga And Asic Implementations 2015 23 Multifunction Residue Architectures For Cryptography 2015 24 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2015 25 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based On Multilevel Conditional Probability 2015 26 Fast Sign Detection Algorithm For The Rns Moduli Set {2n+1 − 1, 2n − 1, 2n} 2015 27 Variable Latency Speculative Han-Carlson Adder 2015 28 High-Speed And Energy-Efficient Carry Skip Adder Operating Under A Wide Range Of Supply Voltage Levels 2015 29 Efficient Coding Schemes ForFault-Tolerant Parallel Filters 2015 30 Trade-Offs ForThreshold Implementations Illustrated On Aes 2015 31 Novel Design Algorithm For Low Complexity Programmable Fir Filters Based On Extended Double 2015

- 4. MSR PROJECTS TRAINING | DEVELOPMENT | PLACEMENTS Address: #105,Gyan arcade,Beside sheesh mahal there, Near kanaka duga temple,Ameerpet, Hyderabad.EMail:msrprojectshyd@gmail.com, Web: http://msrprojects.weebly.com faceb ook.com/m.s.r.project, No: +91 9581464142. Base Number System 32 Fully Reused Vlsi Architecture Of Fm0/Manchester Encoding Using Sols Technique ForDsrc Applications 2015 33 Result-Biased Distributed-Arithmetic-Based Filter Architectures For Approximately Computing The Dwt 2015 34 Design And Analysis Of Approximate Compressors For Multiplication 2015 35 Single-Supply 3t Gain-Cell For Low-Voltage Low-Power Applications 2015 36 A Novel Approach To Realize Built-In-Self-Test(Bist) Enabled Uart Using Vhdl 2015 37 An Optimized Modified Booth RecoderFor Efficient Design Of The Add-Multiply Operator 2015