Report

Share

Download to read offline

Recommended

Recommended

More Related Content

Similar to Module-5A.pdf

Similar to Module-5A.pdf (20)

IRJET- Design And VLSI Verification of DDR SDRAM Controller Using VHDL

IRJET- Design And VLSI Verification of DDR SDRAM Controller Using VHDL

memeoryorganization PPT for organization of memories

memeoryorganization PPT for organization of memories

A Comparitive Analysis of Improved 6t Sram Cell With Different Sram Cell

A Comparitive Analysis of Improved 6t Sram Cell With Different Sram Cell

More from 8885684828

More from 8885684828 (13)

Recently uploaded

Recently uploaded (20)

Basic Electronics for diploma students as per technical education Kerala Syll...

Basic Electronics for diploma students as per technical education Kerala Syll...

PE 459 LECTURE 2- natural gas basic concepts and properties

PE 459 LECTURE 2- natural gas basic concepts and properties

S1S2 B.Arch MGU - HOA1&2 Module 3 -Temple Architecture of Kerala.pptx

S1S2 B.Arch MGU - HOA1&2 Module 3 -Temple Architecture of Kerala.pptx

"Lesotho Leaps Forward: A Chronicle of Transformative Developments"

"Lesotho Leaps Forward: A Chronicle of Transformative Developments"

Digital Communication Essentials: DPCM, DM, and ADM .pptx

Digital Communication Essentials: DPCM, DM, and ADM .pptx

Standard vs Custom Battery Packs - Decoding the Power Play

Standard vs Custom Battery Packs - Decoding the Power Play

Linux Systems Programming: Inter Process Communication (IPC) using Pipes

Linux Systems Programming: Inter Process Communication (IPC) using Pipes

8086 Microprocessor Architecture: 16-bit microprocessor

8086 Microprocessor Architecture: 16-bit microprocessor

HOA1&2 - Module 3 - PREHISTORCI ARCHITECTURE OF KERALA.pptx

HOA1&2 - Module 3 - PREHISTORCI ARCHITECTURE OF KERALA.pptx

Electromagnetic relays used for power system .pptx

Electromagnetic relays used for power system .pptx

Unit 4_Part 1 CSE2001 Exception Handling and Function Template and Class Temp...

Unit 4_Part 1 CSE2001 Exception Handling and Function Template and Class Temp...

1_Introduction + EAM Vocabulary + how to navigate in EAM.pdf

1_Introduction + EAM Vocabulary + how to navigate in EAM.pdf

scipt v1.pptxcxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx...

scipt v1.pptxcxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx...

Module-5A.pdf

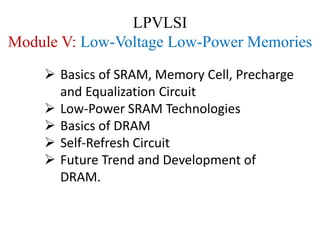

- 1. LPVLSI Module V: Low-Voltage Low-Power Memories Basics of SRAM, Memory Cell, Precharge and Equalization Circuit Low-Power SRAM Technologies Basics of DRAM Self-Refresh Circuit Future Trend and Development of DRAM.

- 2. LOW-POWER CMOS RANDOM ACCESS MEMORY CIRCUITS

- 3. Basics of SRAMs In general the pins of a SRAM are: 1.Addresses (Ao ... An); which define the memory location; 2. Write Enable (WE); which selects between the read and write modes; 3. Chip Select (CS); which selects one memory out of several within a system; 4. Output Enable (DE); which is used to enable the output buffer; and 5. Input/Output data (I/O). 6. Power supply pins.

- 5. The memory array contains the memory cells which are readable and writable. The row decoder (X-decoder) selects I out of n = 2K rows, while the column decoder (Y- decoder) selects I = 2i out of m = 2j columns. The address (row and column) are not multiplexed as in the case of a DRAM. Sense amplifiers detect small voltage variations on the memory complementary bit-line which reduces the reading time.

- 6. The conditioning circuit permits the precharge of the bit-lines. The access time is determined by the critical path from the address input to the data output as shown below. This path contains address input buffer, row decoder, memory cell array, sense amplifier and output buffer circuits. The word-line decoding and bit-lines sensing delay times are critical delay components.

- 7. To reduce the sensing time during a read operation, the swing on the bit-lines should be as small as possible.

- 8. The critical path for read access in SRAM

- 9. Typical timing of a SRAM: (a) read cycle (b) write cycle

- 10. A timing diagram during read cycle is shown above. During this time the data stored in a specific SRAM location (defined by the address) is read out. For a read cycle, two times are shown in the figure; the read cycle time, tRC, and the address access time, tAA. Figure shows the write cycle which permits change to the data in an SRAM. Two times are indicated, the write cycle time, tWC, and the write recovery time, tWR.

- 11. (Word line) (Bit line) (Bit line bar) 6T SRAM Cell General diagram of 6T SRAM cell

- 12. READ operation:

- 13. READ operation:

- 14. Write operation: