VLSI STEM Poster

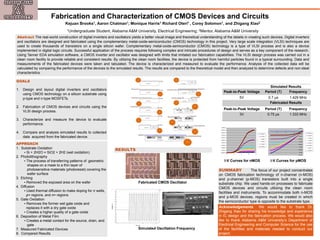

- 1. Fabrication and Characterization of CMOS Devices and Circuits Kejuan Brooks1, Aaron Chatman1, Monique Harris1 Richard Oteri1 , Corey Solomon1, and Zhigang Xiao2 1Undergraduate Student, Alabama A&M University, Electrical Engineering; 2Mentor, Alabama A&M University Abstract The real-world construction of digital inverters and oscillators yields a better visual image and theoretical understanding of the details in creating such devices. Digital inverters and oscillators are designed and fabricated using the complementary metal-oxide-semiconductor (CMOS) technology in this project. Very large scale integration (VLSI) techniques are used to create thousands of transistors on a single silicon wafer. Complementary metal-oxide-semiconductor (CMOS) technology is a type of VLSI process and is also a device implemented in digital logic circuits. Successful application of the process requires following complex and intricate procedures of design and serves as a key component of the research. Using Tanner EDA simulation software, a CMOS inverter and oscillator was designed with limits that imitated our fabrication capabilities. The VLSI design process was carried out in a clean room facility to provide reliable and consistent results. By utilizing the clean room facilities, the device is protected from harmful particles found in a typical surrounding. Data and measurements of the fabricated devices were taken and tabulated. The device is characterized and measured to evaluate the performance. Analysis of the collected data will be calculated by comparing the performance of the devices to the simulated results. The results are compared to the theoretical model and then analyzed to determine defects and non-ideal characteristics. Acknowledgements We would like to thank Dr. Zhigang Xiao for sharing his knowledge and experience in IC design and the fabrication process. We would also like to thank Alabama A&M University’s Department of Electrical Engineering and Computer Science for the use of the facilities and materials needed to conduct our project. GOALS 1. Design and layout digital inverters and oscillators using CMOS technology on a silicon substrate using p-type and n-type MOSFETs. 2. Fabrication of CMOS devices and circuits using the VLSI design process. 3. Characterize and measure the device to evaluate performance. 4. Compare and analysis simulated results to collected data acquired from the fabricated device. I-V Curves for nMOS -0.0045 -0.004 -0.0035 -0.003 -0.0025 -0.002 -0.0015 -0.001 -0.0005 0 0.0005 -8 -6 -4 -2 0 Series1 Series2 Series3 Series4 Series5 Series6 Series7 Series8 0.00E+00 1.00E-04 2.00E-04 3.00E-04 4.00E-04 5.00E-04 6.00E-04 7.00E-04 8.00E-04 9.00E-04 1.00E-03 0 2 4 6 8 Series1 Series2 Series3 Series4 Series5 Series6 I-V Curves for pMOS RESULTS SUMMARY The focus of our project concentrates on CMOS fabrication technology of n-channel (n-MOS) and p-channel (p-MOS) transistors built into a single substrate chip. We used hands-on processes to fabricate CMOS devices and circuits utilizing the clean room facilities and instruments. To accommodate both n-MOS and p-MOS devices, regions must be created in which the semiconductor type is opposite to the substrate type. APPROACH 1. Substrate Oxidation ▪ Si + 2H2O = SiO2 + 2H2 (wet oxidation) 2. Photolithography ▪ The process of transferring patterns of geometric shapes on a mask to a thin layer of photosensitive materials (photoresist) covering the wafer surface 3. Etching ▪ Removed the exposed area on the wafer 4. Diffusion ▪ Used thermal diffusion to make doping for n wells, p+ regions, and n+ regions 5. Gate Oxidation ▪ Removes the former wet gate oxide and replaces it with a dry gate oxide ▪ Creates a higher quality of a gate oxide 6. Deposition of Metal Film ▪ Creates a metal contact for the source, drain, and gate 7. Measured Fabricated Devices 8. Compared Results Simulated Results Peak-to-Peak Voltage Period (T) Frequency 5V 0.7 µs 1.429 MHz Fabricated Results Peak-to-Peak Voltage Period (T) Frequency 3V 0.75 µs 1.333 MHz Simulated Oscillation Frequency Fabricated CMOS Oscillator