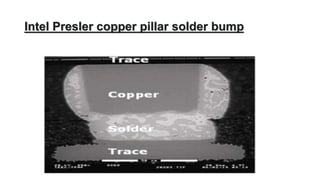

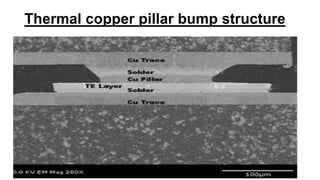

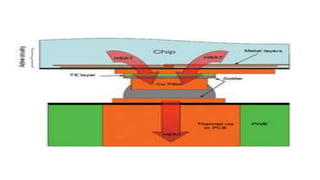

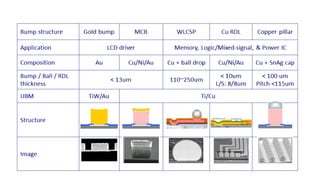

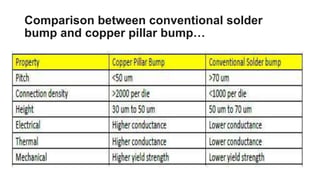

The document discusses thermal copper pillar bumps, which are thermoelectric devices embedded in flip chip interconnects. It provides a brief history of solder bump and copper pillar bump technology. The thermal copper pillar bump structure is described, which incorporates a thin-film thermoelectric layer to enable active heat transfer. Applications include general cooling, precision temperature control, power generation, and cooling of chip hotspots. Benefits include low cost, lead-free, and superior electromigration performance. In conclusion, copper pillar bump technology is emerging for die-to-die bonding due to advantages over solder bumps.