Recommended

PDF

20210925_jazug_azure_what_to_do_first

PPTX

PDF

知っているようで知らないNeutron -仮想ルータの冗長と分散- - OpenStack最新情報セミナー 2016年3月

PDF

Docker 9 tips~意外と知られていない日常で役立つ便利技

PDF

メトリクスによるソフトウェア品質評価・改善および製品品質実態

PDF

若手インフラエンジニアの課題と教育(クラウド全盛期の時代にインフラエンジニアをどのように育てるか?)

PDF

エクストリーム ネットワークス レイヤ2/3スイッチ基本設定ガイド

PDF

【Unite Tokyo 2019】「禍つヴァールハイト」最大100人同時プレイ!モバイルオンラインゲームの実装テクニック

PDF

Nutanix Community Edition 5.18 徹底解説

PPTX

PDF

エンジニア向け夏期特別講座 〜 Red Hat OpenStack徹底解説! 第二部 OpenStackの内部構造

PDF

PDF

CyberAgentのPrivateCloudeを支えるStorage基盤

PDF

PPTX

PDF

PDF

PDF

PDF

UXとUXD~長期的ユーザビリティをどう作りどう測るか?

PDF

Smart se seminor no6 agileqa cybozu

PDF

AIによる未来のUXデサイン? 〜 ChatGPT・AIartなど 〜

PDF

PPTX

PDF

Spring Initializrをハックする-カスタマイズを通してその内部実装を覗く

PDF

PPTX

Windows Server Community Meetup#3:Windows RDMA Networking for Windows Server ...

PDF

RUM と STM で実現する動画視聴における信頼性エンジニアリング

PDF

FIDO2導入とヤフーがめざすパスワードレスの世界

PPTX

PPTX

More Related Content

PDF

20210925_jazug_azure_what_to_do_first

PPTX

PDF

知っているようで知らないNeutron -仮想ルータの冗長と分散- - OpenStack最新情報セミナー 2016年3月

PDF

Docker 9 tips~意外と知られていない日常で役立つ便利技

PDF

メトリクスによるソフトウェア品質評価・改善および製品品質実態

PDF

若手インフラエンジニアの課題と教育(クラウド全盛期の時代にインフラエンジニアをどのように育てるか?)

PDF

エクストリーム ネットワークス レイヤ2/3スイッチ基本設定ガイド

PDF

【Unite Tokyo 2019】「禍つヴァールハイト」最大100人同時プレイ!モバイルオンラインゲームの実装テクニック

What's hot

PDF

Nutanix Community Edition 5.18 徹底解説

PPTX

PDF

エンジニア向け夏期特別講座 〜 Red Hat OpenStack徹底解説! 第二部 OpenStackの内部構造

PDF

PDF

CyberAgentのPrivateCloudeを支えるStorage基盤

PDF

PPTX

PDF

PDF

PDF

PDF

UXとUXD~長期的ユーザビリティをどう作りどう測るか?

PDF

Smart se seminor no6 agileqa cybozu

PDF

AIによる未来のUXデサイン? 〜 ChatGPT・AIartなど 〜

PDF

PPTX

PDF

Spring Initializrをハックする-カスタマイズを通してその内部実装を覗く

PDF

PPTX

Windows Server Community Meetup#3:Windows RDMA Networking for Windows Server ...

PDF

RUM と STM で実現する動画視聴における信頼性エンジニアリング

PDF

FIDO2導入とヤフーがめざすパスワードレスの世界

Similar to 「電子立国日本の自叙伝」に見る半導体産業温故知新

PPTX

PPTX

PPTX

PPTX

「揚げて炙ってわかる�コンピュータの仕組み」の舞台裏

PPTX

PPTX

PPTX

チップレベルでカスタマイズできることで見える世界の体験

PPTX

PDF

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

PPTX

センサ端末構築を牽引するマイコン・LSI技術とその動向

PPT

PPTX

研究を「社会実装」する“別の”方策(d.lab-VDECデザイナーズフォーラム)

More from Junichi Akita

PPTX

教員自身の「融合的な学び」の体験�〜「ハルロック」と「分解のススメHyper」〜

PPTX

M5Stack用のつよつよ系負荷を駆動するUnit群(スイッチサイエンス年度末大感謝祭 240223)

PPTX

M5Stackで脱出ゲームのギミックを作ってみた件(M5StackユーザーミーティングLT)

PPTX

PPTX

日本の「ものづくり」の可能性:中国深センとの比較を通して

PPTX

PPTX

PPTX

日本での電子回路の導入教育の可能性:中国との比較を通して

PPTX

PPTX

PPTX

3Dプリンタを改造してチップマウンタを作ってみたら物理的にForkされた件

PPTX

PPTX

PPTX

PPTX

STM32F互換マイコン(自称を含む)を�軽く解析してみた

PPTX

基板設計の基礎知識と実践(別名:基板と仲良くなる方法)

PPTX

PPTX

PPTX

うっかりチップマウンタを自作して薄い本を書いてみた

PPTX

多様な学生の教材としてしてのプロトタイピング用マイコンボードの可能性

「電子立国日本の自叙伝」に見る半導体産業温故知新 1. 2. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

自己紹介

本業:金沢大の教員

専門:集積回路、イメージセンサ、インタラクション

好きなプロセスはCMOS 0.35um

本業2:Maker(メイカー)、ハンダテラピスト

好きな半田はPb:Sn=37:63

3. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

Contents

半導体の基礎知識

物性〜製造〜回路〜システム

「電子立国日本の自叙伝」とその時代背景

どういう時代だったのか?

「電子立国日本の自叙伝」その後

その後、時代はどう進んでいったのか?

そこから、何を学ぶべきなのか?

4. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

※Disclaimer

「昔はよかった」とか「日本の半導体の復活」

みたいなことは、毛頭、全く興味はありません

歴史をふまえて、現状を知り、未来を考えた

い、という立場です

これをきっかけに、半導体の中身(作り方や

原理)について、知識を持つ機会にできれば

と思います。

そして、半導体の非専門家の皆さんが、半導

体とどう向き合うとシアワセか、を、いっしょに

考えたいと思います

5. 6. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

今日のお題:「半導体」

チップ(半導体チップ)

=集積回路(Integrated Circuits; IC)

「シリコン」「石」と呼ばれることもある(けっこう適当)

LSI(大規模集積回路; Large Scale Integration)

導体と絶縁体の中間の

電気抵抗をもつ材料

条件に応じて導体や絶縁体になる

(電流をON/OFFできる)

それを使って電子回路をつくる

電子回路→論理回路→コンピュータにつながる

半導体=コンピュータ=現代社会

半導体を知ることは社会の未来を理解すること

7. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

(おまけ)炙って見られる

どこのご家庭にもある

BBQ用バーナー(カセットボンベ式)

3分くらい炙る

※火事・ヤケドに注意

ICチップ(パッケージ入)

チップが見えてきた!

炭化したパッケージを、

ピンセットなどで、崩していく

(チップを割らないように注意)

8. 9. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

ひとことで「半導体」といっても

プロセス:製造方法(ほとんど化学)

結晶成長、酸化、ガス拡散、イオン、・・・

デバイス:電子の挙動(ほとんど物理)

量子力学、結晶界面、電子伝導

回路:トランジスタのつなぎ方(電子回路)

回路理論、オーム法則〜電子回路

ロジック:論理回路

VerilogHDL〜高位合成(FPGAもここ)

システム:アーキテクチャ(ほとんどアート)

全体を俯瞰して、実現可能性&最適化

設計ツール:CAD/EDAツール

プロセス、デバイス、回路、ロジック、・・・

秋田の

守備範囲

10. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

半導体→トランジスタ→論理回路

ref: http://imasaracmosanalog.blog111.fc2.com/category33-1.html

A X

A X

論理回路

電子回路

コンピュータ

(CPU・メモリなど)

11. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

つくりかた

「電子立国日本の自叙伝」を見ましょう

30年前の話ですが、基本原理は同じ

(準備)材料採掘→ウエハ

(前工程)ウエハに素子・回路を作る

(後工程)チップを切り分け、パッケージに入

れて、テストする

12. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

(準備)Si採掘〜ウエハまで

Si原石(SiO2)を採掘

還元してSi

eleven-nine純度(99.99…9%)に精製(→多結晶Si)

単結晶引き上げ(→インゴット)

スライス(→ウエハ)

研磨

13. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

(前工程)回路の作り込み(1)

ウエハ上に順にトランジスタや配線を作る

酸化(保護膜をつける)

写真工程(フォトリソ)&エッチングで

酸化膜に穴を開ける

https://www.hitachi-hightech.com/jp/products/device/semiconductor/etch.html

14. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

(前工程)回路の作り込み(2)

空いた酸化膜の窓から:

不純物導入(半導体の性質を変える)

配線形成(パターンを形成)※PCBと原理は同じ

https://www.aion-kk.co.jp/column/etching_vol3/

N型

P型

15. 16. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

(後工程)よく見るICへ

ダイシング(ウエハ→チップ)

ボンディング(チップと足を接続)

モールディング(樹脂封入)

検査

※前工程よりクリーン度・必要精度が低い

17. 18. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

半導体が基盤技術となった要因

Siは豊富・安価な材料(質量順で地球上2位)

SiO2が安定・高品質な絶縁体・保護膜

Siを酸化して作れる(別材料を積まなくていい)

写真工程(フォトリソ)で、まとめてつくれる

1個でも1億個でも手間は同じ

ガス拡散・イオン打ち込み等で電気的性質を

選択的に自由に変えられる

比例縮小という性質が担保する進化の道筋

=Mooreの法則

19. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

もう一つの奇跡的整合:光ファイバ

λ=1.55μm(近赤外)

半導体レーザの実用化

(AlGaAs/GaAs(0.8μm)→InGaAsP/InP)

=安価・安定な光源

石英ファイバの損失が最も小さい(極低損失帯)

=長距離伝送できる

EDFA(エルミウム・ドープ・ファイバ増幅器)で増幅できる波長

=光のまま増幅できる

分散シフトファイバ(BSF)で波長分散=0

=波形が乱れない

Siが近赤外に受光感度を持つ=受信回路の集積化

20. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

集積回路の発明

US Patent No. 2 981 877 (R. Noyce)

(1961)

US Patent No. 2 138 743 (J. Kilby)

(1959)

電子回路を半導体(ケイ素=シリコン)に作り込んだもの

インテルの創業者(の一人)

21. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

半導体の進化の歴史:Mooreの法則

ref: http://www.intel.com/jp/intel/museum/processor/index.htm

傾き:×約1.5/年

年を追って、複雑・高機能な集積回路がつくられるようになった

※G.Moore (インテルの創業者の一人)

G.Mooreが1965年に論文[1]で述べる(どちらかというと信頼性up)→C.Meadが「法則」と命名→「予測」→「指針(目標)」へ

G.E.Moore, "Cramming more components onto integrated circuits," IEEE Solid-State Circuit Newsletter, Vol.11, No.5, pp.33-35, 1965.

22. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

Mooreの法則の原論文(?)

チップにたくさん素子を

つめると・・・

信頼性が上がる

コストは下がる(が最適値がある)

ホームコンピュータも現実に

未来は明るい。あとは、どうやるか、だ。

23. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

Mooreの法則のカラクリ:比例縮小

コンピュータの電子回路の最小単位

=MOSトランジスタ

電流のON(“1”)/OFF(“0”)を制御するスイッチ

集積回路の部品(MOSトランジスタ)を、同じ

形状で、より小さく作ると・・・?

寸法: 1/α

不純物濃度: α

電源電圧: 1/α p-Si

S D

G

n-Si

n-Si

p-Si

S D

G

n-Si

n-Si

L

R.H.Dennard et al., "Design of ion-implanted MOSFET's with very small physical dimensions," IEEE J.of SSC, Vol.9, No.5, pp.256-268, 1974.

MOSトランジスタの断面構造

24. 25. 26. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

比例縮小の効果

効果:いいことばかり

速度↑(電子の移動=信号の伝搬距離が短くなる)

消費電力↓(電源電圧が下がる)

集積度(機能)↑(1つの素子が小さい=同一チップに多数)

技術が進むべき方向性が極めて明確なまれなケース

p-Si

S D

G

n-Si

n-Si

p-Si

S D

G

n-Si

n-Si

L

• 素子面積:1/α2

• 素子密度:α2

• 電流I:1/α (←電圧:1/α)

• 容量C:1/α (←C=εS/d, S:1/α2, d:1/α)

• 抵抗R:α (←R=ρL/S, S:1/α2, L:1/α)

• 回路遅延:1/α (←E:一定, S-D間:1/α)

• 消費電力:1/α2 (←V:1/α, I:1/α)

• 配線遅延時間CR:1 (変わらない) ※MOSトランジスタを

上から見たところ

(素子1個の専有面積)

物理的な詳細

27. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

般若心経だと・・・

1um

0.8um

0.5um

0.35um

18ヶ月

18ヶ月

18ヶ月

同じ用紙サイズなら文字数2倍

=機能2倍

28. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

般若心経だと・・・(その2)

1um

18ヶ月

18ヶ月

0.5um

0.8um

同じ内容なら用紙サイズ1/2

=コスト1/2

29. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

半導体の面白さと難しさ

Si平面に好きなものを作れる

CPU、メモリ、論理回路、アナログ回路

MEMS、センサ、・・・

白紙キャンパスに絵を描くようなもの

最後はGDS(レイアウトデータ)

設計方法はいろいろ

(回路図、HDL、図形描画・・・)

逆に、自由すぎて、どこから手を付けていいのか

途方に暮れることもしばしば・・・

30. 31. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

「電子立国日本の自叙伝」

1991 (平成3)年 1月〜9月、NHKスペシャル

第1回 新・石器時代 ~驚異の半導体産業~

第2回 トランジスタの誕生

第3回 石になった電気回路

第4回 電卓戦争

第5回 8ミリ角のコンピューター

第6回 ミクロン世界の技術大国

ディレクター:相田洋、語り:三宅民夫

32. 33. 34. 35. 36. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第1回:概論・現況

「チップ作る。どこから?」「Si掘るところから!」

フォトリソ工程の説明

クリーンルーム内の映像はけっこう貴重

37. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

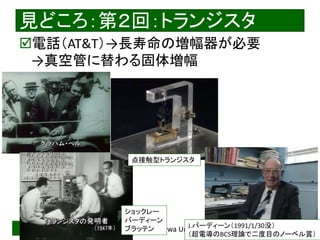

見どころ:第2回:トランジスタ

電話(AT&T)→長寿命の増幅器が必要

→真空管に替わる固体増幅

J.バーディーン(1991/1/30没)

(超電導のBCS理論で二度目のノーベル賞)

点接触型トランジスタ

ショックレー

バーディーン

ブラッテン

38. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第2回:トランジスタ

Geの精製(ゾーン・メルト法)

単結晶Geをつくる(引き上げ(CZ)法)

ショックレーは「無理だ」と言っていたらしい

(多結晶Geから単結晶を取り出して使う)

39. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第2回:トランジスタ

Geトランジスタの作り方の工夫

バイポーラ・トランジスタ(※MOSFETとは別)

PNP構造の「N」を薄く安定に作るのがポイント

引き上げ(CZ)法(結晶成長の途中で不純物投入)

合金法

ソニーのラジオ←品質安定化の工夫

40. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第3回:集積回路

Geトランジスタ→大規模システムへ

コンピュータ、ミサイル制御

問題点:配線が複雑・低信頼性+温度特性が悪い

41. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第3回:集積回路

Siトランジスタへの期待

Siは反応性が高く、不安定

Siの熱酸化によるSiO2の形成=保護膜(偶然)

ガス拡散法で不純物導入(太陽電池から)→Trへ

Siの精製・単結晶成長

42. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第3回:集積回路

Siトランジスタ→集積回路へ

Siトランジスタの構造:メサ型→プレーナ型

実はここで集積回路の要素技術は揃っていた

マーキュリー計画→アポロ計画へ

←非力なロケットからの回路の小型軽量化の要求

軍需の大量購入で量産技術が大きく進んだ

日本でも似た技術が

プレーナ型特許の回避

モレキュラー

・エレクトロニクス

(→集積回路)

メサ型:露出部があり不安定 プレーナ型:露出部がない

43. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第4回:電卓戦争

計算機の歴史

機械式(手回し式)

コンピュータの理論・ブール代数と融合

リレー式→トランジスタ式

44. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第4回:電卓戦争

アメリカより日本では小型化のニーズがあった

論理回路の省回路化からのMOSトランジスタ

理論的には示されていた(byバーディーン)

実際にはあまりにも不安定

(作ってもすぐ動かなくなる)

Naが原因とわかり、実用化(日本の技術)

集積回路誕生の頃は、ここまで複雑なシステムがな

かった(byノイス)

バイポーラのNANDゲート MOSのNANDゲート

45. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第4回:電卓戦争

MOS回路の進化

←電卓のための省回路・低電力

pMOS→ダイナミックpMOS

→CMOS→クロックトCMOS

TI製電卓LSI→コモディティ化

差別化へ

機能を割り切った低価格

液晶→太陽電池駆動

カスタムLSIを手設計

46. 47. 48. 49. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第5回:マイクロプロセッサ

ビジコン(日本)が、インテルに

電卓LSIの設計・製造を依頼(嶋が渡米)

インテルはもともとメモリの会社で、オーバーキャパ

テッド・ホフがストアードプログラム方式を発案

嶋+F.ファジンが論理設計

※このあたりは遠藤「計算機屋かく戦えり」等で

大型・ミニコンの歴史を踏まえるとより理解が進むと思います

革命的

アイディア

50. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第5回:マイクロプロセッサ

当時のLSI設計(レイアウト)→製造マスク

※現在はCAD or 半自動化されているが原理は

同じ

論理回路図

チップ製造

(写真工程)へ

51. 52. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

見どころ:第6回:周辺技術

周辺技術の開発の苦労話

ダイシング

リードフレーム

ボンダー

クリーンルームとチリ・純粋

ステッパー

53. 54. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

その後:技術面

基本的な方針は変わっていない

微細化・高集積化

要素技術は、問題を乗り越えて進化

MOSトランジスタ:平面型→FD-SOI→FinFET(立体)

配線:Al→Cu

エレクトロマイグレーション(電流で原子が動いて断線)

フォトリソ

光:可視光→紫外線→軟X線(EUV)

フォトマスク:等倍→縮小→液浸・位相シフト・・・

55. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

その後:産業構造面(1)

分業化が進む

設計(ファブレス企業)

製造(ファブ/ファウンドリ)

AMDもファブレス化

特に先端プロセスの

製造は集約化が進む

TSMC, Samsung

ref: https://news.mynavi.jp/article/20200324-1001940/

56. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

その後:産業構造面(2)

IP(設計資産)も分業化

特にプロセッサコアの寡占化(ARM)

→最近はRISC-Vが、特に中国で事例増加中

(ライセンス料の面よりも、オープンソース面?)

設計ツールも分業化・寡占化

昔は各社が独自EDAツール(特に日本)

今は、Cadence, Synopsysなど数社

オープンソースなEDAツールも、盛り上がりつつ

ある(特に米国)

“ACT”でSoCがコモディティ化

57. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

※第6回の最後にこんな話が(1)

超LSI技術研究組合(日本:官主導)

企業間の技術交流があった

番組内ではDRAM(規則構造:微細化)が主

→MPUは日本は追いつけていない(設計面)

MPUはソフトウエアと不可分なので後発が不利

そういえばTRONは・・・

58. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

※第6回の最後にこんな話が(2)

ロバート・ノイス氏のインタビュー

「海外の技術革新を真似→製造技術を高める」

だけで、技術革新への貢献、マインドが足りない

菊池誠氏のインタビュー

追いかけていたアメリカを超えたら目標を見失った

相田ディレクターも「重要な指摘」と言っている

ロバート・ノイス

(1990/6/3没)

59. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

ちなみに・・・

インテルはもともとメモリの会社

1968年創業、ロゴは磁気コアメモリを「食う」から

1970年、世界初のDRAM i1103出荷

1971年、EPROMの発明(i1702)

i4004〜i8080のころも、

「CPUはDRAMを売るための手段」

その後、IBM PCの8088採用などで

CPUへシフト

1985年DRAM事業から撤退

60. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

「その後」の日本の半導体産業

(吉森,中屋「国内論理系半導体産業の分析と将来戦略」,信学誌, 96, 2, pp.70-75 (2013))

2019年:6%

61. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

その後の日本の半導体産業

(朝日新聞2009/06/03)

(朝日新聞2012/10/04)

(朝日新聞

2013/02/06)

62. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

日本の半導体企業の再編

ref:https://xtech.nikkei.com/dm/article/COLUMN/20150412/413883/

※この他、独立系でソニー(イメージセンサ)が残っている

現在の

キオクシア 現在の

ソシオネクスト

63. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

最近の世界の半導体産業

まさに成長産業

AIがIoTが後押し

(WSTS (World Semiconductor Trade Statistics:世界半導体市場統計)の資料より)

64. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

Mooreの法則の罠:4MbDRAMの立上り

DRAM(半導体メモリ)は、3年ごとに4倍容量の製品

が主軸になってきた(Mooreの法則どおり)

1Mb→4Mbの世代交代で、市場の立上りを読み間

違えた

(直野「転換期の半導体・液晶産業」(日経BP,1996))

65. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

なぜ4Mbは当初売れなかたのか?

機能単価が高かったわけ

ではない

(お買い得な4Mbが売れない)

不景気だったわけでもない

(前の世代の1Mbは好調)

ユーザは4Mbが必要なかった

DRAM大口ユーザ=PC

OS:MS-DOS (1MB以上は使えない)

実際、その後、順調に4Mbは

市場が立ち上がって成長

(1991年=Windows3.1の発売)

(直野「転換期の半導体・液晶産業」(日経BP,1996))

1Mのほうが

ビット単価は高いのに

世代交代

4Mのほうが

ビット単価は安いのに

世代交代していない

66. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

機能単価と機能飢餓

Mooreの法則による半導体産業成長の

重要な前提=機能飢餓

ユーザ(市場)が、慢性的に高機能を欲している

状態

ICT産業は長年、機能飢餓状態にあった

昔のPCのカタログのウリ=性能

最近はどうか?

分野によっては機能飢餓が薄れている

最近のPCのカタログには性能が(ほぼ)載ってい

ない

67. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

機能飢餓を忘れた技術

テレビ:SDTV→HDTV→4K/8K

SDTV→HDTVは、画質に対する機能飢餓からか?

HDTV→4K/8Kでの機能飢餓は?

そもそも地上波のテレビは見られるのか?

DVD→HD-DVD vs Blu-ray→で??

http://www.garbagenews.net/archives/1935926.html http://www.nissay.co.jp/enjoy/keizai/32.html

68. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

目的と手段?

(よくある話)社員のために仕事が必要

例:似たようなマイコンの多品種化

→設計・テスト工数の大幅増で首を絞めている

ムーアの法則=基本性能の底上げ

汎用品の性能↑

カスタム品の優位性・必要性の相対的な低下

設計・チップの再流用・製品展開が有用

69. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

高品質という罠

例:DRAM

当初は交換機・汎用計算機でのニーズから

10年寿命品質・信頼性

それに向けて技術が進歩したのは事実

→(分野によっては)過剰品質に

PCでは5年寿命で十分:Micron, Samsungの躍進

典型的な「イノベーションのジレンマ」

“Made in Japan”

「安かろう悪かろう」

→「高品質」→罠?

そもそも「高品質」なん?

70. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

成功体験という罠

強烈な成功体験ほど、忘れにくい?

時代も背景も構造も変わっているのに、

同じ方法論で進もうとする

下手すると「根性論」で乗り切ろうとする

どうしたらいいんだろう・・・?

若い人は、能力も気合もあるのに・・・

71. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

Mooreの法則の今後:物性面

微細化が進みすぎて、素子として動作しない

+安定に製造できない

不安要因

製造ばらつき(設計通りの形状にならない)

不純物ばらつき(電気特性が設計通りにならない)

トンネル効果(OFFにしたつもりが電子が通り抜ける)

Siでももうちょっと行けそう

Si以外の材料では

もっといけそう

その後もなくなる

わけではない

ref: https://slideplayer.com/slide/7843454

Si原子(直径0.2nm)

×50

72. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

最近のCPU(※イメージ)

Intel Core i7 (2008)

トランジスタ(素子)数~10億個

(設計では、これらを1つも間違いなく組み合わせる)

cf: 地球の人口~70億人、中国の人口~13億人

73. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

10nm時代の半導体との付き合い方

製造不良は出るもの

冗長化、マルチコア化でコア数を調整

スケーラブル・コンピューティングと整合性がよい

トランジスタ単価(機能単価)はゼロに収束

価格を下げる→チップ面積縮小→ゼロに収束

機能をあげる→価格を維持・向上

製造工場の稼働率のためにも、チップ面積は

縮小しない

機能飢餓があるアプリケーションを探す

74. 2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

これらの知識を踏まえて・・・

「テカナリエ・レポート」を読むと、よくわかる

スマホSoCのシェア・戦略

微細加工技術の採用・使い分け

Fab(製造工場)の使い分け・戦略

プロセッサ・アーキテクチャの動向

(ARM←→RISC-V)

ARM=ARM社のライセンス製品

(組み込みの業界標準、ソフトバンクが買収)

RISC-V=オープンソース、ソフトウエアの「縛り」がない

分野で採用事例が急拡大中

※個人でも購読できます

→https://forms.gle/kqxcp5Uc8mHqoMpW9

![2021/3/21 Interface Device Laboratory, Kanazawa University http://ifdl.jp/

半導体の進化の歴史:Mooreの法則

ref: http://www.intel.com/jp/intel/museum/processor/index.htm

傾き:×約1.5/年

年を追って、複雑・高機能な集積回路がつくられるようになった

※G.Moore (インテルの創業者の一人)

G.Mooreが1965年に論文[1]で述べる(どちらかというと信頼性up)→C.Meadが「法則」と命名→「予測」→「指針(目標)」へ

G.E.Moore, "Cramming more components onto integrated circuits," IEEE Solid-State Circuit Newsletter, Vol.11, No.5, pp.33-35, 1965.](https://image.slidesharecdn.com/210321akita-210321014610/85/slide-21-320.jpg)