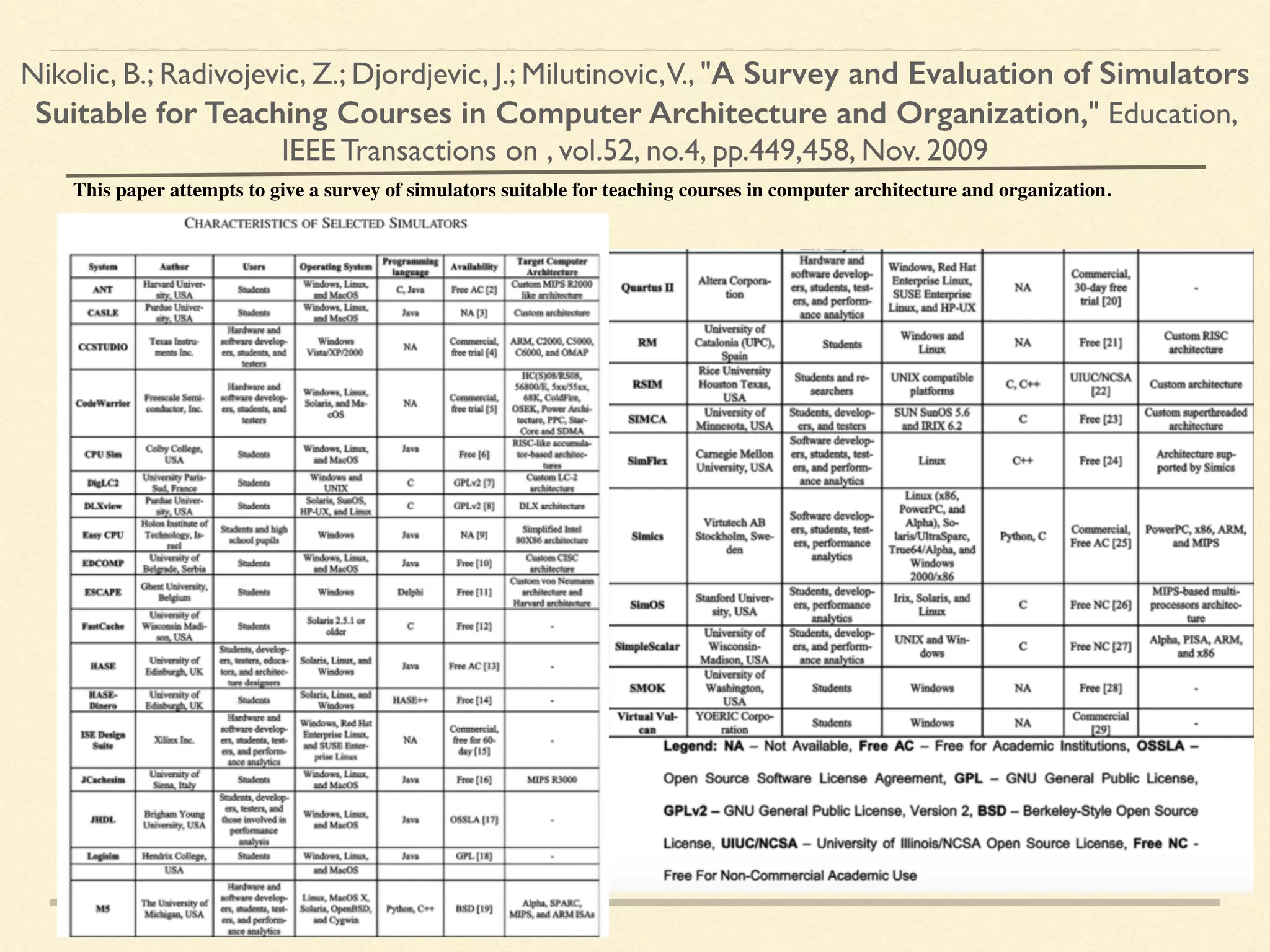

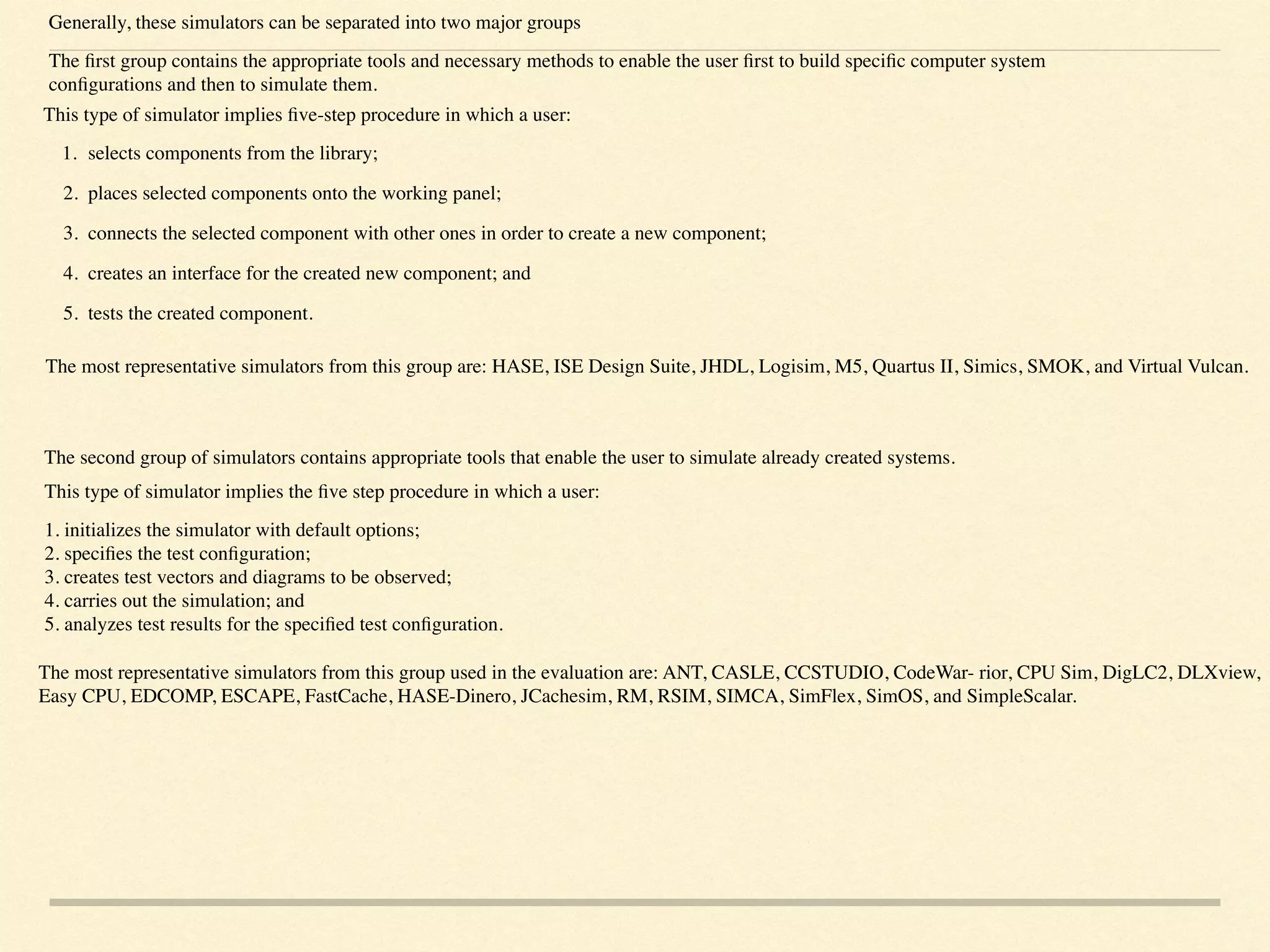

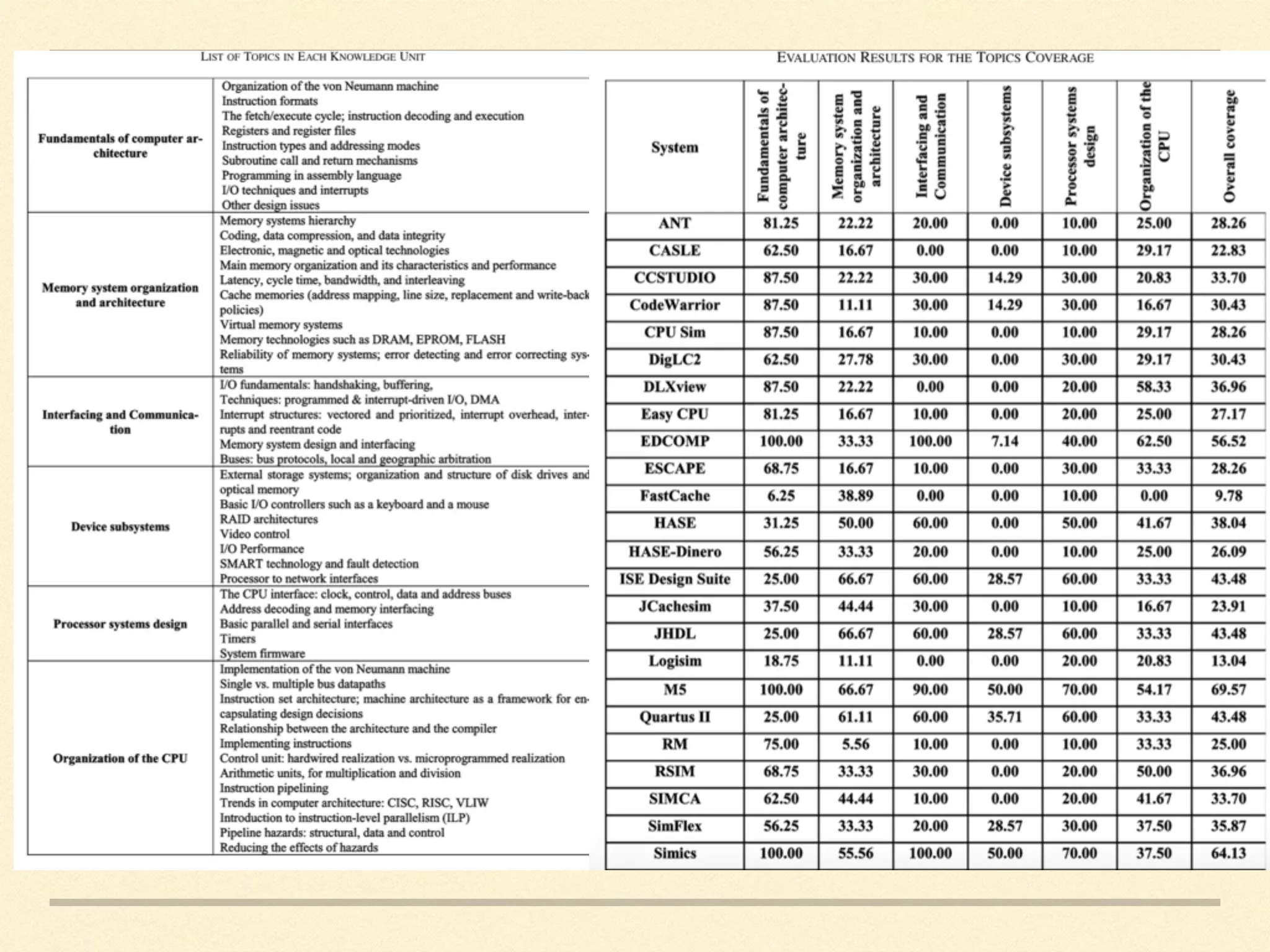

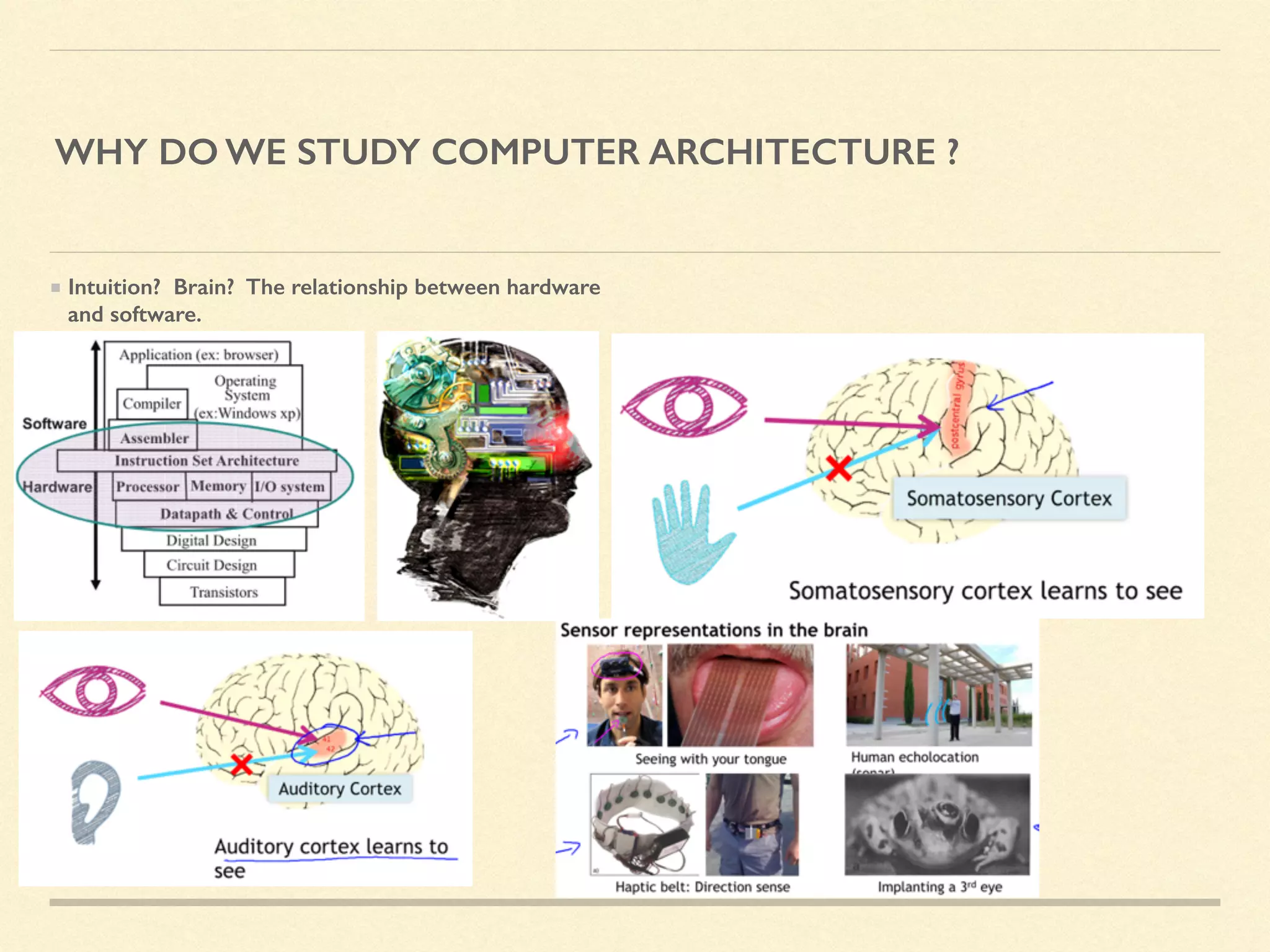

This document summarizes several university courses on computer architecture and organization. It discusses where the courses fit in their respective curriculums, how students are assessed, what topics are covered, and what materials and tools are used. The courses cover topics like digital logic, machine level representation of data, assembly level organization, memory systems, multiprocessing, and performance enhancements. Assessment methods include exams, projects, homework, and labs. Tools used include simulators, emulators, assemblers, and hardware description languages.

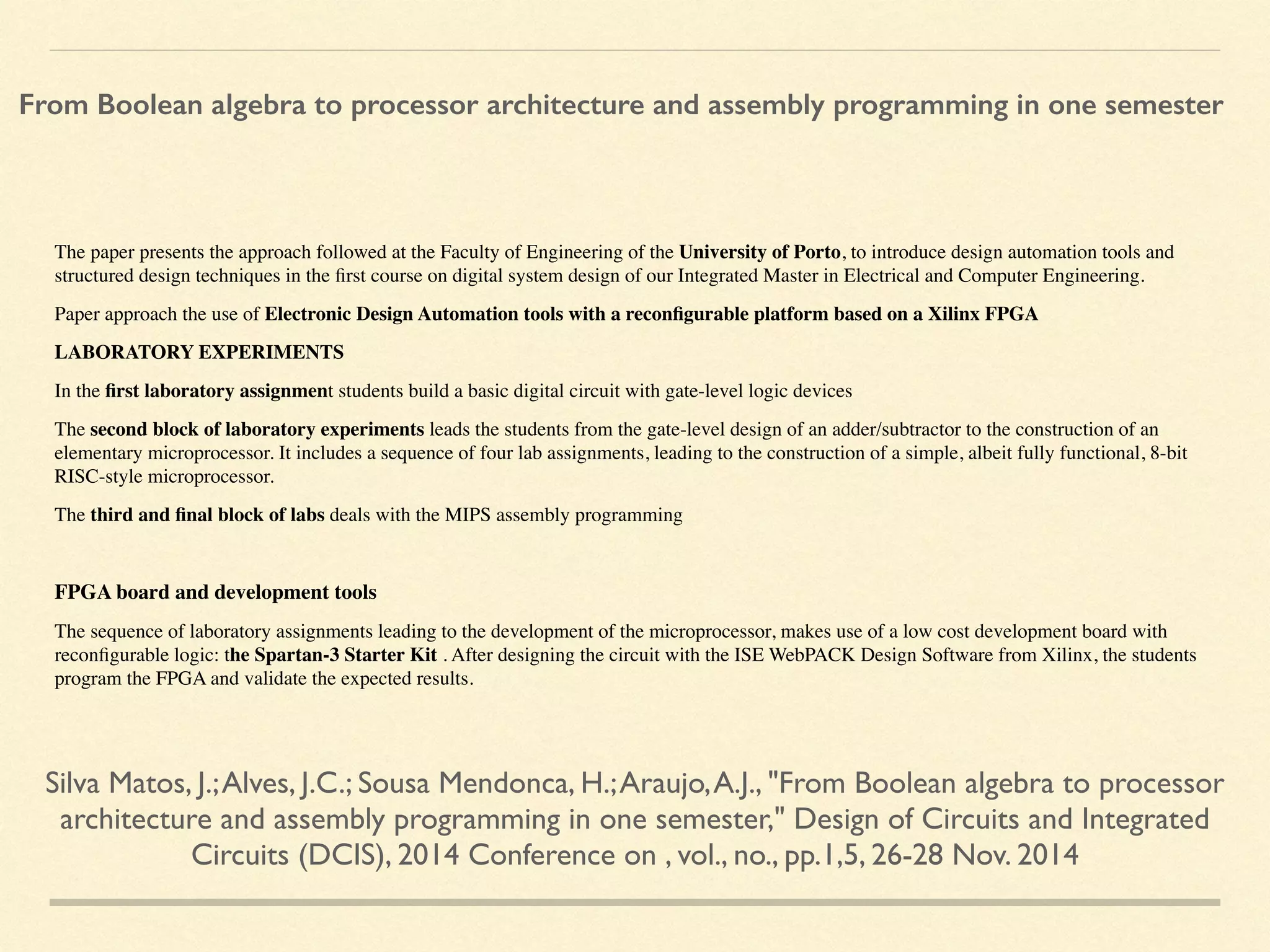

![CSL 211 - Computer Architecture, IIT Delhi

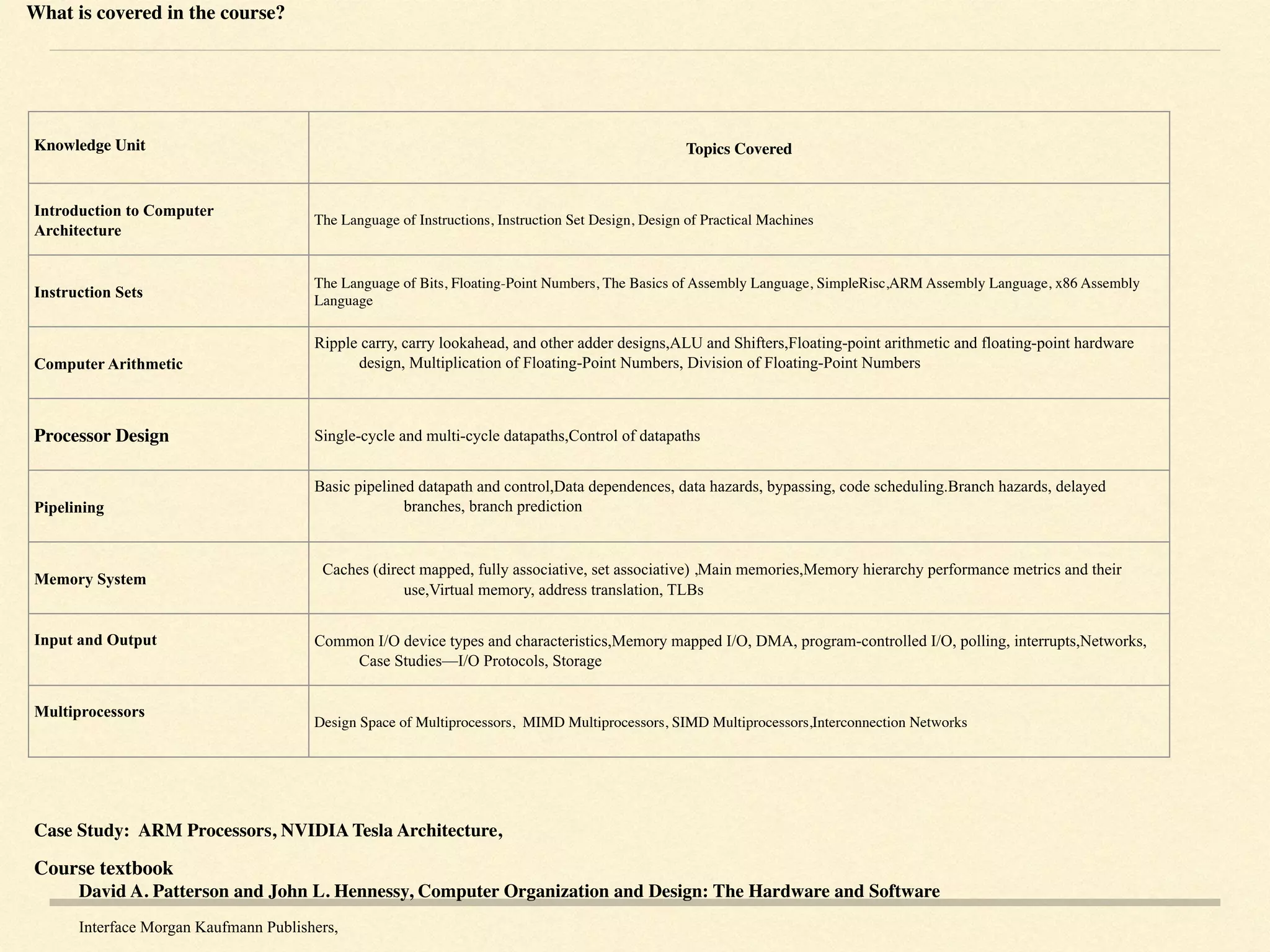

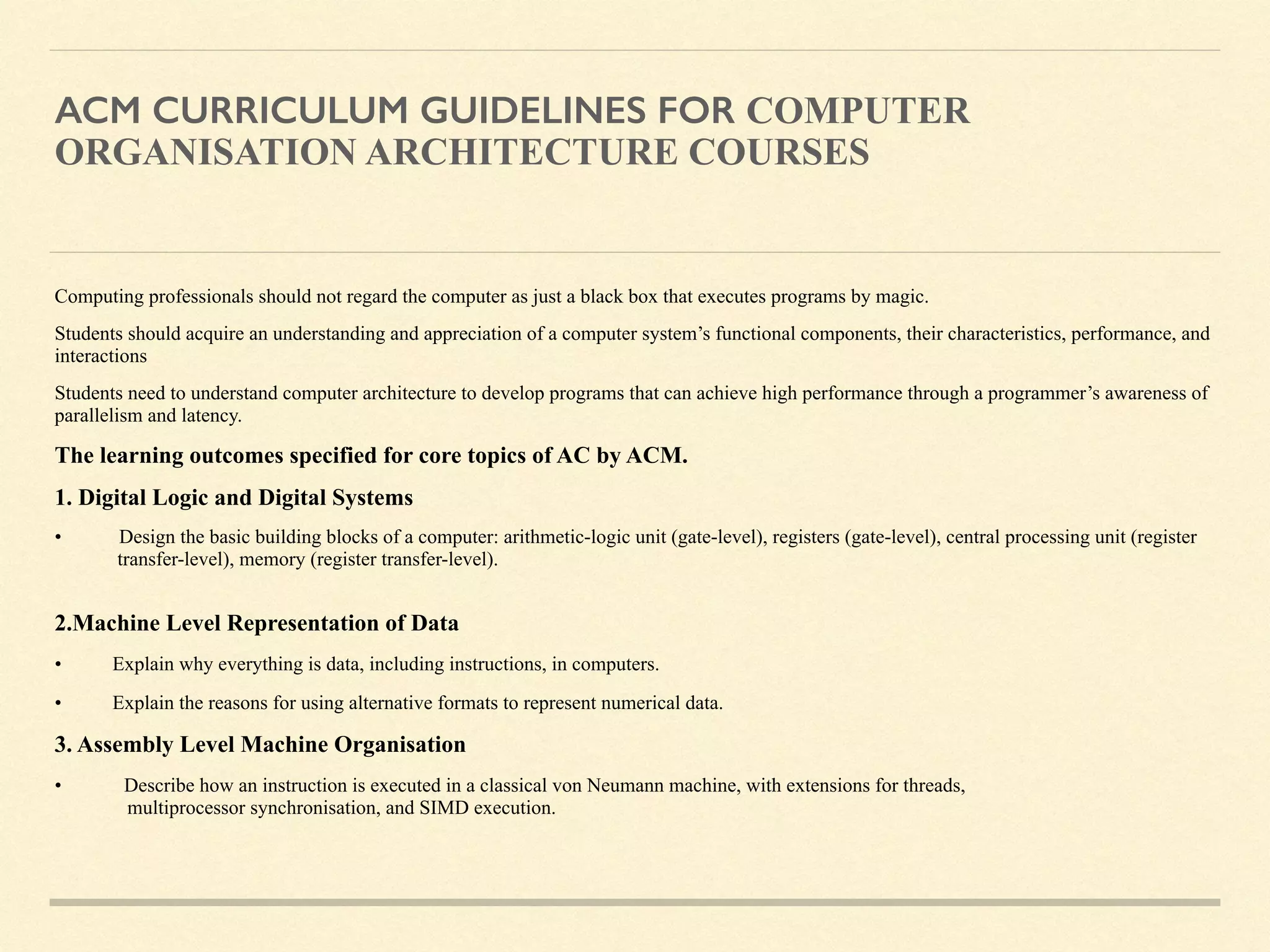

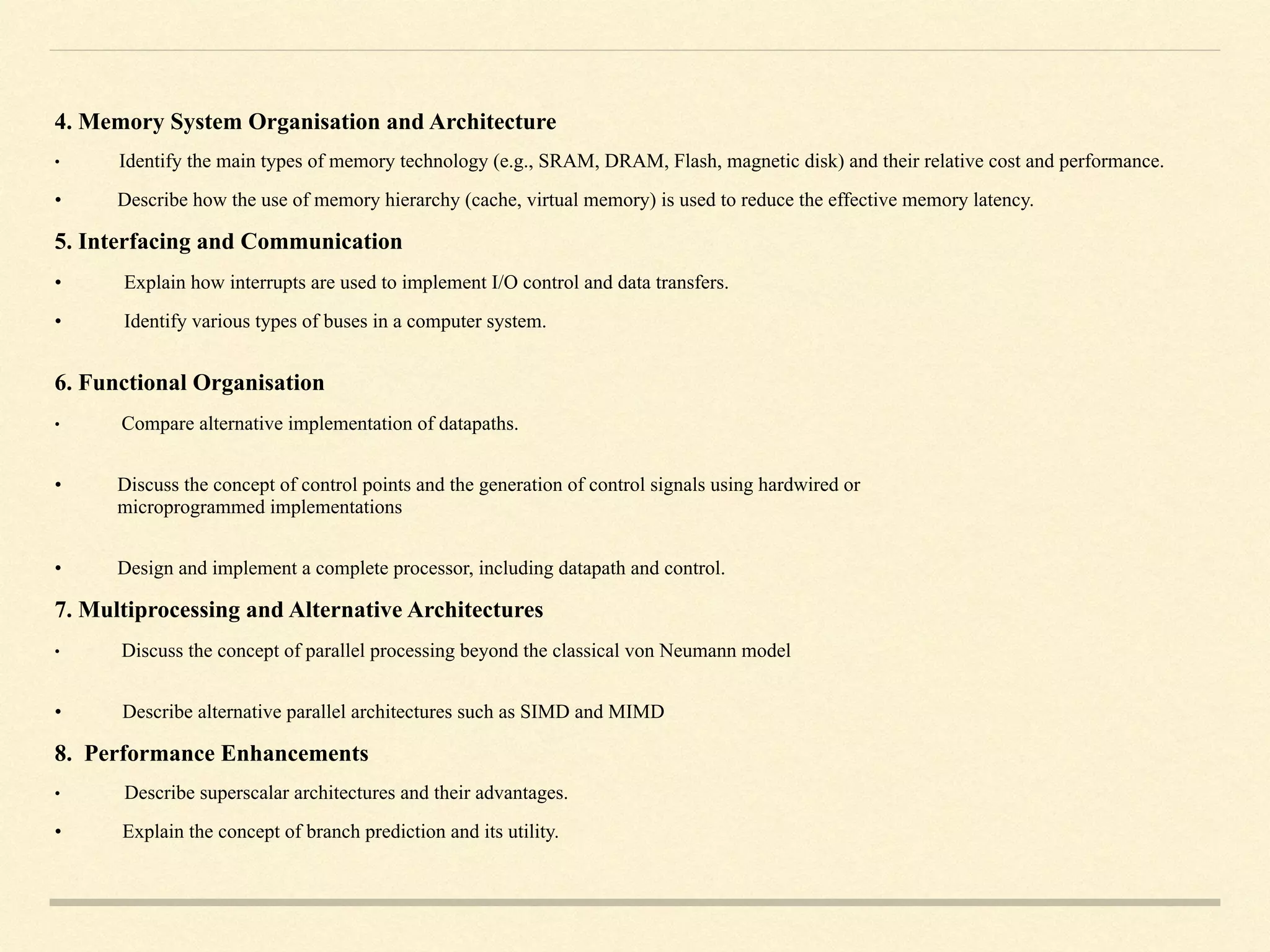

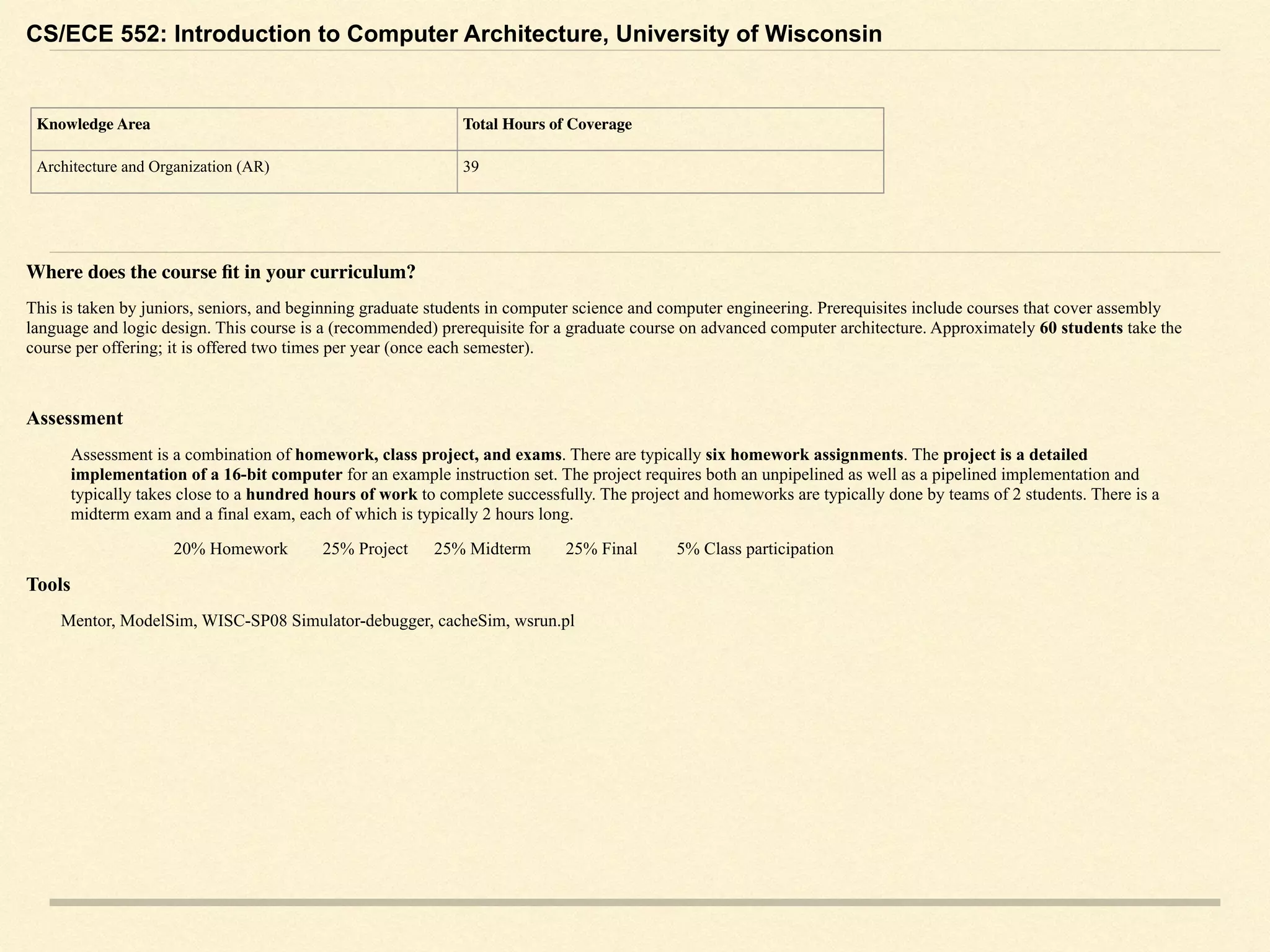

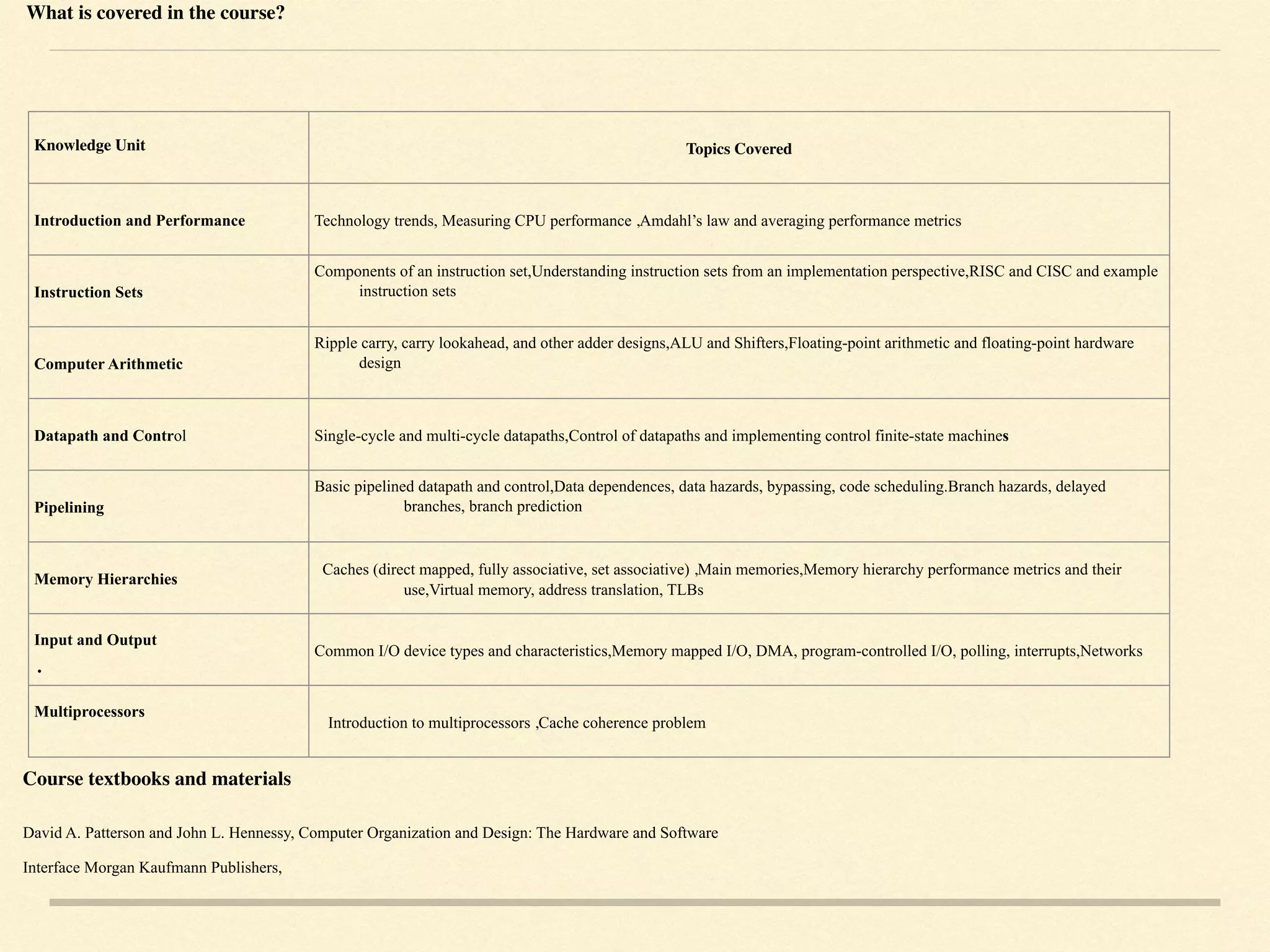

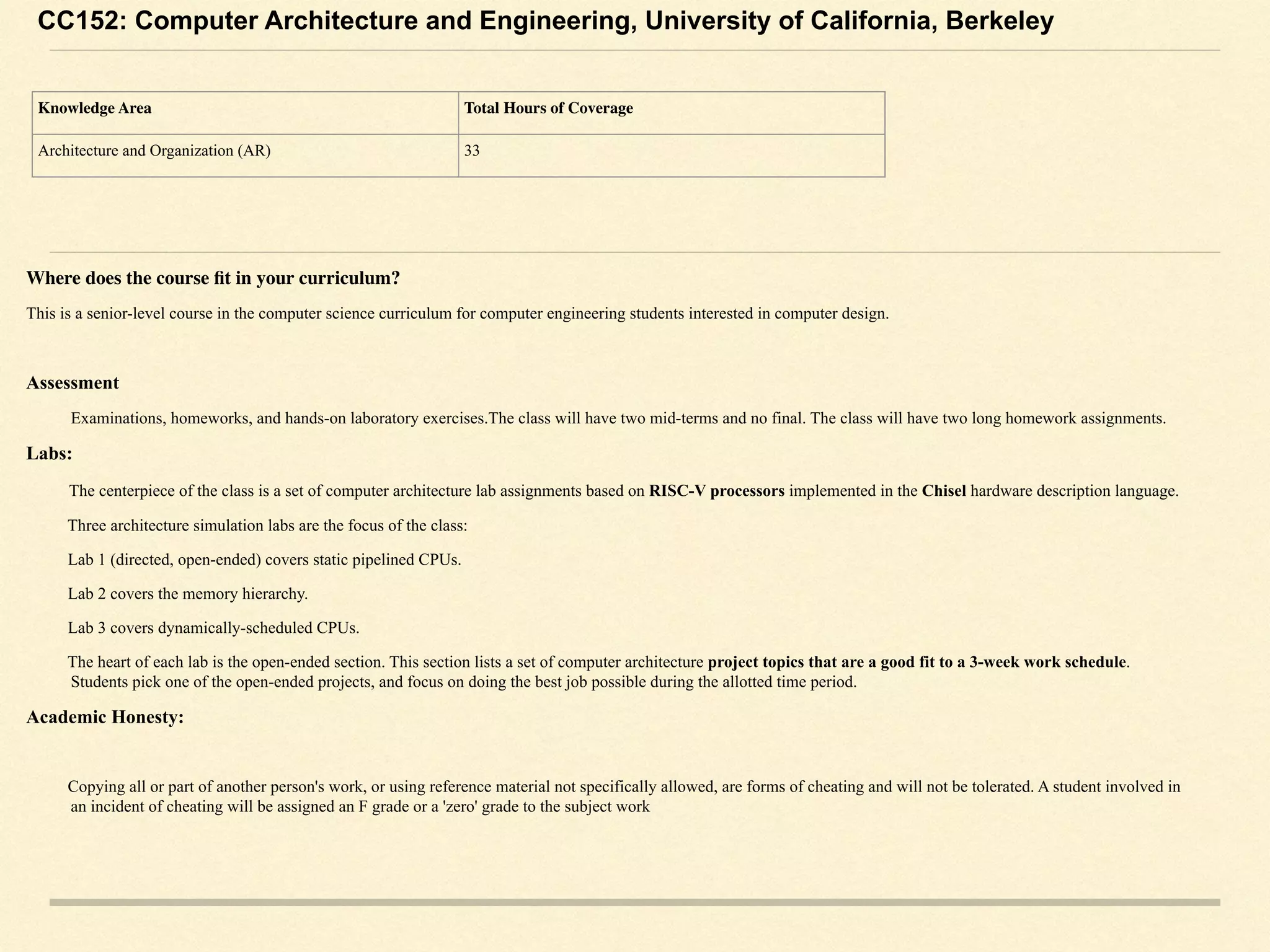

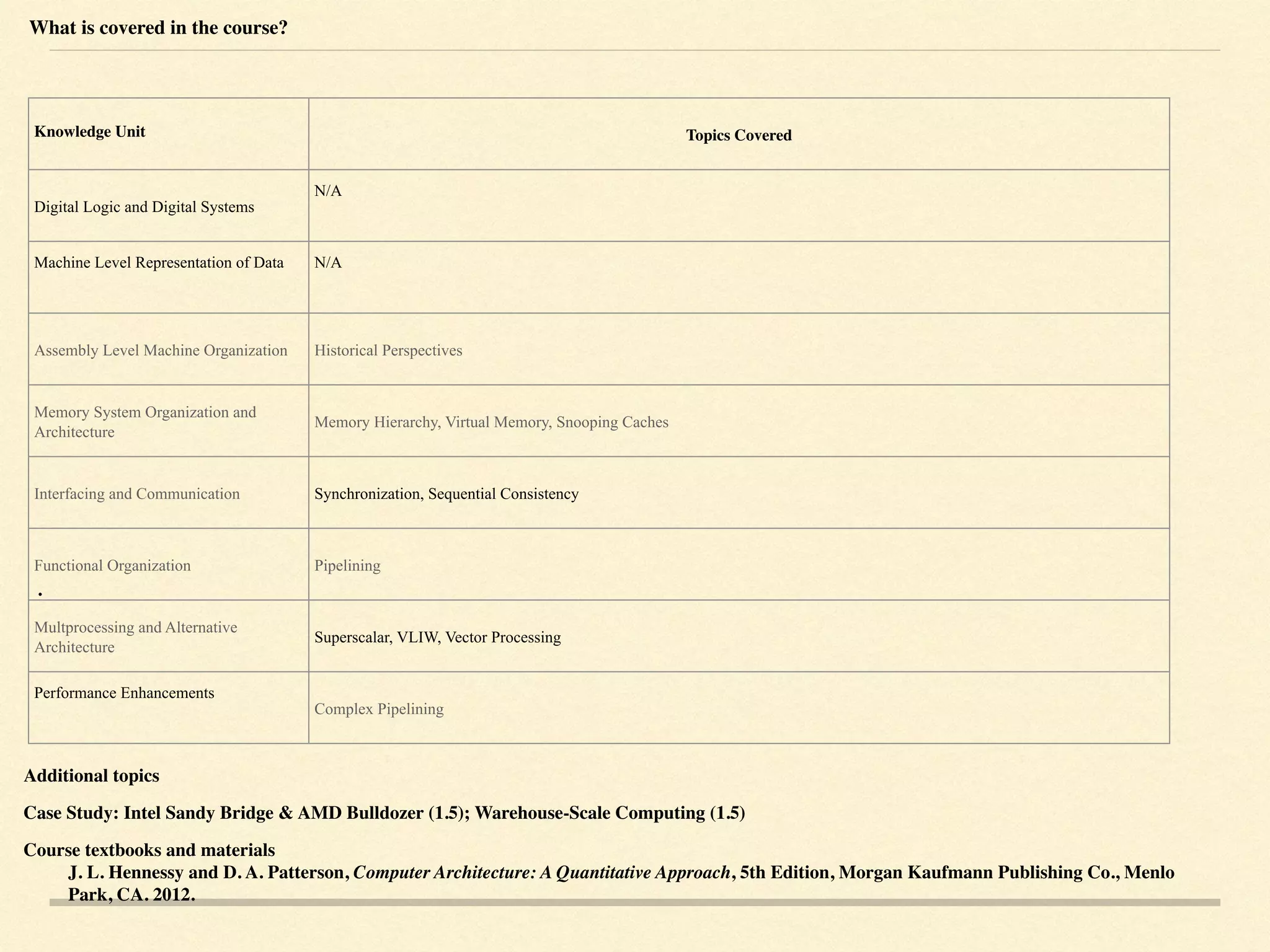

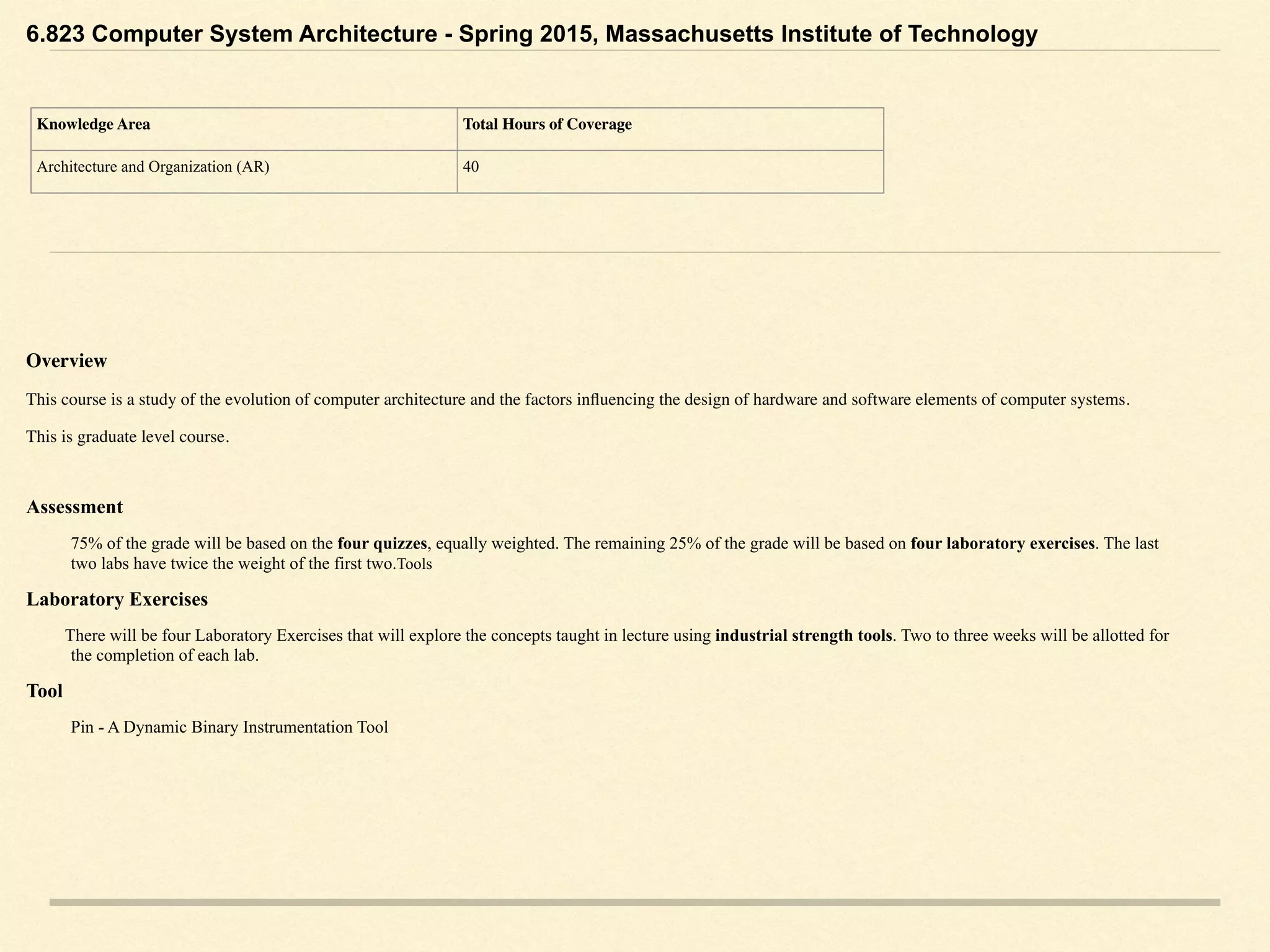

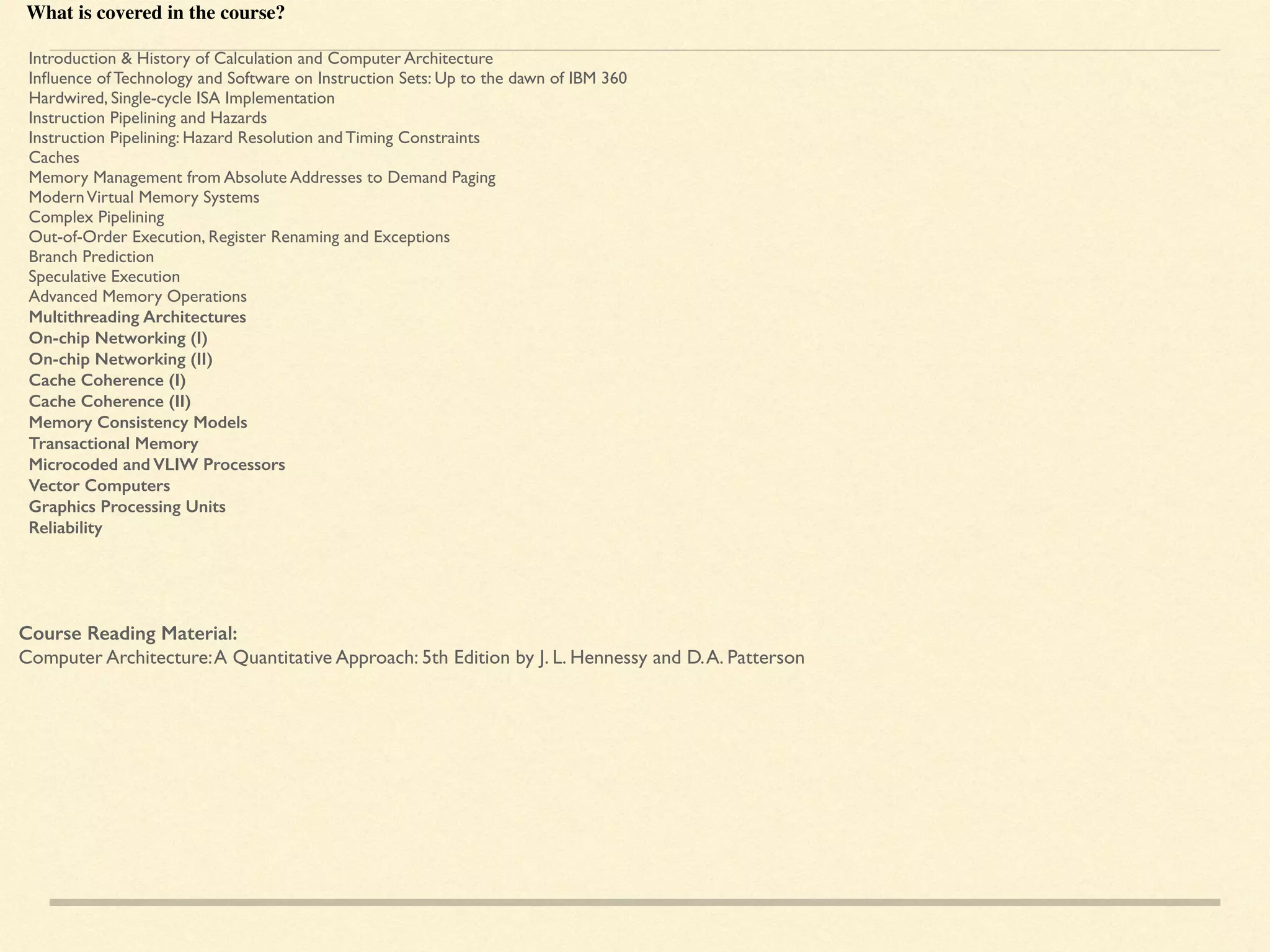

Where does the course fit in your curriculum?

The 'Computer Architecture' course is intended to teach undergraduate students in Electrical Engineering and Computer Science the basics of computer architectures.

Credits : 5 [3-1-2] (L-T-P)

Assessment

MINOR - I 10%, MINOR -II 15%, MAJOR 25%, ASSIGNMENTS 50%

Tools

Tejas Architecture Simulator, EmuArm (GUI based ARM Emulator), NASM assembler, Logisim

ACADEMIC MISCONDUCT

Academic misconduct such as cheating will not be tolerated. The work you submit in this class is expected to be your own. If you submit work that has in part

or in whole been copied from some published or unpublished source (including current or former students), or that has been prepared by someone other than

you, or that in any way misrepresents somebody else's work as your own, you will face severe disciplinary action.

Any detected cases of cheating will be pursued. Penalties can include: receiving a zero on the assignment (the minimum penalty), failing the course, having a

note placed in your permanent academic record, suspension, and ultimately expulsion.

Knowledge Area Total Hours of Coverage

Architecture and Organization (AR) 42](https://image.slidesharecdn.com/coa-150715074949-lva1-app6891/75/Computer-Oraganisation-and-Architecture-11-2048.jpg)