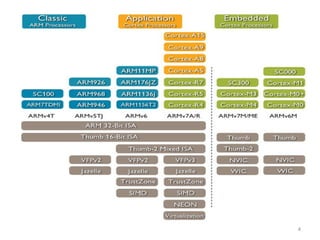

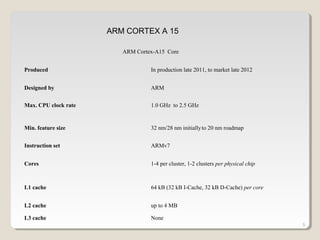

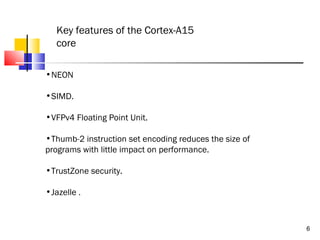

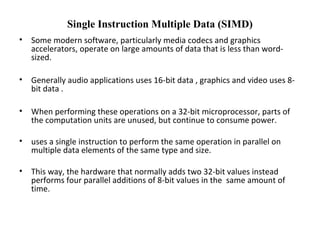

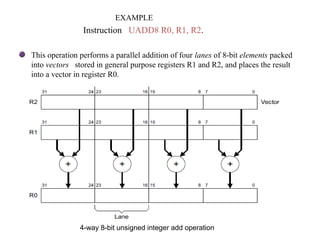

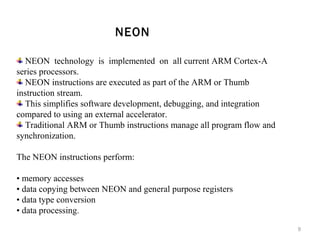

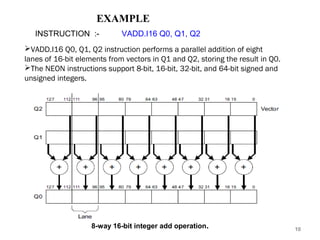

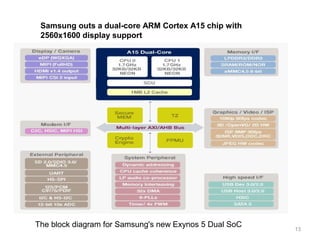

The document discusses the ARM Cortex A15 processor. It was designed by ARM and began production in late 2011 for market in late 2012. Key features include NEON for SIMD operations, a VFPv4 floating point unit, Thumb-2 instruction encoding, and TrustZone security. Applications include smartphones, computing devices, and digital home entertainment systems.

![REFERENCES

RESEARCH PAPERS

[1] Cortex™-A15 Revision: r2p0 Technical Reference Manual.

[2] W H I T E P A P E R Brian Carlson OMAP 5 Product Line Manager

Member of Group Technical Staff (MGTS) Wireless business unit. © 2011

Texas Instruments Incorporated.

[3] W H I T E P A P E R ‘ARM NEON support in the ARM’

REFERENCE BOOKS

[4] Embedded Real Time System: Concepts , Design & Programming,

Dr.K.VK.K.Prasad,Dreamtech Publication.

WEBSITE

[5] WWW.ARM.COM

[6]www.google.com

[7] www.wikipedia.com

[8] New Samsung Cortex A15-based chip opens door to “Retina” Android

tablets _ Ars Technica.htm

15](https://image.slidesharecdn.com/armcortexa15-140116041441-phpapp01/85/ARM-cortex-A15-15-320.jpg)