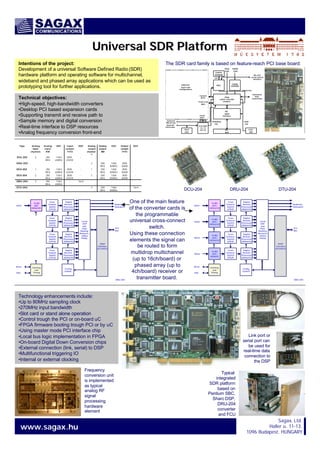

The universal SDR platform consists of modular converter cards that can be configured for multi-channel or phased array applications. The cards feature high-speed ADCs and DACs, digital signal processing resources, and programmable cross-connect switches allowing signals to be flexibly routed. This customizable open-source platform is intended as a prototyping tool to develop new SDR applications.