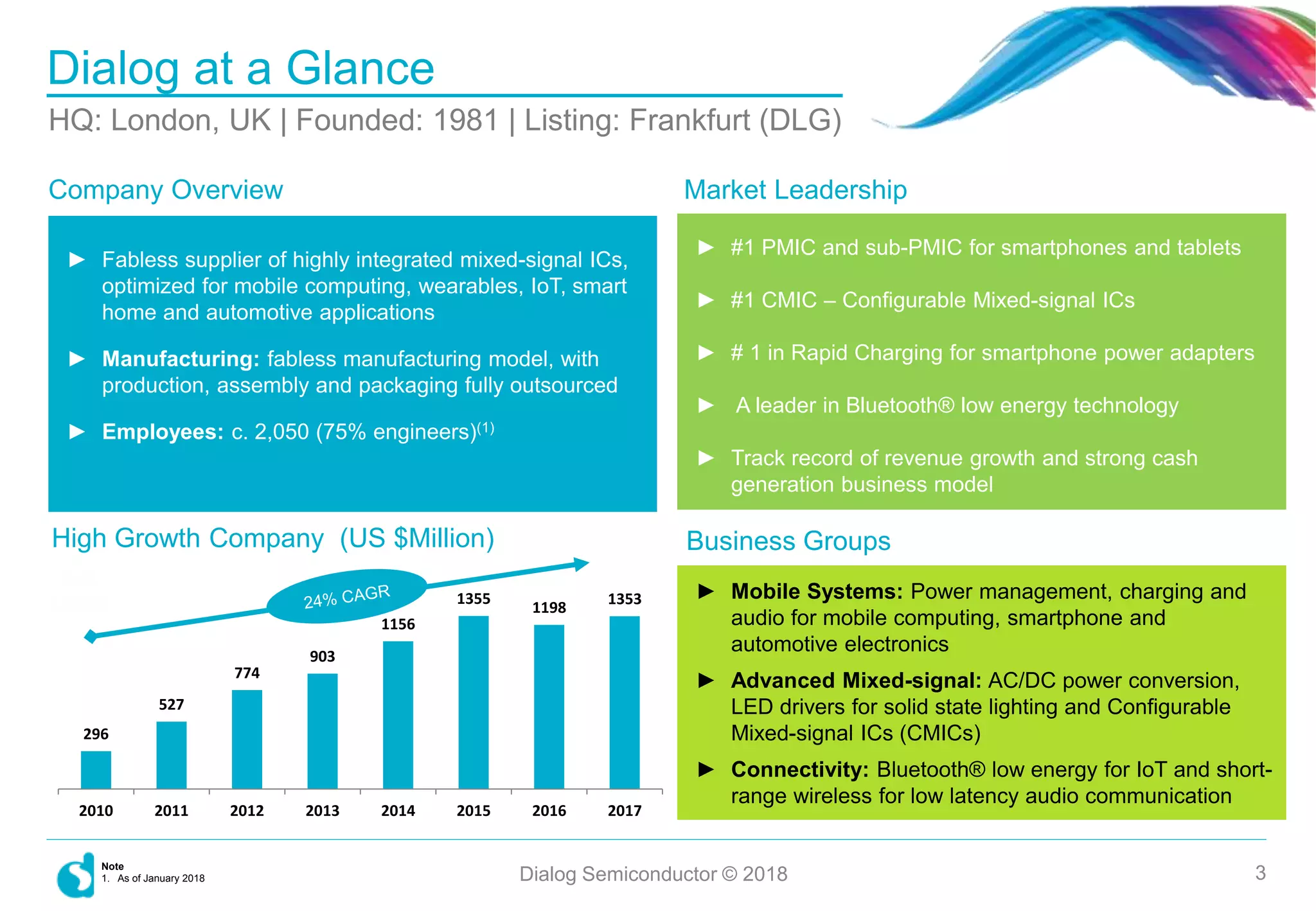

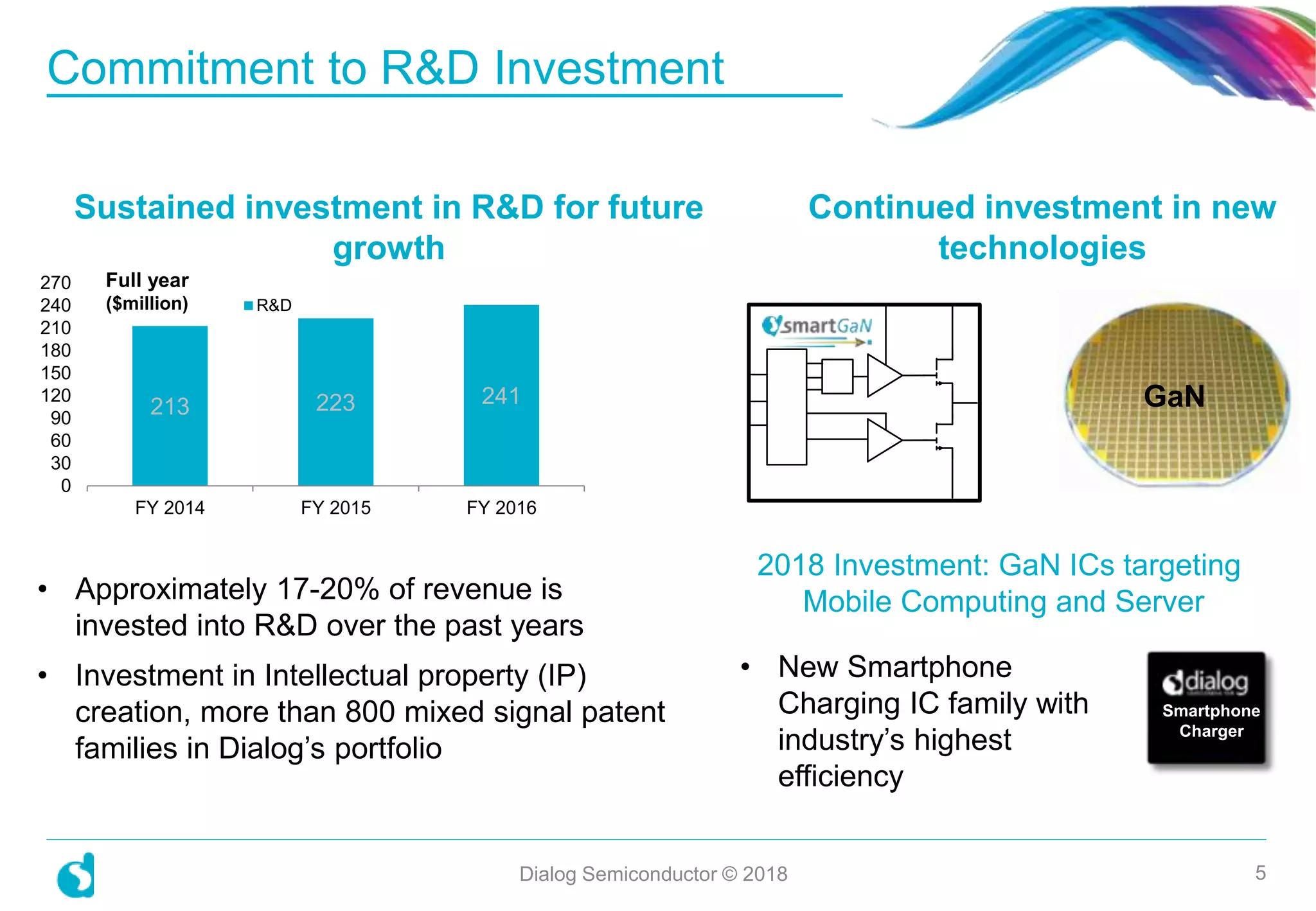

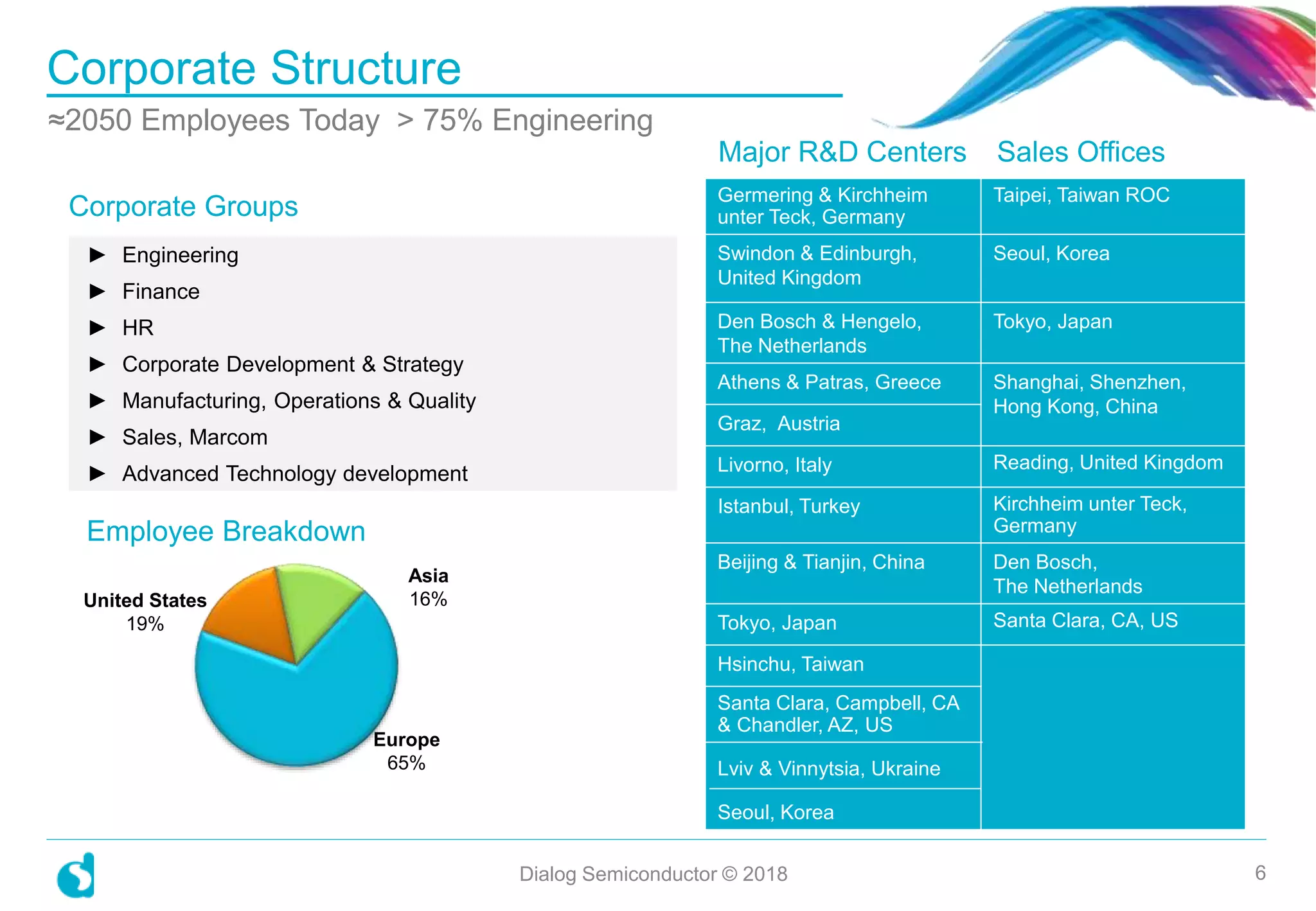

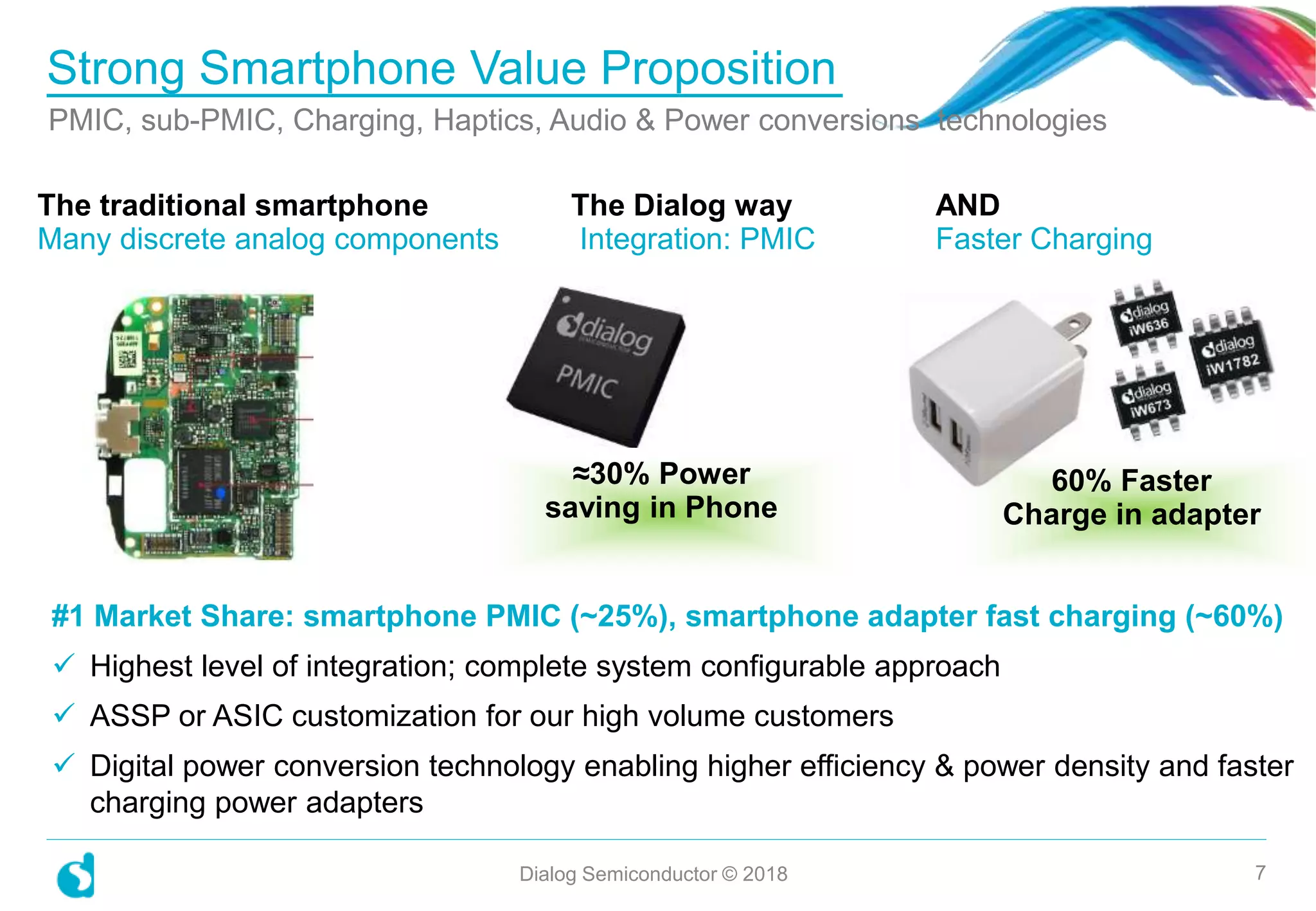

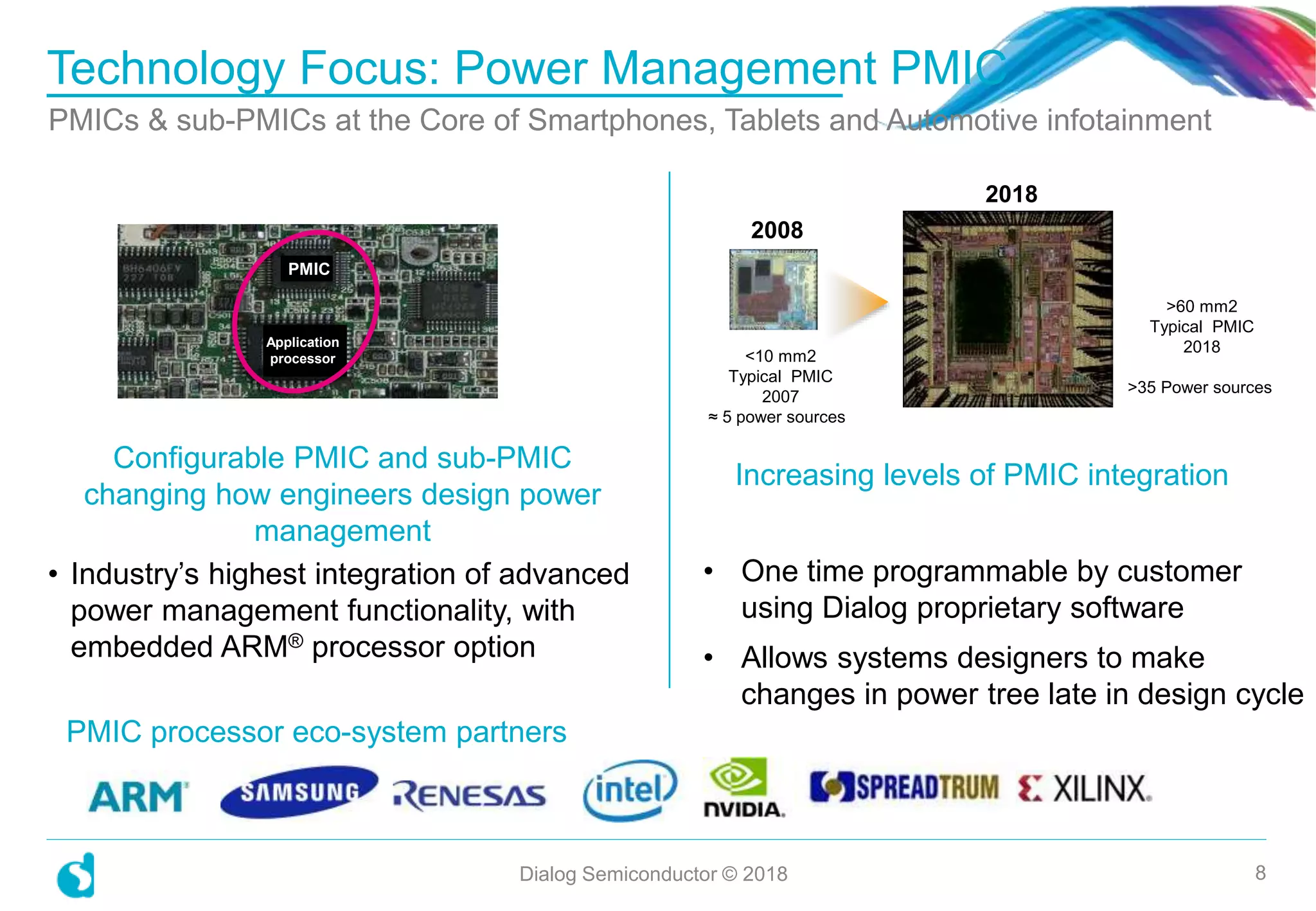

Dialog Semiconductor is a fabless semiconductor company specializing in power management, charging, audio, and wireless technologies. It has over 2,000 employees worldwide and is a market leader in power management ICs for smartphones, Bluetooth low energy chips, and fast charging technologies. The presentation provided an overview of Dialog's business, technology focus areas, growth strategy through R&D investment, and global corporate structure.