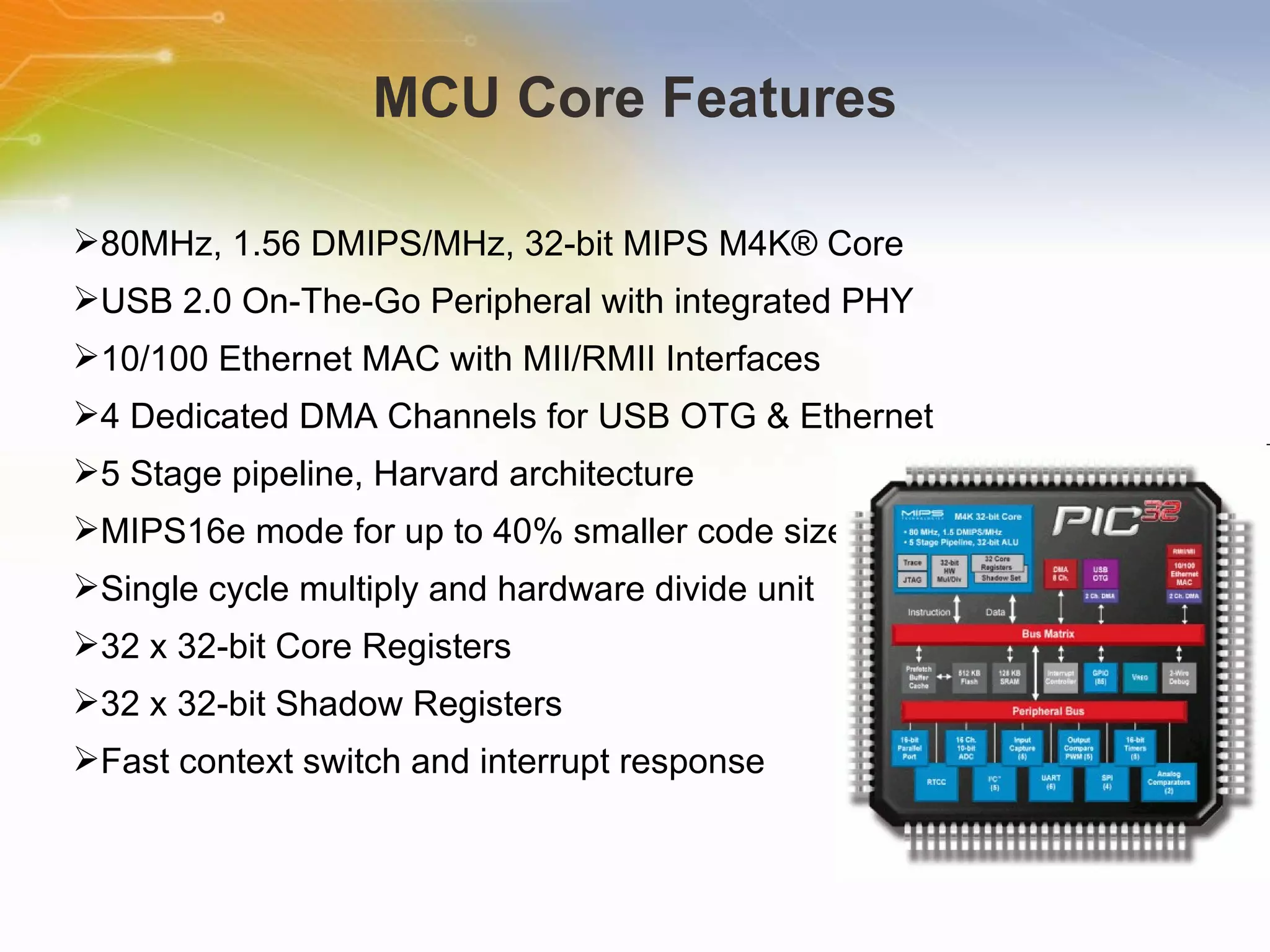

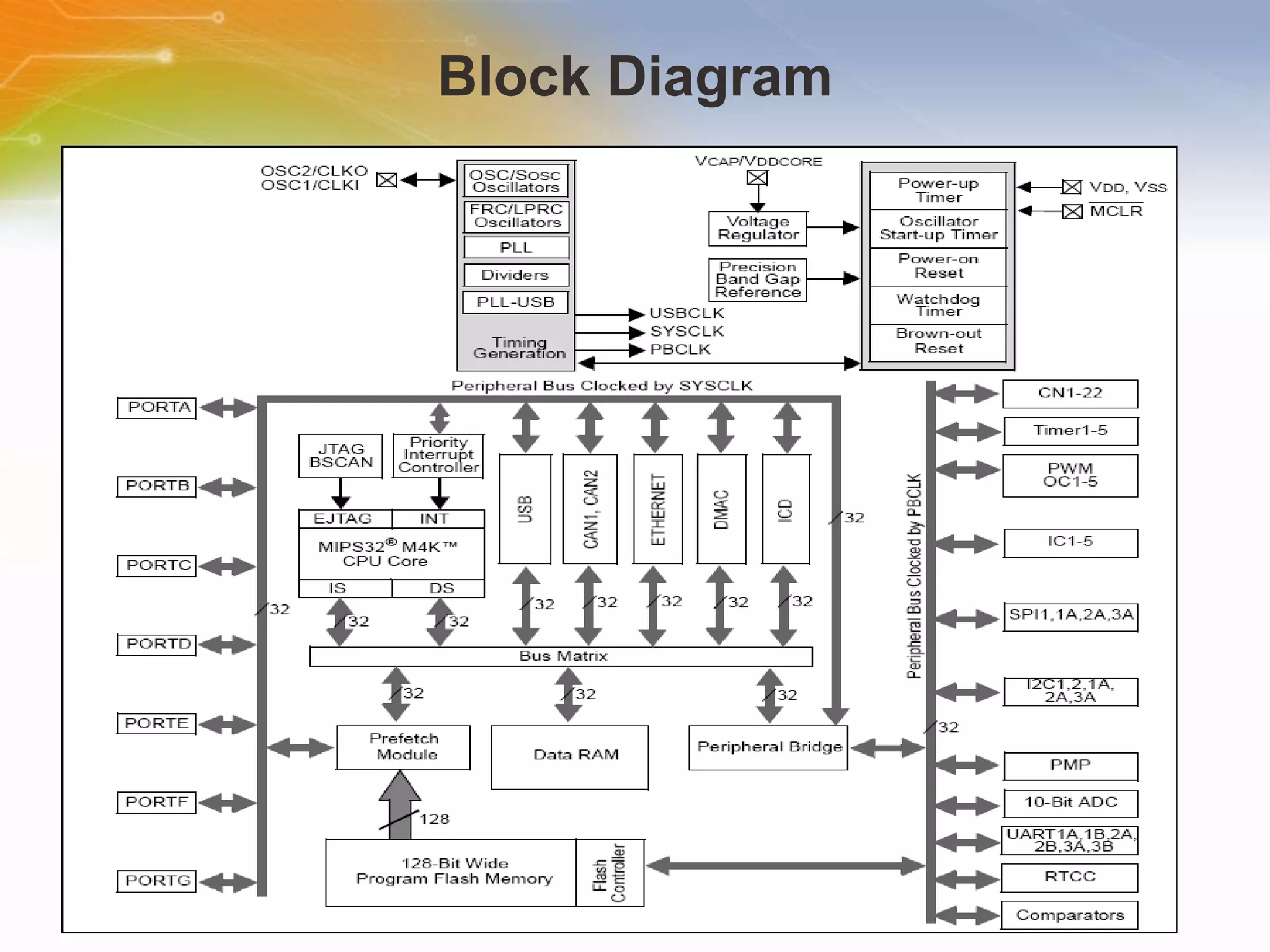

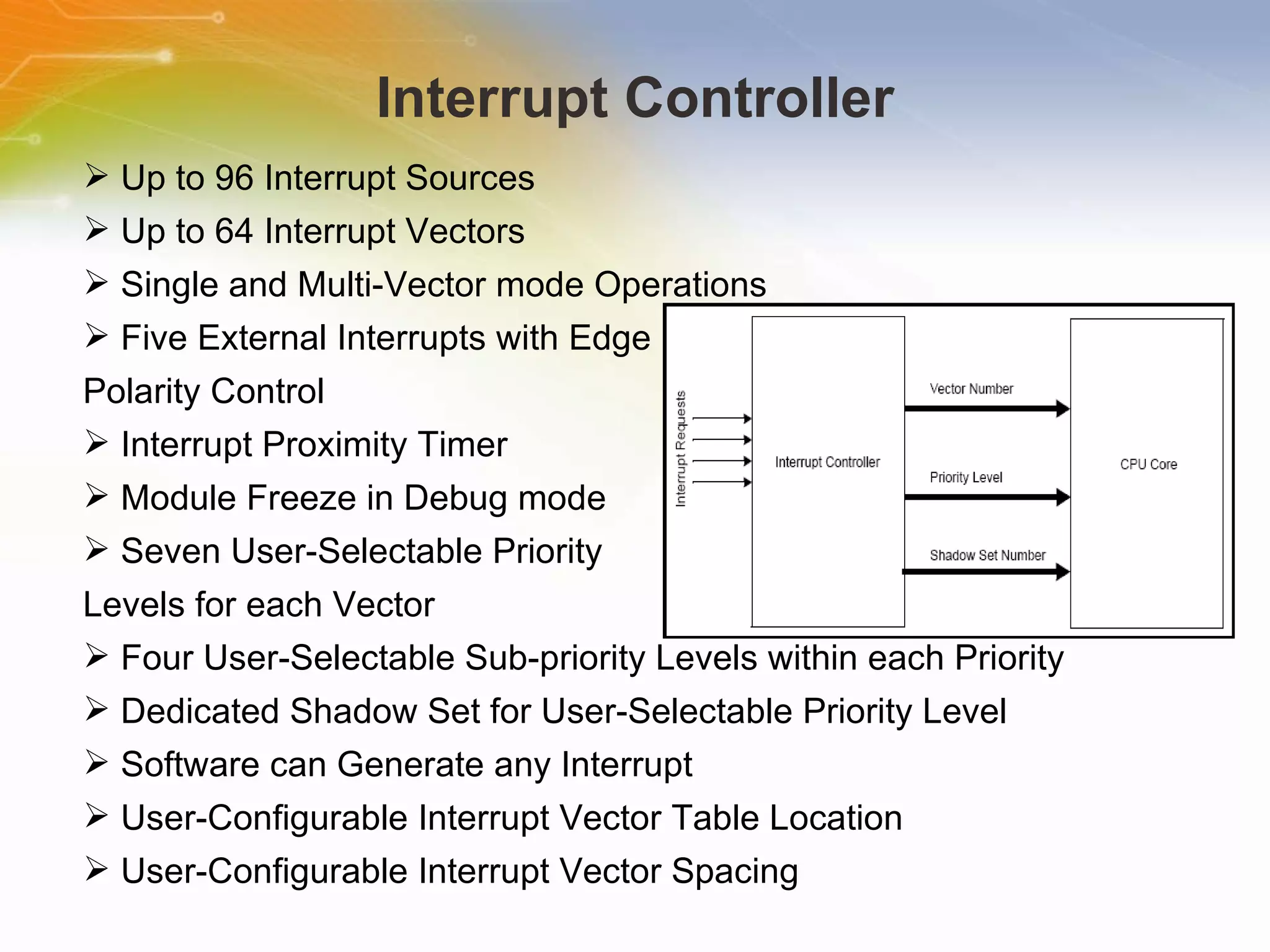

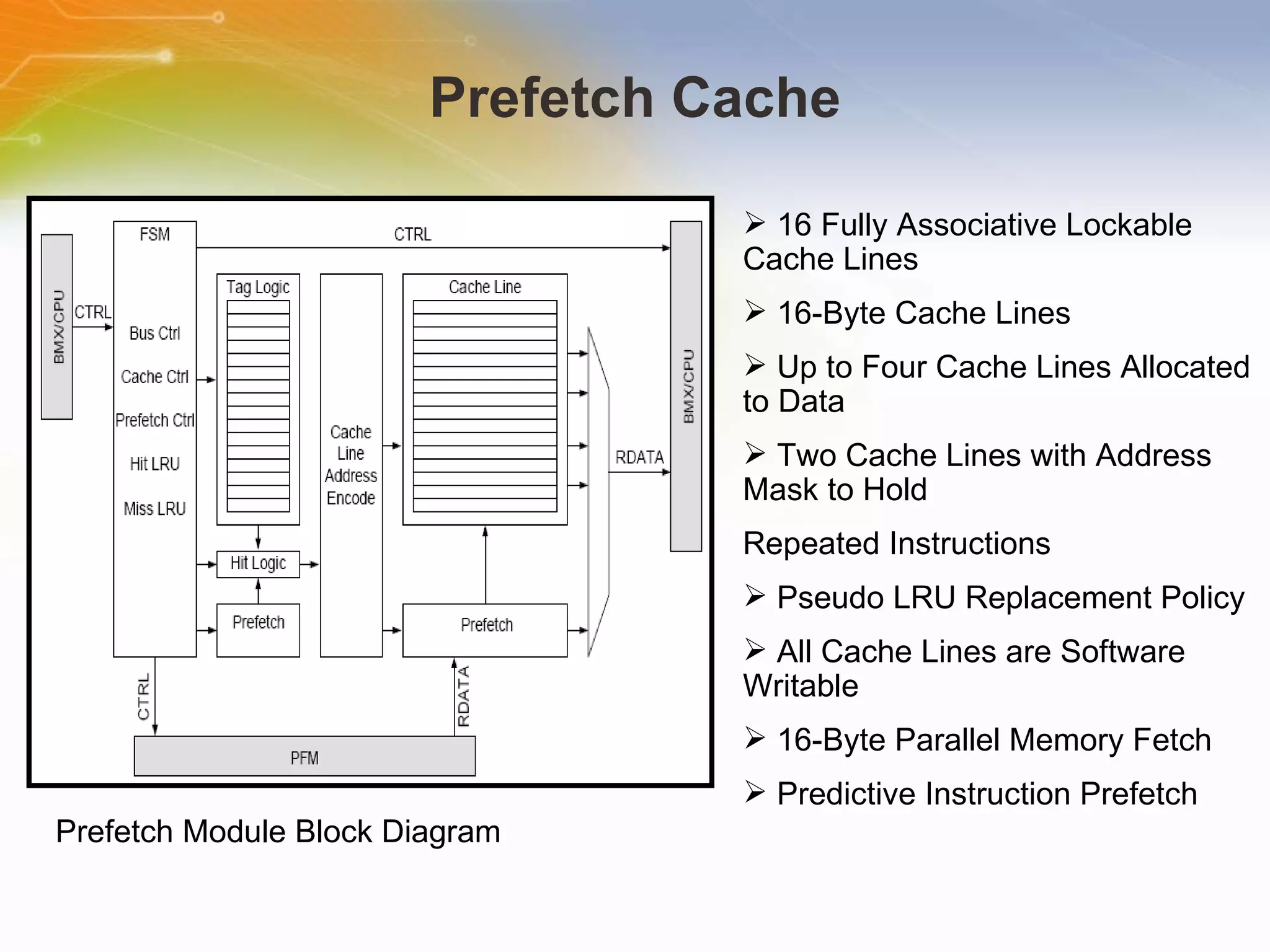

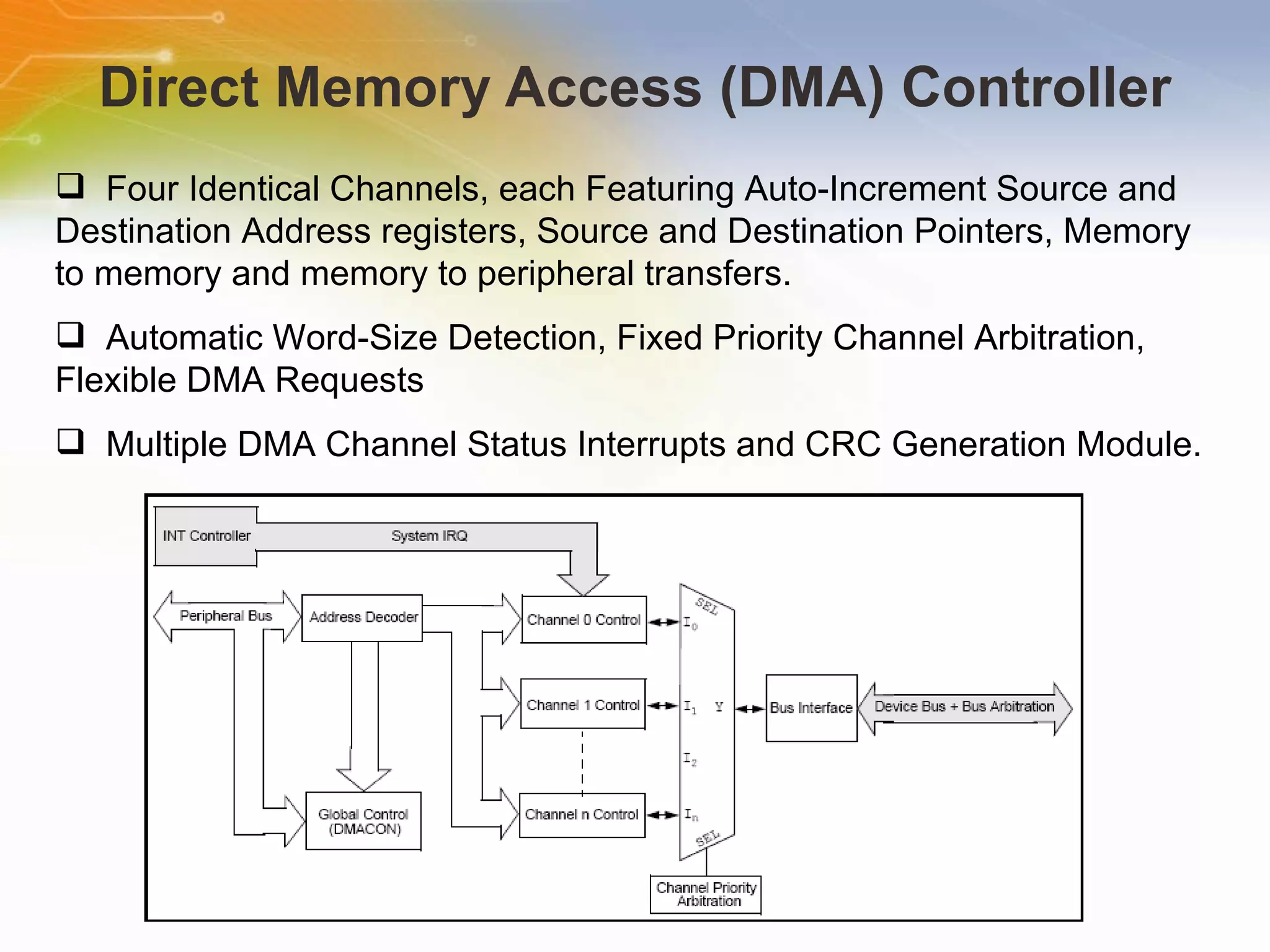

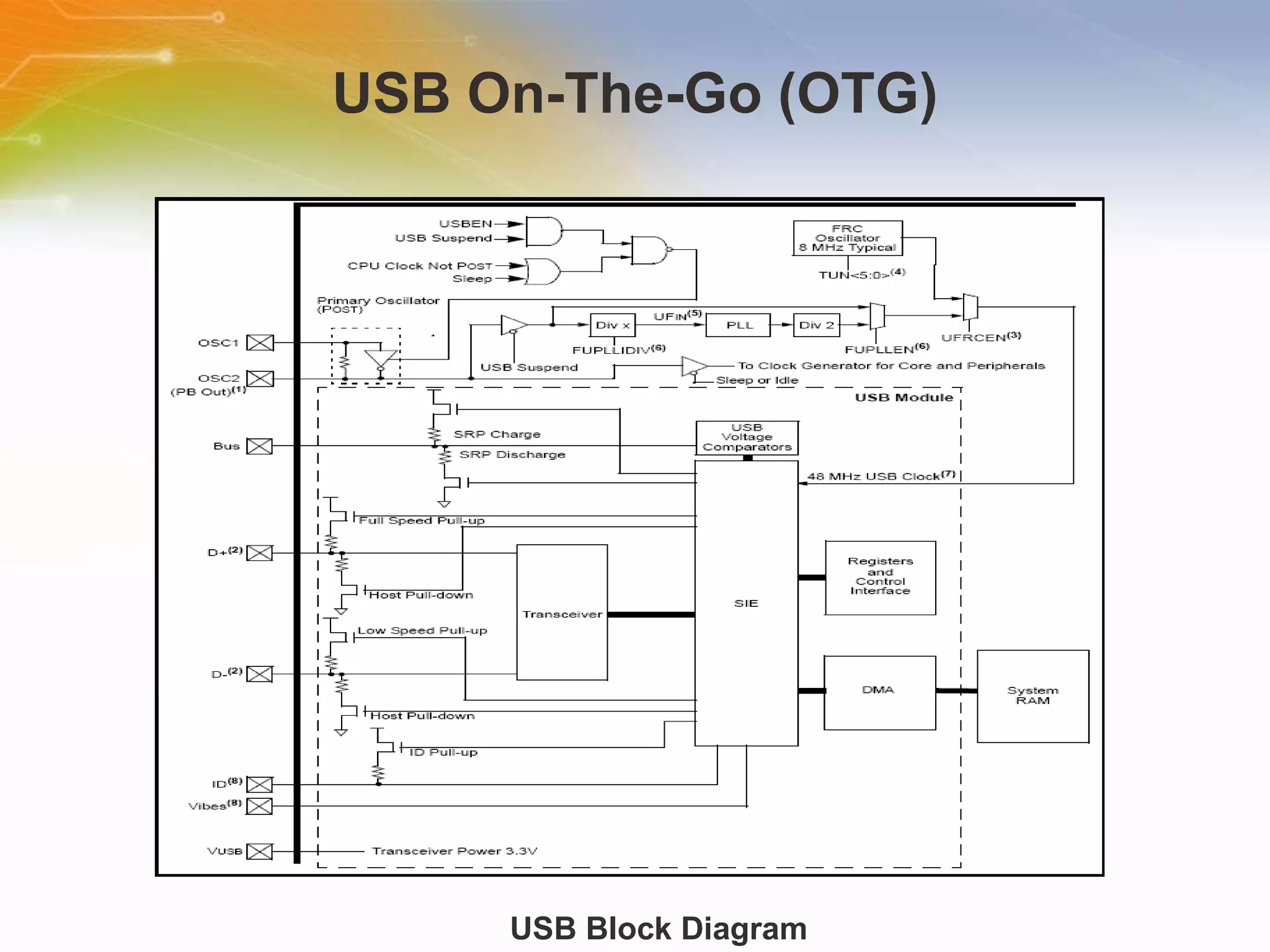

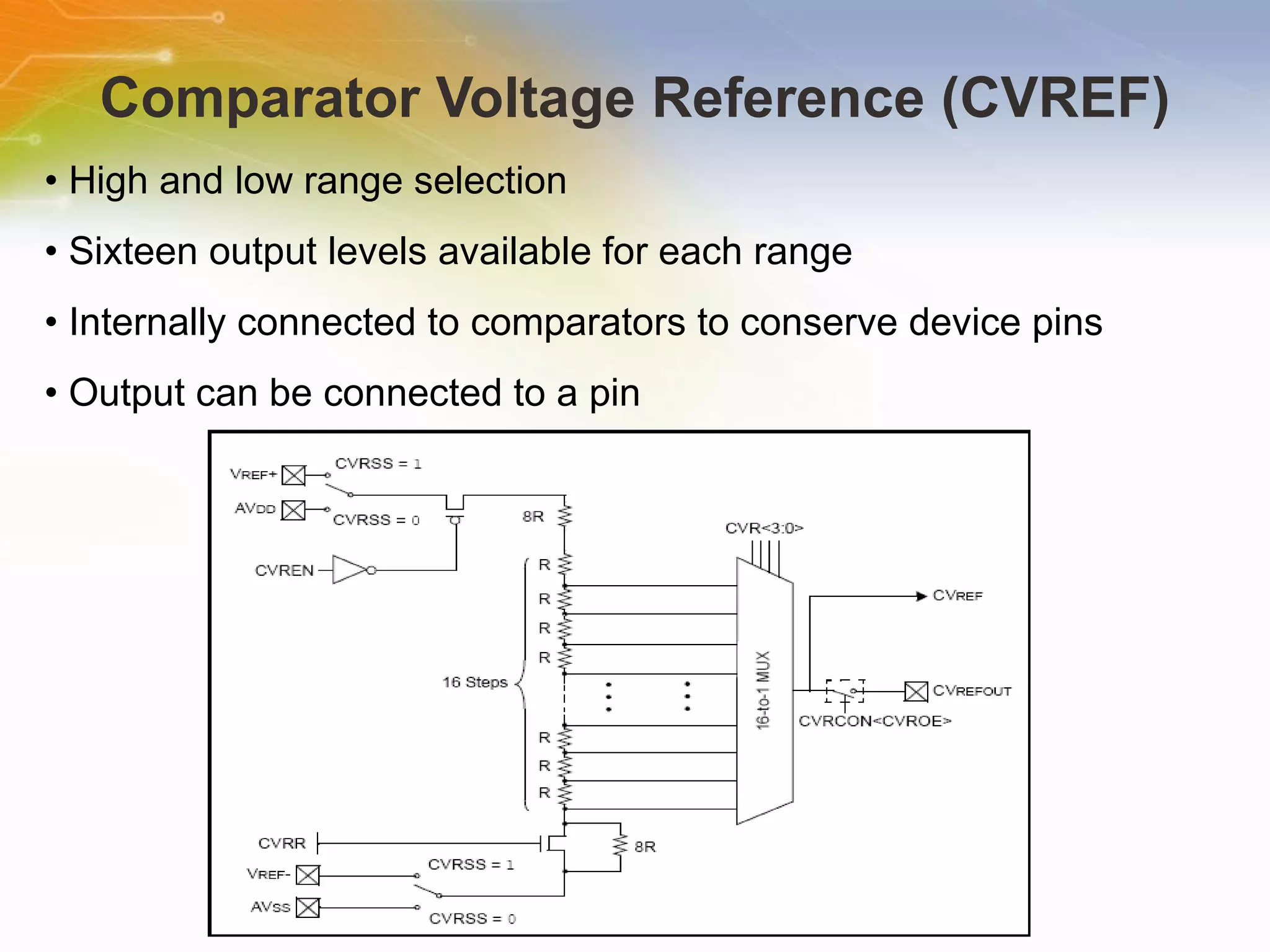

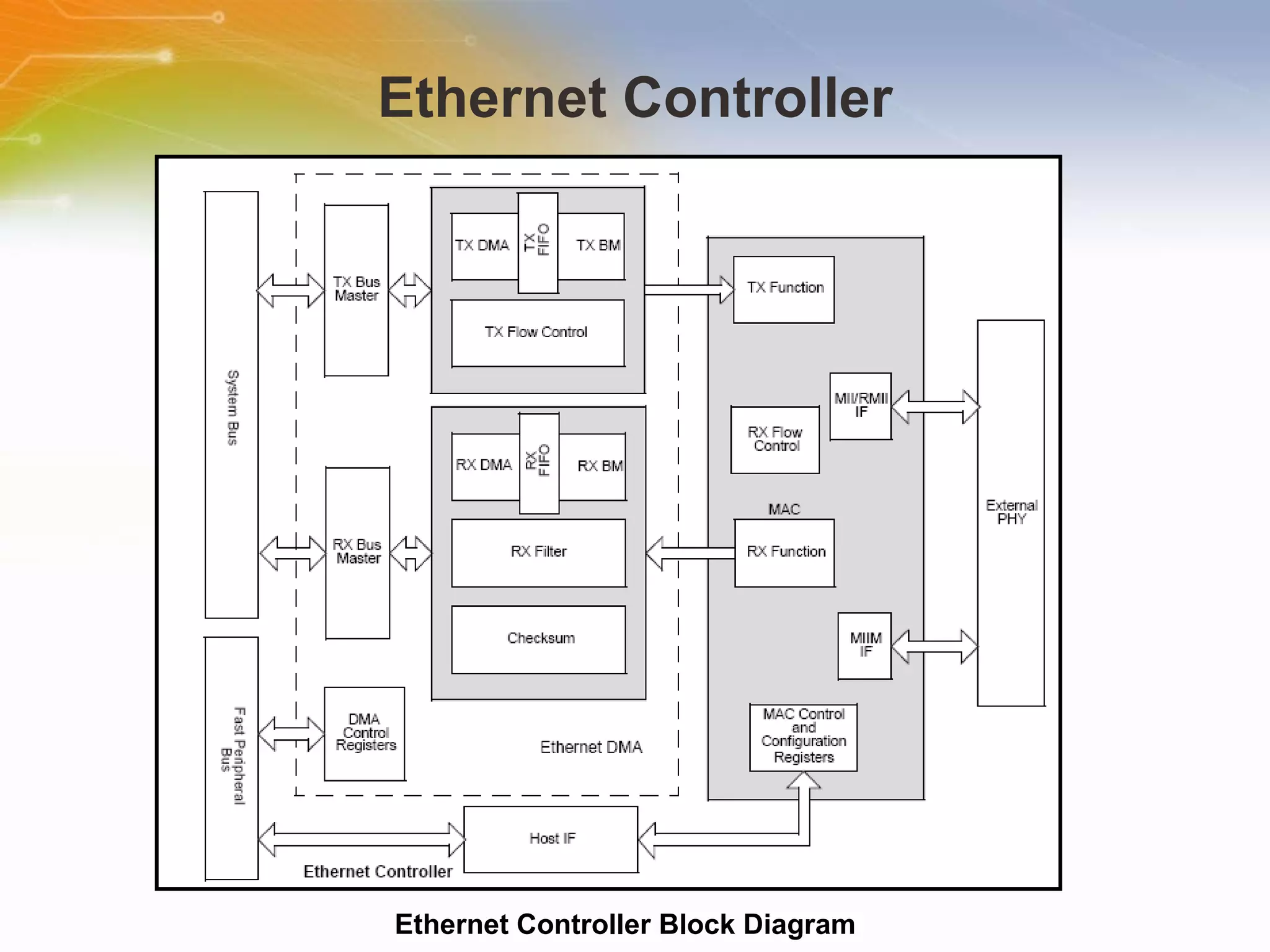

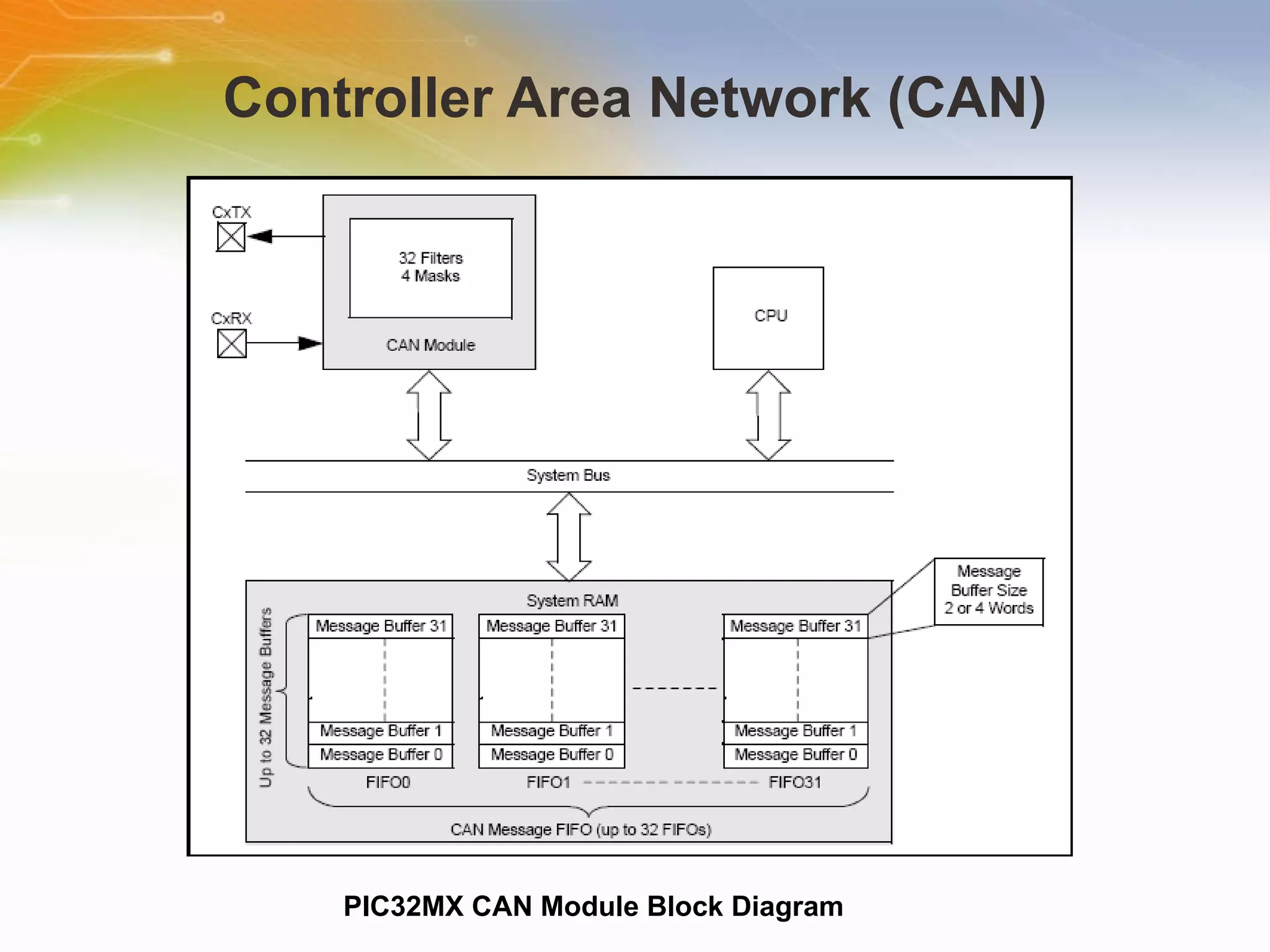

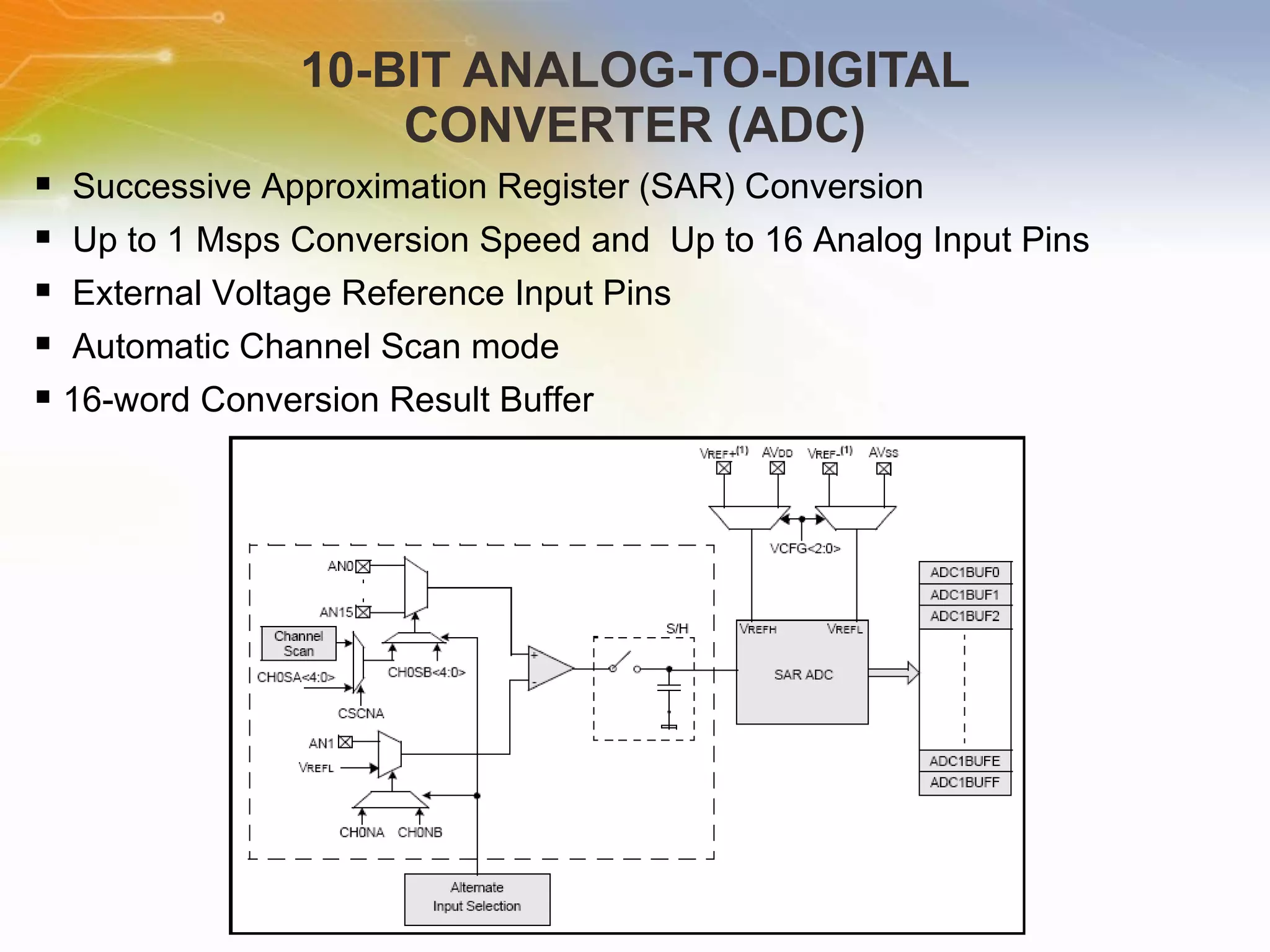

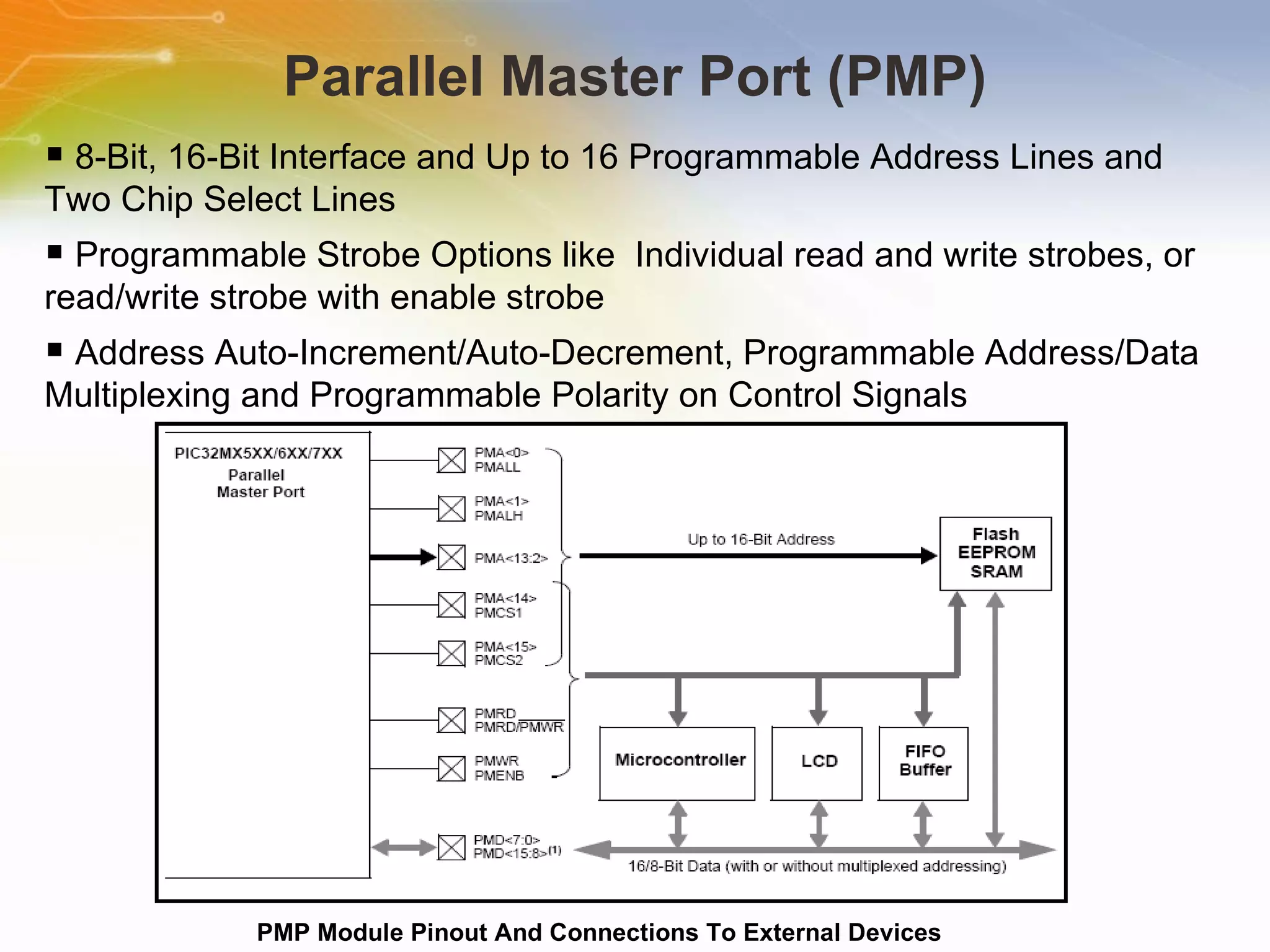

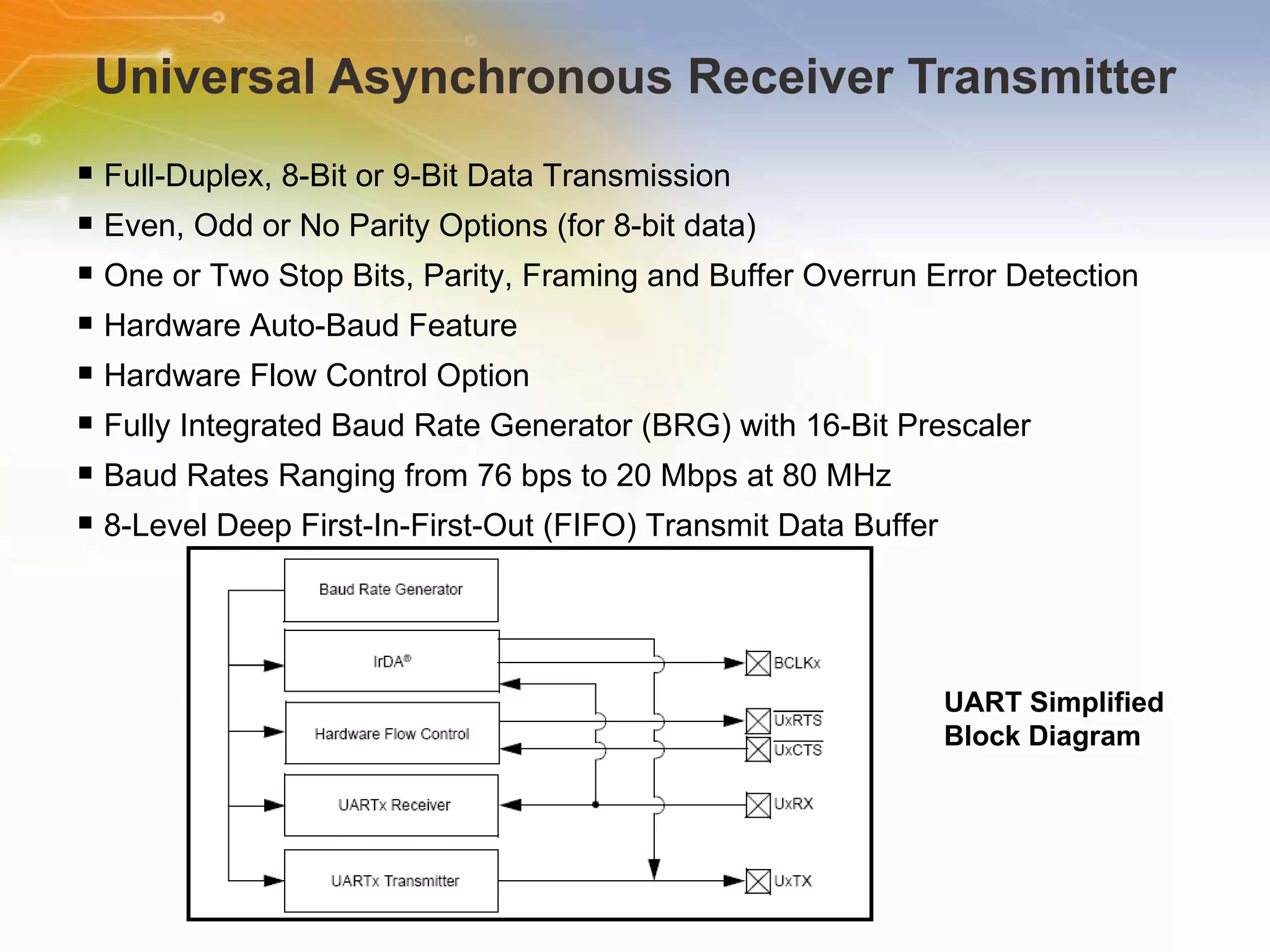

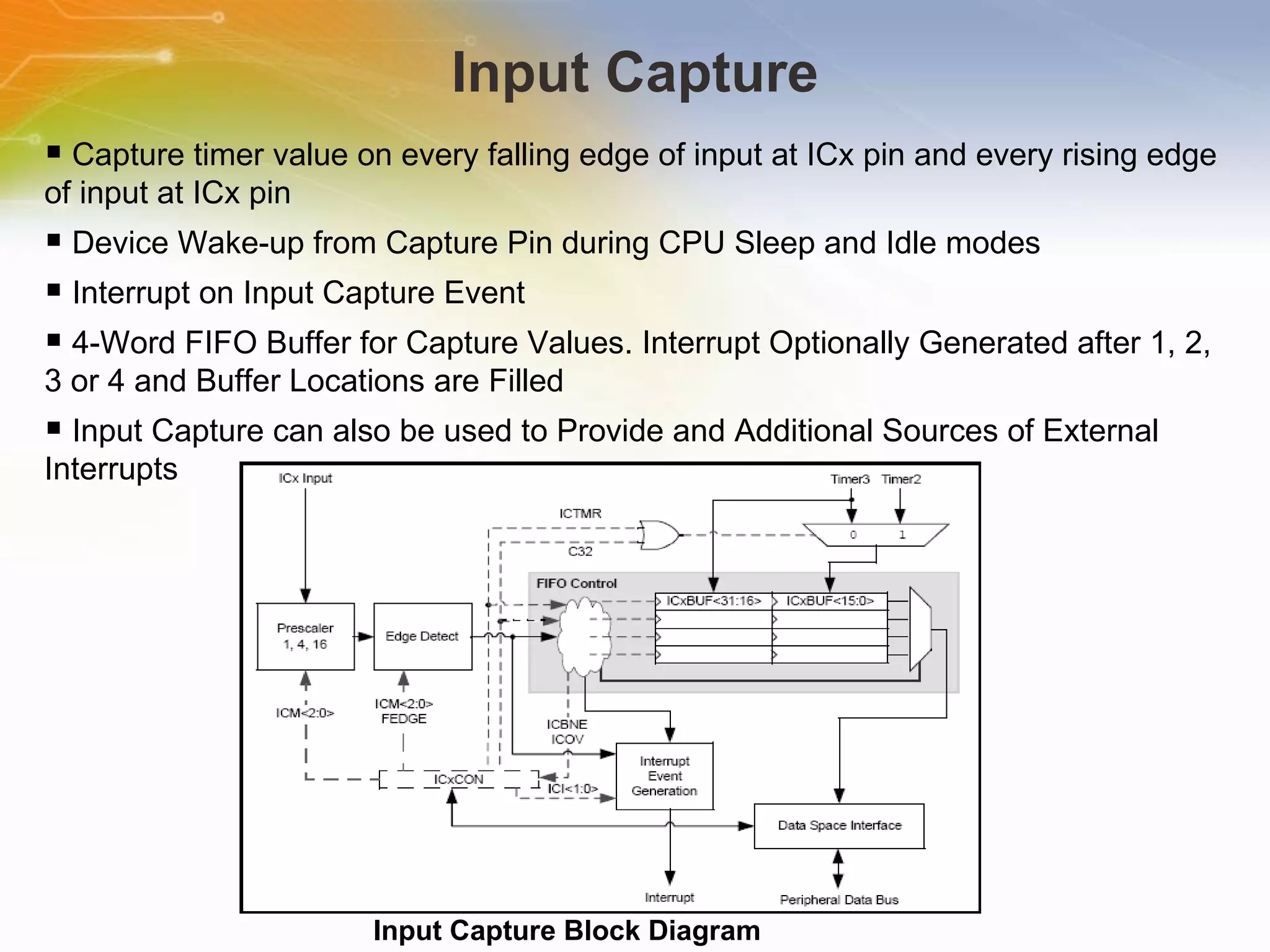

The document provides an overview of Microchip's PIC32MX5XX/6XX/7XX 32-bit flash microcontrollers. It describes the MCU's core features such as its 80MHz MIPS processor, USB 2.0 and Ethernet interfaces. It also summarizes the device's memory organization, interrupt controller, prefetch cache, DMA and various peripherals including ADC, UART, CAN and more. The 18-page document provides block diagrams and descriptions of the features to help familiarize users with the microcontroller family.