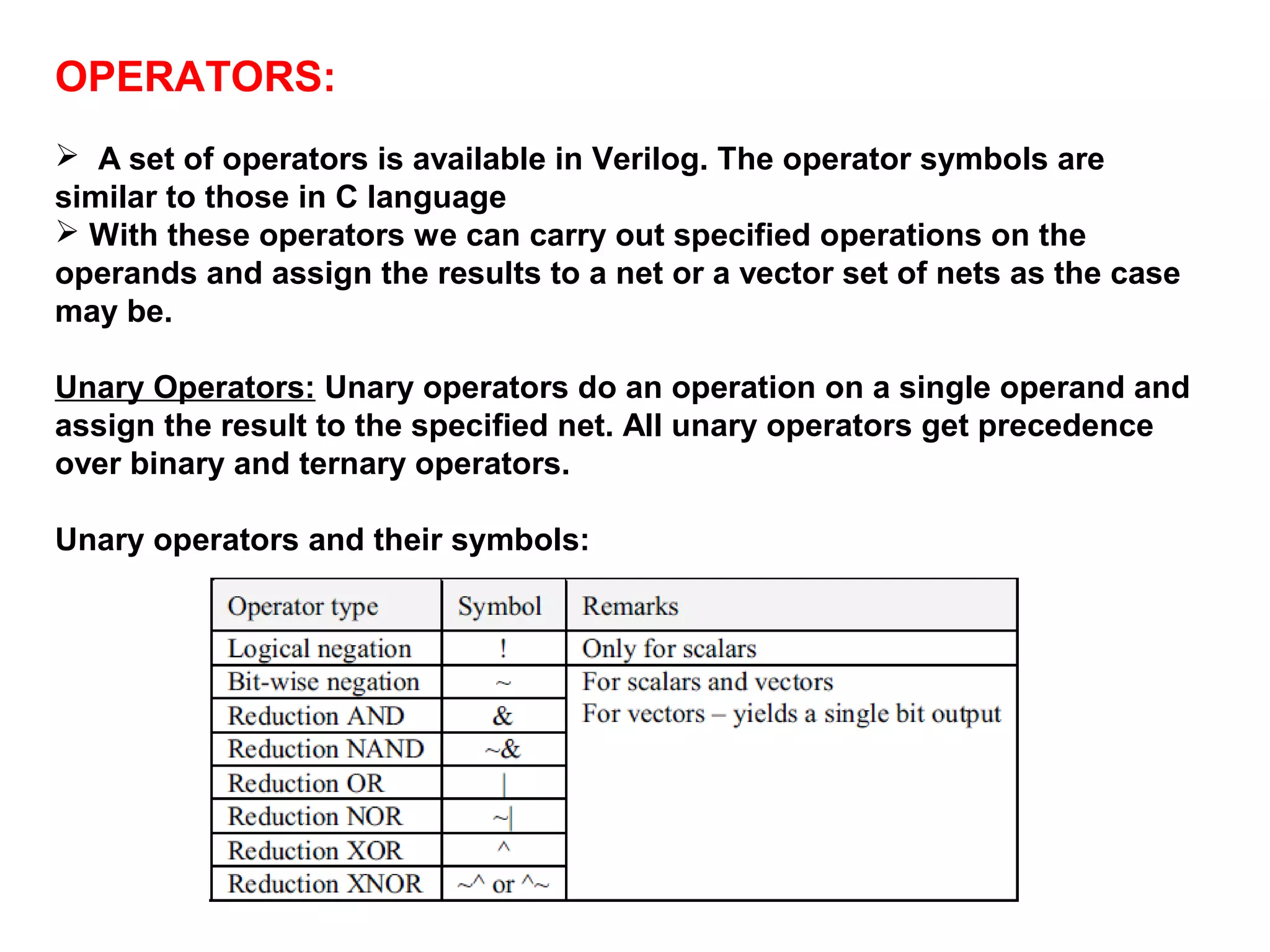

The document discusses various operators in Verilog including unary, binary, arithmetic, logical, relational, equality, bitwise logical, shift, and ternary operators. It provides examples of how each operator works and precedence rules. Unary operators operate on a single operand, binary operators take two operands, and the ternary operator checks a condition and branches accordingly. Operator precedence is also covered, noting that parentheses can be used to override the default precedence when needed.

![Arithmetic operators:

The modulus operand is similar to that in C language – It provides

the remainder of the division of two numbers.

Example:

module add_8(a,b,c);

input[7:0]a,b;

output[7:0]c;

assign c = a + b ; // indication of arithmetic binary operator for

//addition

endmodule](https://image.slidesharecdn.com/operators-140917230056-phpapp01/75/Operators-4-2048.jpg)

![Shift Operators contd..:

the shift operation shifts left operand by the right

operand number of times. It is a logical shift .The

vacated bits are filled with 0 , if the right operand

evaluates to an x or z, the result of the shift operation

is an x.

reg[0:7] Qreg;

Qreg= 4’b0111;

qreg >> 2 is 8’b0000_0001](https://image.slidesharecdn.com/operators-140917230056-phpapp01/75/Operators-16-2048.jpg)

![Conditional operator contd…

cond_expr ? expr1:expr2

If cond_expr is true (that is ,has a value 1), expr 1 is selected, if cond_expr

is false (value 0) , expr2 is selected.

if cond_expr is an x or a z , the result is a bitwise operation on expr1 and

expr2 with the following logic: 0 with 0 gives 0, 1 with gives 1, rest are x.

here is an example

wire [0:2] student = marks >18 ? Grade_A : grade_c;

the expression marks > 18 is computed ; if true , Grade_A is assighned to

student , if marks <=18 , grade_C is assighed to student

Another example

always

#5 ctr = (ctr!=25) ? (ctr+1) : 5;

The expression in the procedural assignment says that if ctr is not equal to

25 increment ctr, else if ctr becomes 25, reset to 5.](https://image.slidesharecdn.com/operators-140917230056-phpapp01/75/Operators-18-2048.jpg)