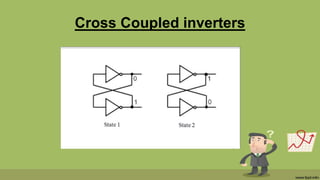

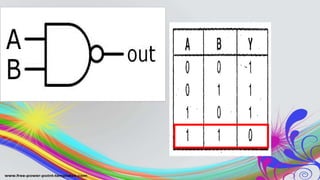

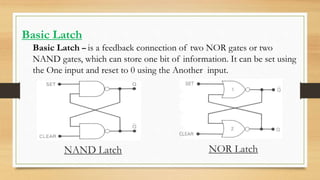

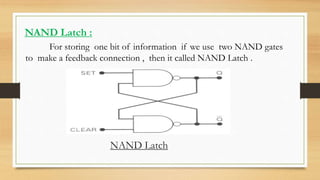

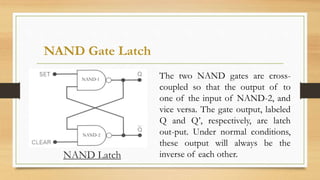

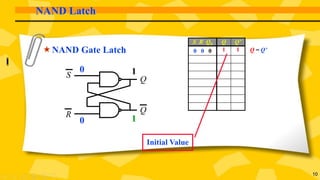

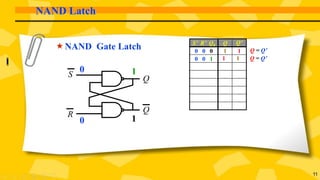

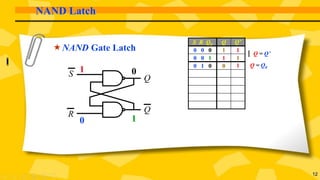

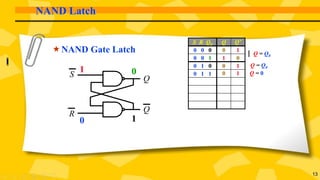

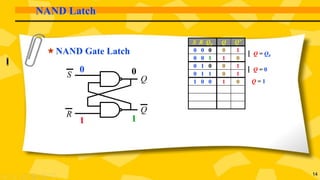

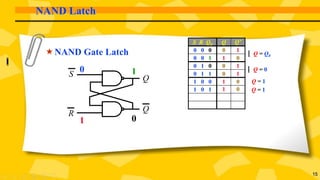

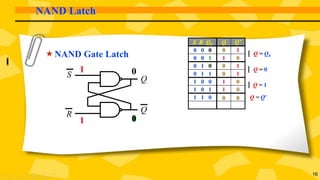

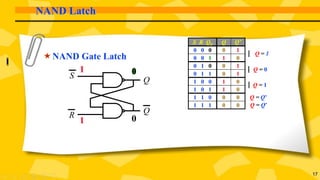

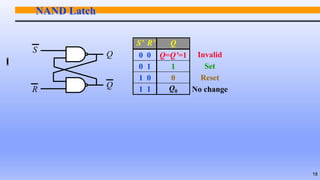

The document discusses a NAND latch, which is a type of sequential logic circuit that can store one bit of information. It consists of two cross-coupled NAND gates that provide feedback to each other. The state of the latch's output Q is determined by the previous inputs and state, not just the current inputs. The NAND latch can be set to 1 by applying a 1 to the S input and reset to 0 by a 1 on the R input. It will maintain its output state as long as neither input is active.