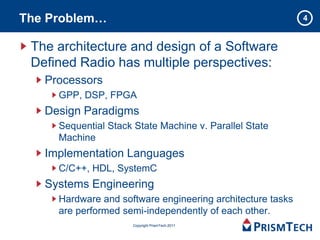

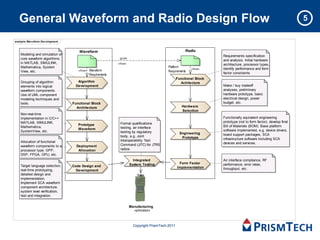

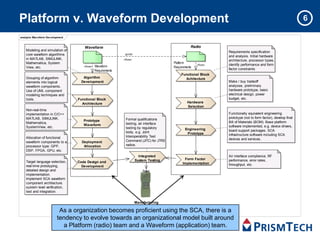

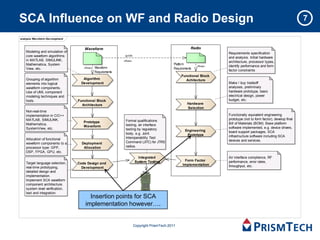

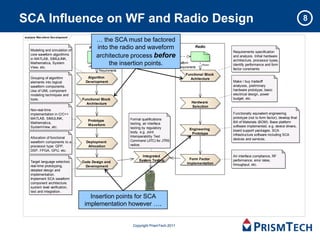

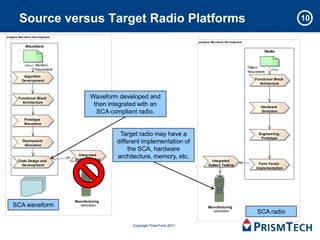

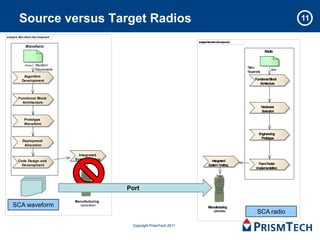

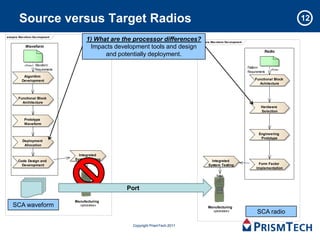

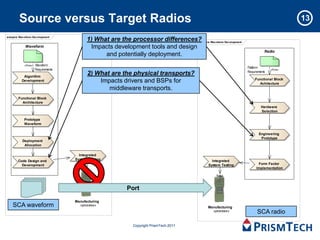

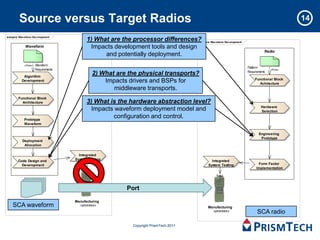

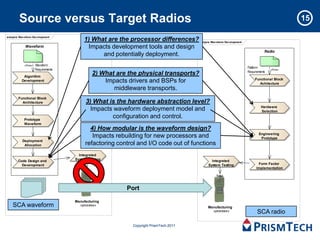

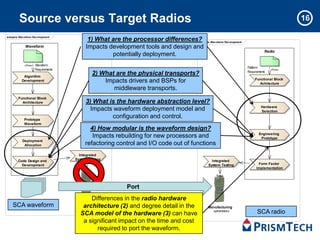

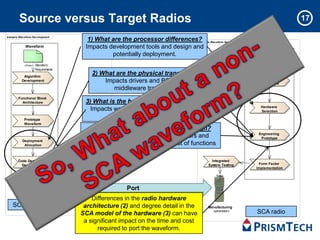

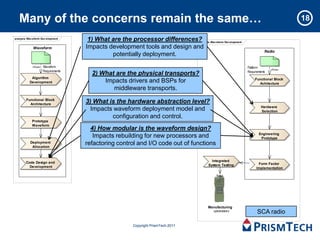

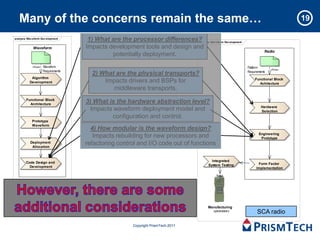

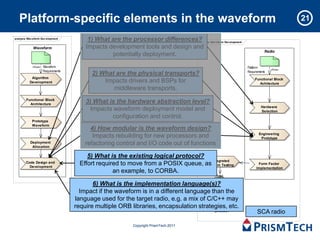

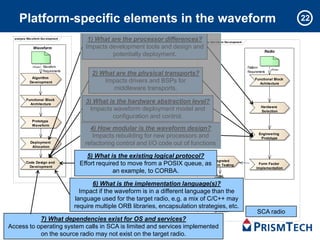

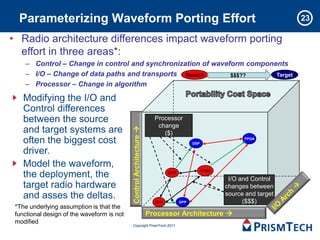

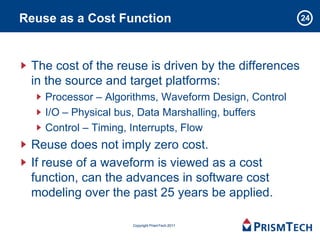

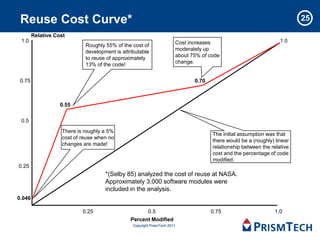

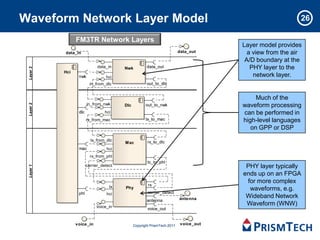

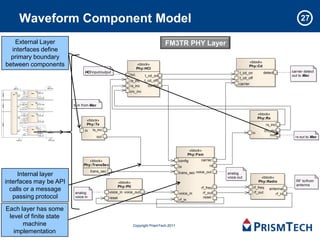

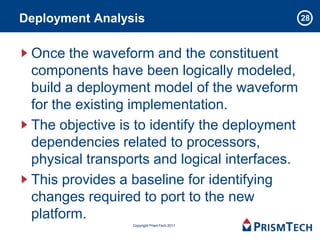

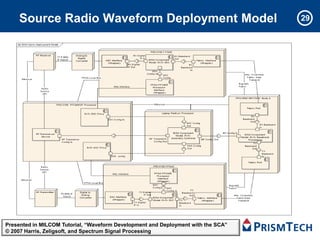

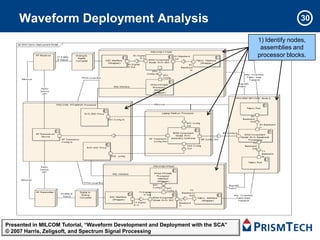

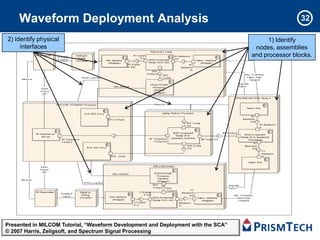

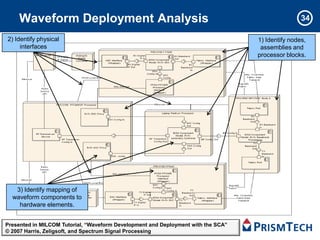

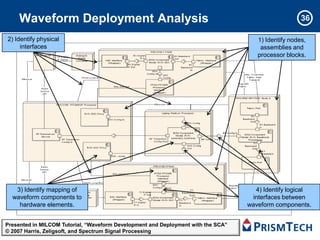

The document discusses the challenges and processes involved in migrating legacy waveforms to the Software Communications Architecture (SCA) for Software Defined Radios. It highlights the complexities of porting non-SCA compliant waveforms, discusses the relationship between architecture and design across different implementation platforms, and emphasizes the need for modular design and adherence to SCA standards to promote waveform portability. Ultimately, successful migration requires thorough analysis of processor differences, hardware abstraction levels, and existing logical protocols.