JD Role Type Slides - 12.2022.pdf

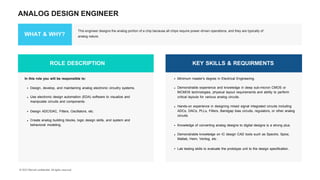

- 1. ANALOG DESIGN ENGINEER This engineer designs the analog portion of a chip because all chips require power-driven operations, and they are typically of analog nature. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Design, develop, and maintaining analog electronic circuitry systems. Use electronic design automation (EDA) software to visualize and manipulate circuits and components. Design ADC/DAC, Filters, Oscillators, etc. Create analog building blocks, logic design skills, and system and behavioral modeling. In this role you will be responsible to: Minimum master's degree in Electrical Engineering. Demonstrable experience and knowledge in deep sub-micron CMOS or BiCMOS technologies, physical layout requirements and ability to perform critical layouts for various analog circuits. Hands-on experience in designing mixed signal integrated circuits including ADCs, DACs, PLLs, Filters, Bandgap bias circuits, regulators, or other analog circuits. Knowledge of converting analog designs to digital designs is a strong plus. Demonstrable knowledge on IC design CAD tools such as Spectre, Spice, Matlab, Hsim, Verilog, etc . Lab testing skills to evaluate the prototype unit to the design specification.

- 2. DIGITAL DESIGN ENGINEER This engineer designs the digital logic of a chip because in the complex products that we make, we require complex digital blocks. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Contribute to the development of one or more Co-processor units, industry standard, high-speed serial bus interfaces for Marvell’s next generation Multi-core embedded ARM processor family targeted at Networking, Storage, Security, and Wireless applications in the state-of-the-art deep sub-micron CMOS process technologies. Write specifications for the relevant block, micro-architecture of the block, design implementation using RTL coding techniques, Synthesis, place & route and timing sign off. Shape the micro-architecture of the chip. Review the verification test plan, coverage analysis and full chip simulation plus debug. In this role you will be responsible to: Electrical/ Computer Engineering or similar disciplines. Knowledge of scripting languages such as Perl/Python Tcl and UNIX shell etc. is desirable. RTL design experience, Synthesis static timing closure, formal verification, gate-level simulations, and block-level function verification. Experience in designing low power, high-speed (>1 GHz), and high- performance ASICs / SOCs.

- 3. DESIGN VERIFICATION ENGINEER The verification team checks the analog and digital logic design for bugs to ensure that the chips work as intended and reduce reparation costs later down the line. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Use industry standard design verification tools and processes such as Verilog/System Verilog, UVM and C programming to verify System on a Chip (SoC) designs. Develop simulation test environment and components such as test benches, checkers and monitors. Use problem solving and critical thinking skills to develop verification test vectors, debug failing simulations and analyze test coverage. Perform automation of data collection and analysis using Python or other scripting languages. Work closely with the design team to ensure best-in-class quality designs that meet our customer requirements. Design, develop, and verify very large high-speed integrated circuit products utilizing leading-edge IC process technology. In this role you will be responsible to: Electrical/ Computer Engineering or similar disciplines. Knowledge of scripting languages such as Perl/Python Tcl and UNIX shell etc. is desirable. RTL design experience, Synthesis static timing closure, formal verification, gate-level simulations, and block-level function verification. Experience in designing low power, high-speed (>1 GHz), and high-performance ASICs / SOCs.

- 4. PHYSICAL DESIGN ENGINEER Physical design is the process of turning a design into a geometric format that we can send to manufacturing. So that we can manufacture chips of specific sizes and performance for the allocated space provided by the customer. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Use industry standard tools in conjunction with developed flows to automate and streamline the overall place and route process. Develop floorplans at the full chip or hierarchical partition level. Execute place and route processes for all blocks at the full chip and hierarchical partition level. Integrate full chip physical data and run signoff quality and correctness checks. Check electromigration (EM), wire-level voltage drops (IR), timing and logical equivalency and correct as needed. In this role you will be responsible to: Minimum master's degree in Electrical Engineering. Knowledge of the following: Digital timing concepts, Scripting (TCL, Perl, Python), Digital logic synthesis, Linux/UNIX commands and shell scripting, HDLs (Hardware Design Languages) like Verilog or VHDL. Knowledge of SOC Design and STA flows is a plus. Familiarity with industry standard EDA tools from Cadence, Synopsys, and/or Mentor. Experience working in a Unix type environment. Ability to work with an international team. Good verbal and written communication skills. Strong problem solving and critical thinking skills.

- 5. VALIDATION ENGINEER The validation team ensures that the product is doing what we designed it to do. This is because manufacturing and/or design defects can cause hardware not to function and be very expensive to redesign the chip. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Test the physical hardware of the chip. Primary job function includes but not limited to develop and execute bench level validation test plans, develop scripts to automate testing, customer support, generate appropriate test report and write application notes. Bring up, debug and characterization of silicon level Marvell IP such as High-Speed SerDes, USB, PLL/DLL, ADC, etc. in test vehicles and various Marvell products. Evaluate and debug new features in PHY, collect performance data, and resolve application/production issues, test to electrical qualifications such as IEEE802.3 and PCIe products . Support internal SoC customers, Field engineers and the ATE team on testing and system level debugging. Provide direct technical support to top tier customers and work with them to review designs, discuss questions and help tune performance to meet system requirement. Work with IP design and architecture teams to help define new features and design new products. In this role you will be responsible to: Minimum bachelor's degree in electrical engineering or computer science. Experience in pre/post silicon validation, stress testing, and various scripting languages. Hardware, software, and systems experience. Hands-on experience – tinkering with boards, wires, etc. Strong C/C++ SW development skills, a good understanding of embedded SW development, and basic knowledge of micro-processor or SOC architecture. Strong knowledge of the NVMe protocol and the PCIe standard with a proven track record of executing bench validation with NVMe over PCIe. Knowledge of UFS, SAS, SATA is a plus. Hands on experience with embedded SW development and debug. Experience in HDD, flash, semiconductor, components, nonvolatile memory industry is a plus. Experienced in using typical lab tools: Emulators, Oscilloscopes, Logic Analyzers.

- 6. FIRMWARE ENGINEER Firmware is the software that is hard coded and runs the hardware that we manufacture. Firmware enables the hardware to do what it was intended/designed for and cannot be altered at discretion. WHAT & WHY? ROLE DESCRIPTION KEY SKILLS & REQUIRMENTS Contribute to design, implementation, verification, and customer support. Potentially contribute in the following domains: PCle/NVMe/SATA, NANO, caching, performance, FTL, infrastructure, and manufacturing. Interact with different teams such as Soc design, Soc validation, SQA, Field Application Engineers as well as customers. In this role you will be responsible to: Software engineering background: Minimum bachelor's degree in Computer Science. Programming experience in C language. Knowledge in embedded firmware, programming and its concepts. Knowledge in processor architectures, specifically ARM. Strong communication skills in English. Agile development.