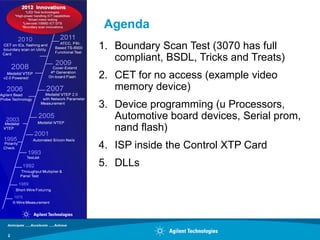

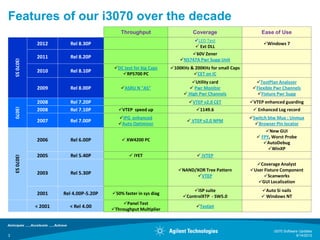

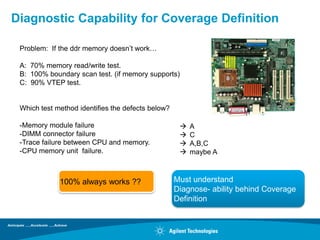

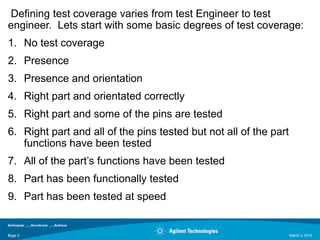

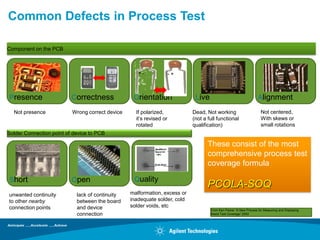

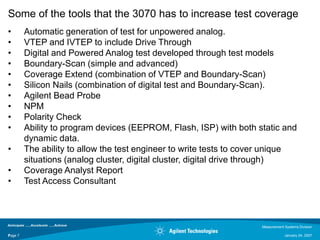

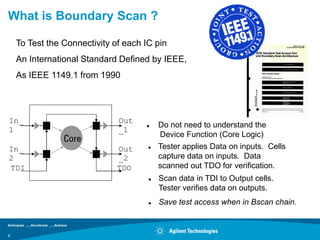

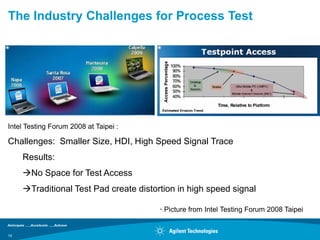

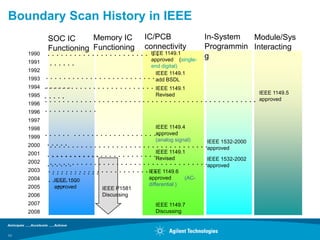

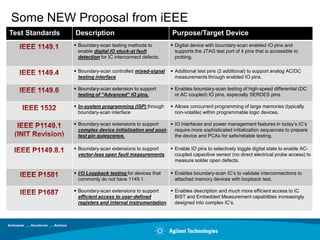

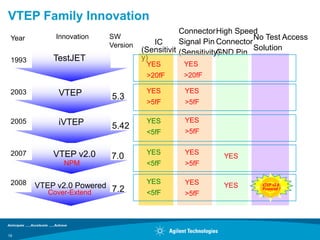

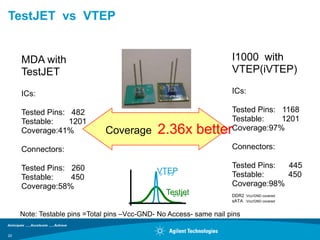

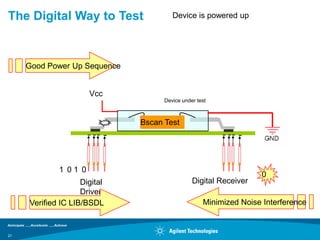

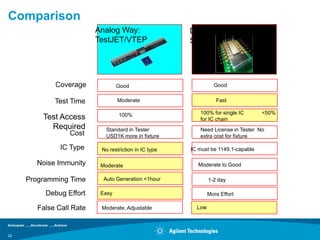

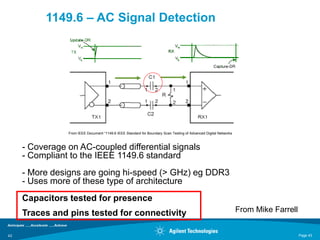

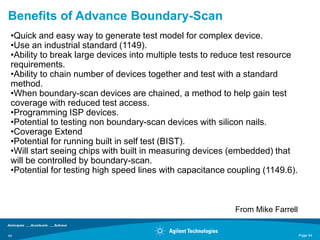

This document discusses improving test coverage using the Agilent 3070 test system. It provides an overview of boundary scan testing and its benefits for testing interconnects without understanding device functionality. It also discusses various tools and techniques the 3070 uses to increase coverage, such as coverage extend combining boundary scan and VTEP testing. The document outlines definitions of different levels of test coverage and common defects tested at each level. It provides a brief history of boundary scan standards and some proposed new extensions. Overall, the document aims to help test engineers understand how to maximize coverage using the capabilities of the 3070.