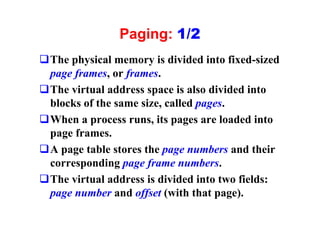

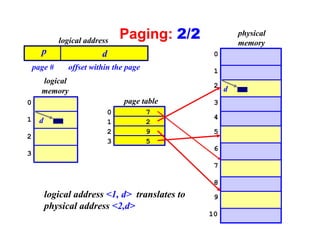

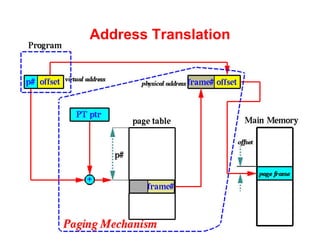

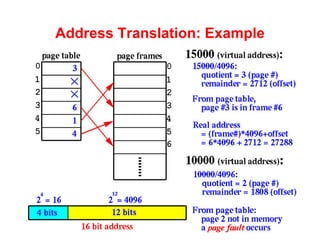

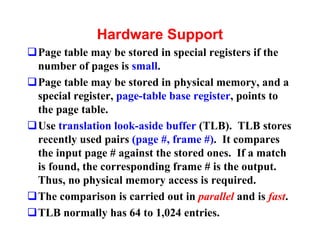

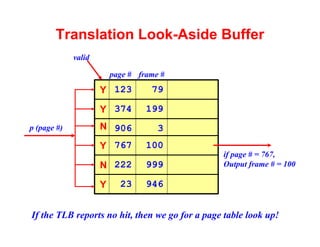

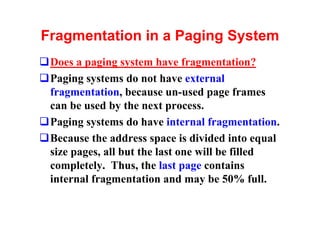

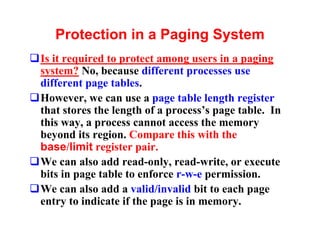

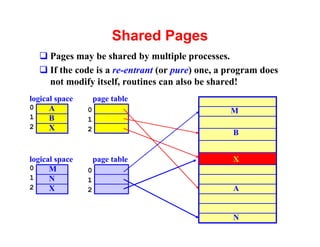

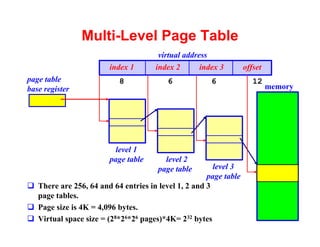

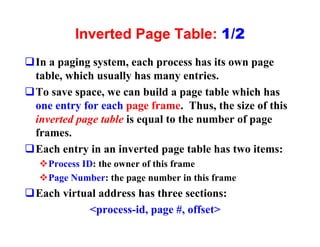

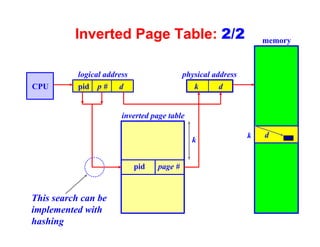

The document discusses address translation in computer systems using paging. It explains that with paging, the virtual address space is divided into pages, and physical memory is divided into page frames. A page table maps pages to frames. The page table can be stored in memory and pointed to by a page table base register. Hardware support for fast translation includes a translation lookaside buffer (TLB) that caches recent page-frame mappings. Paging allows sharing of pages between processes and provides memory protection between processes.