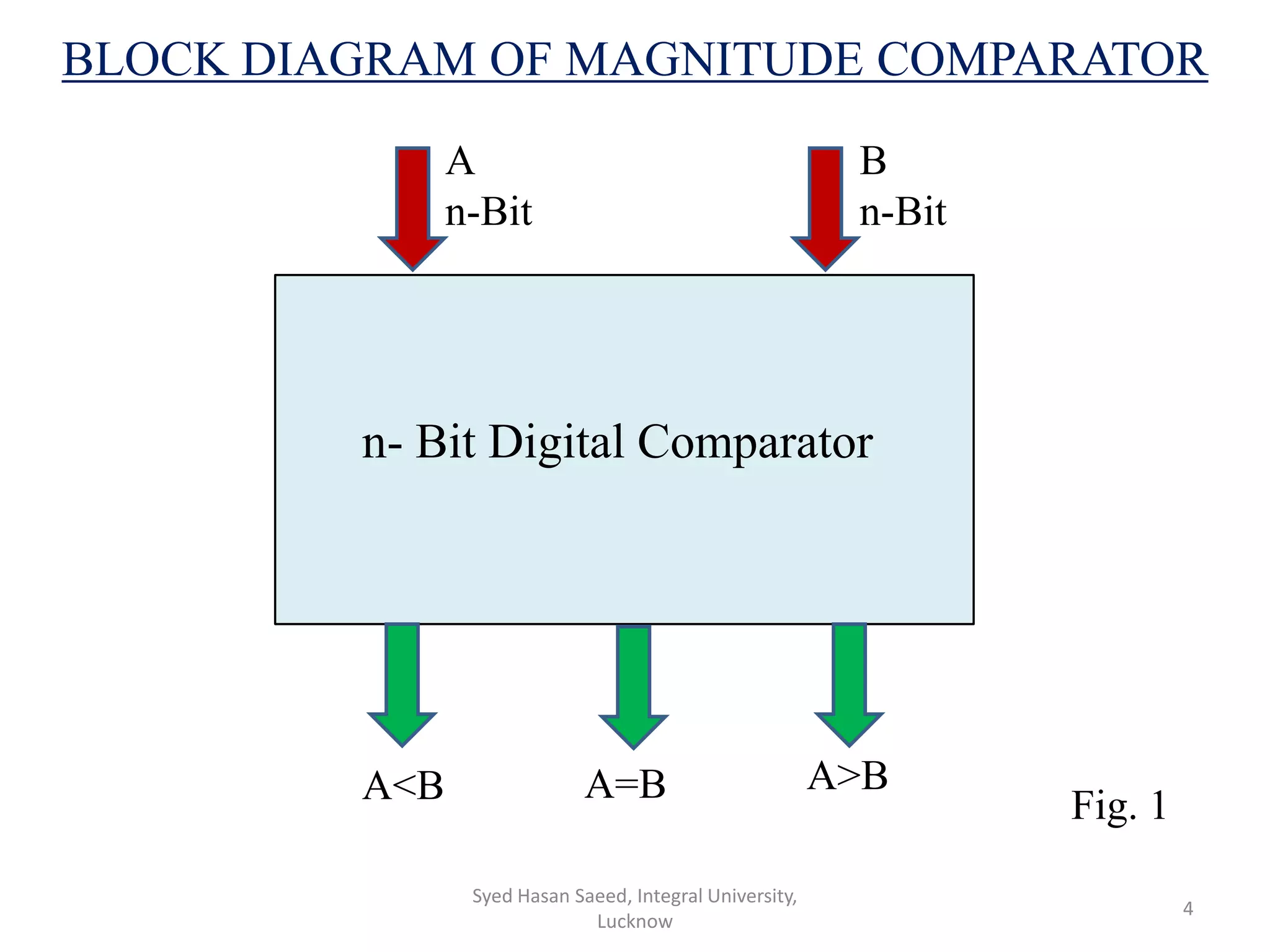

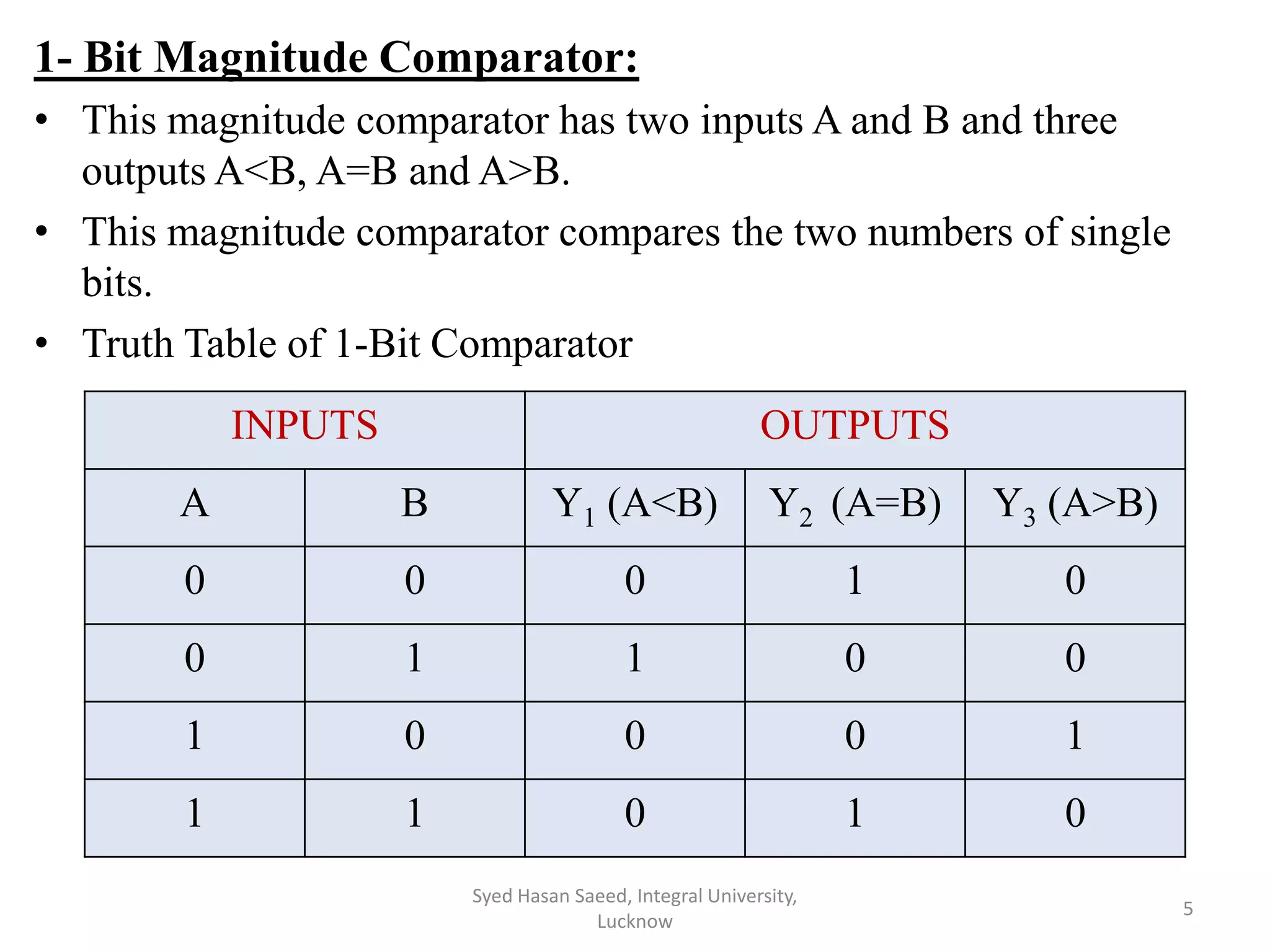

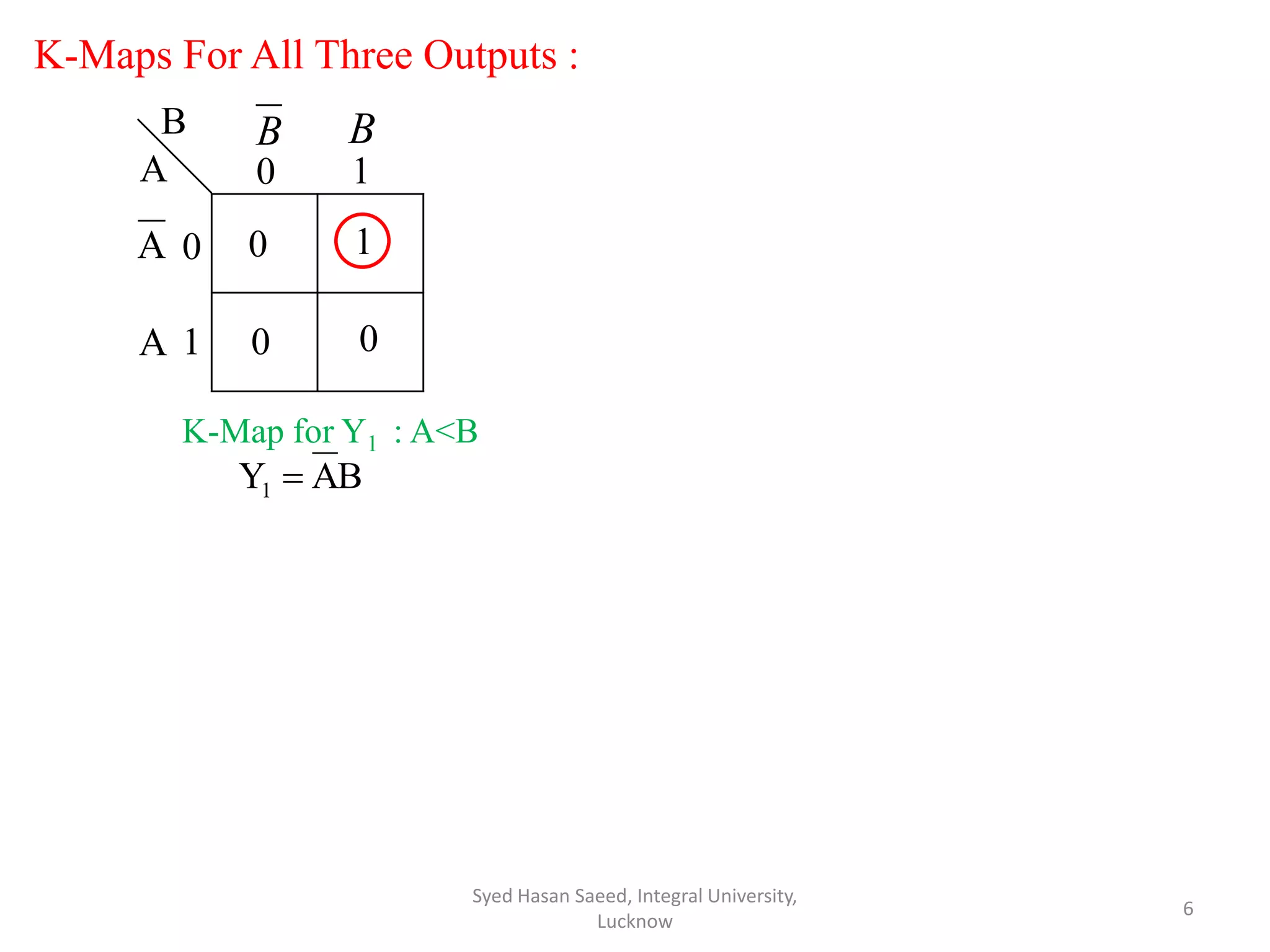

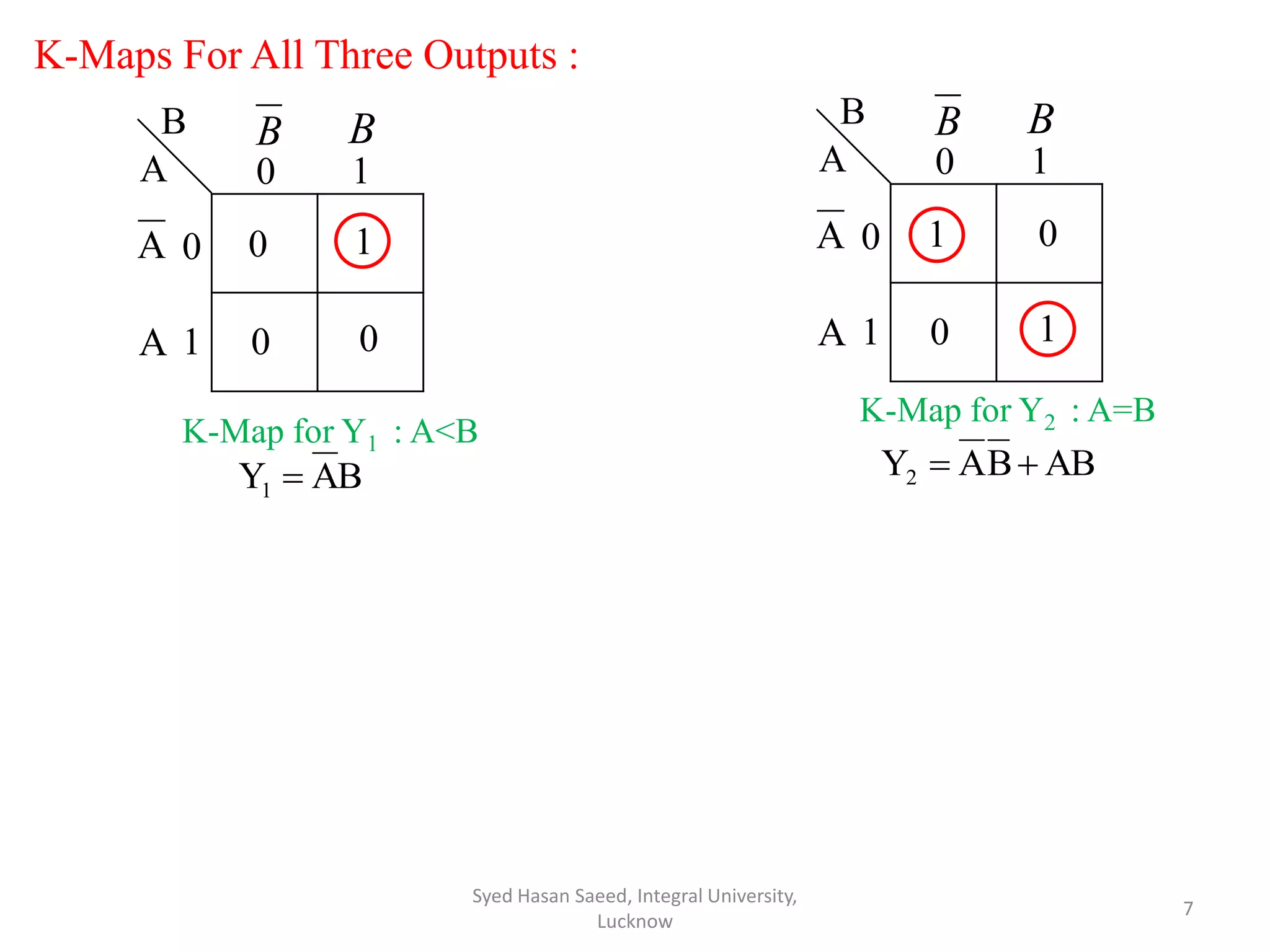

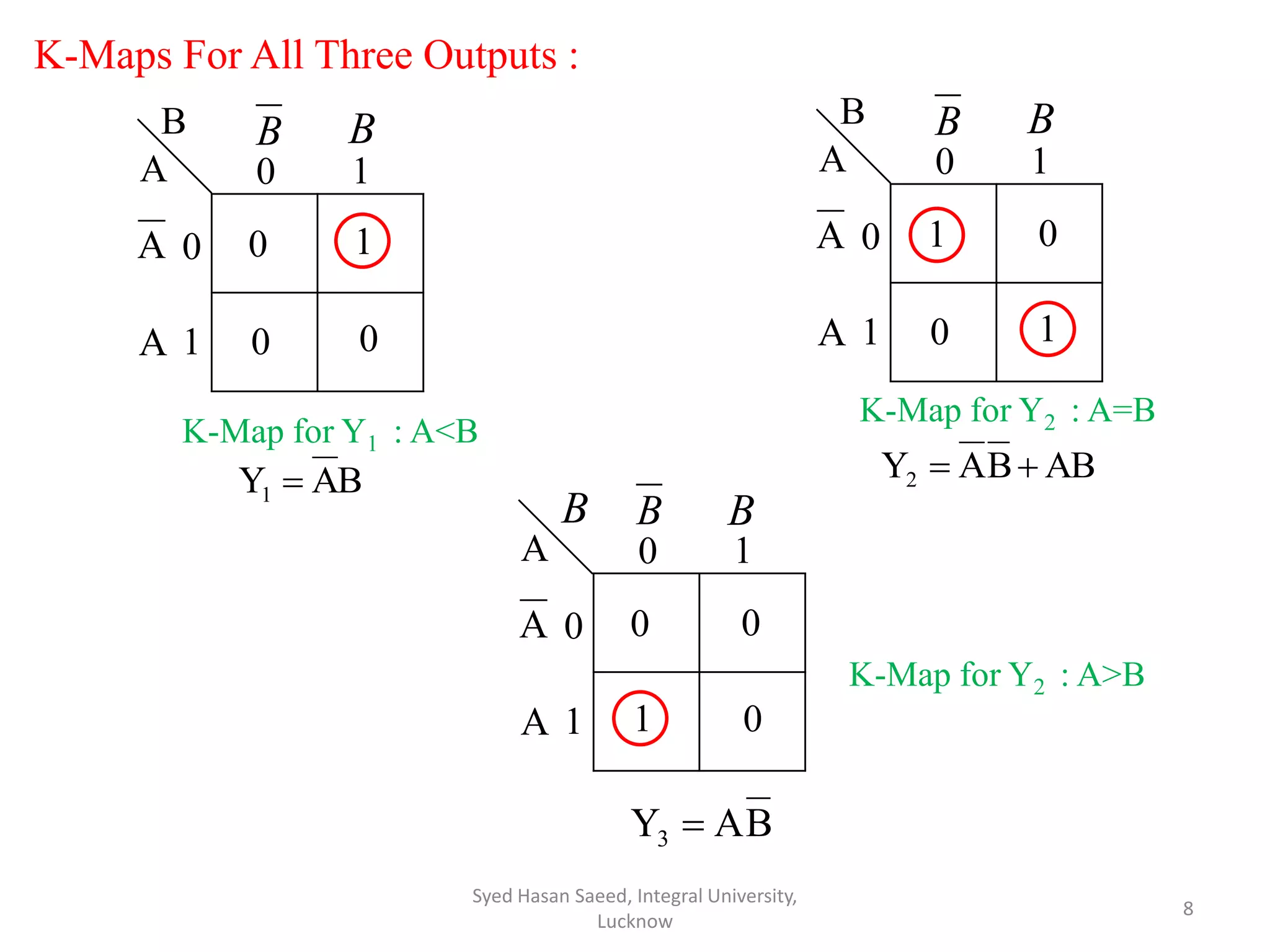

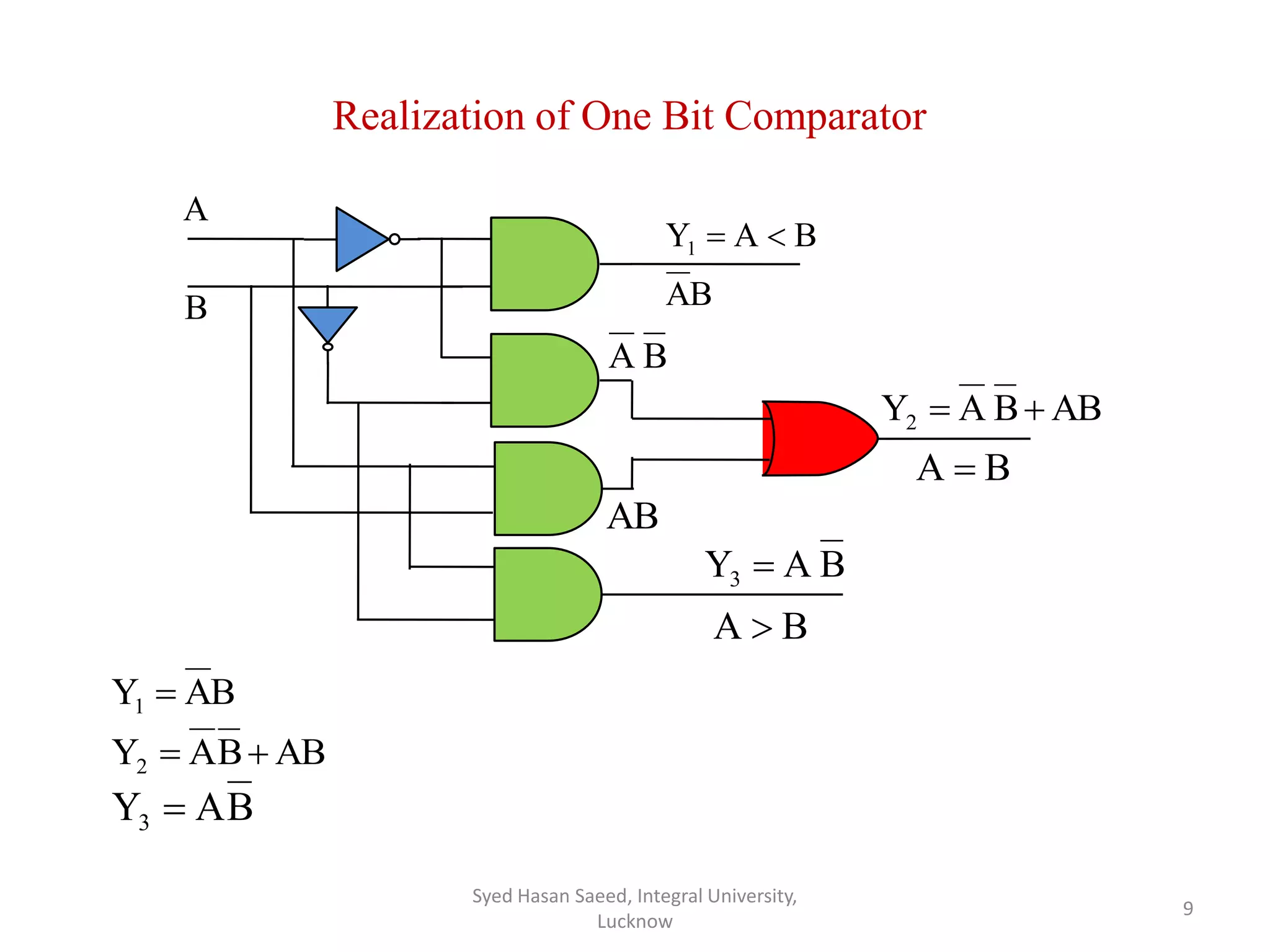

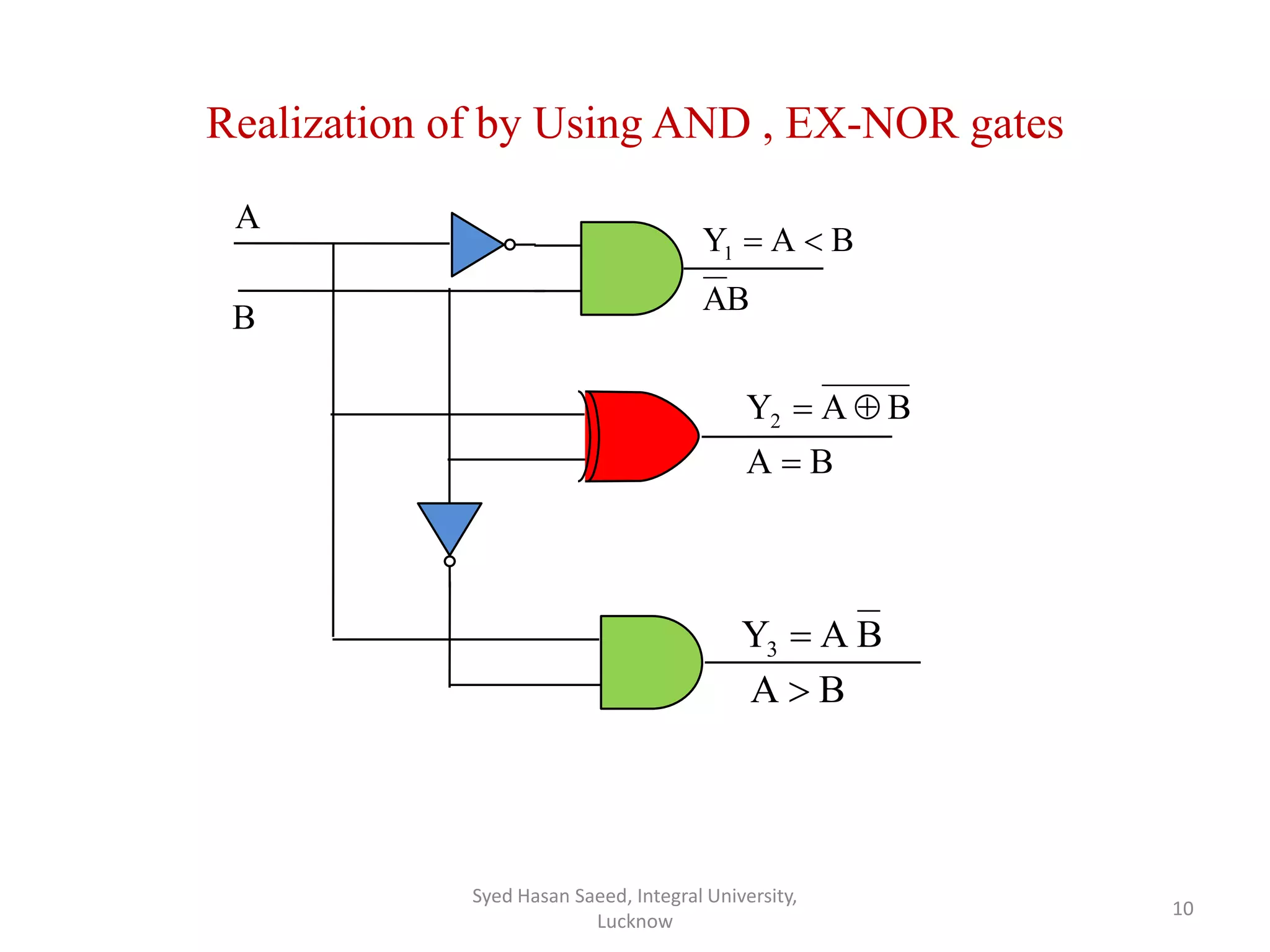

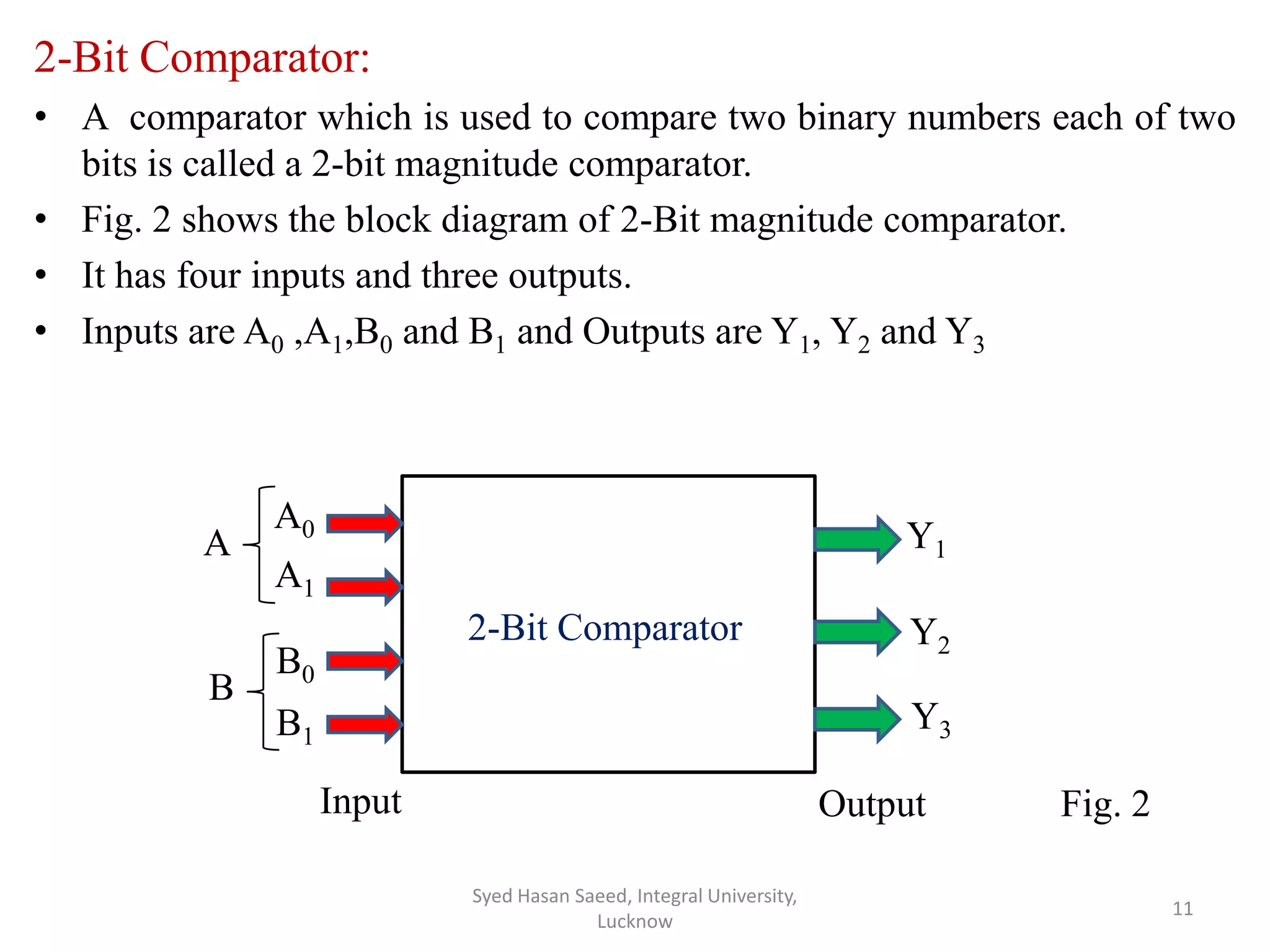

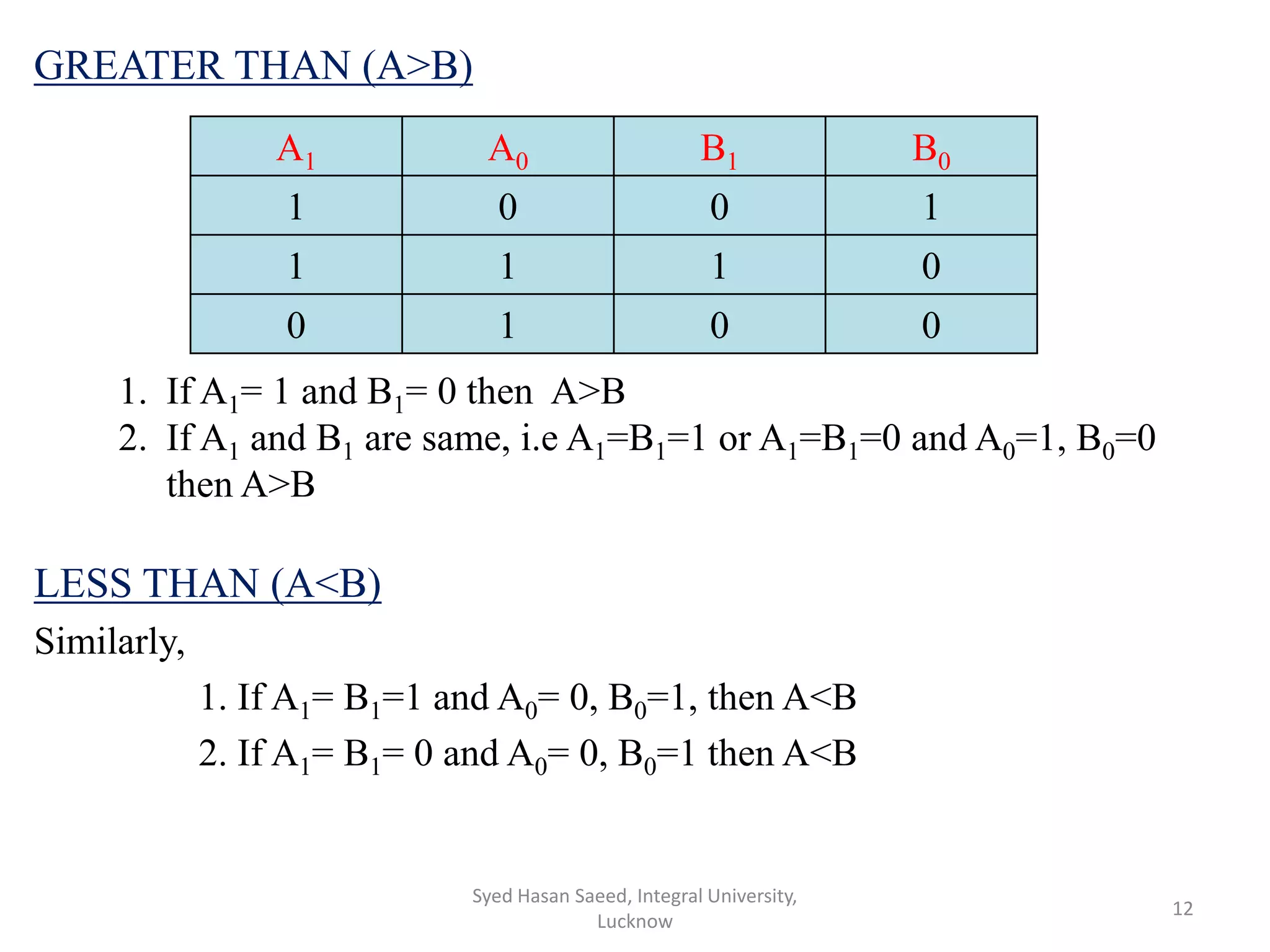

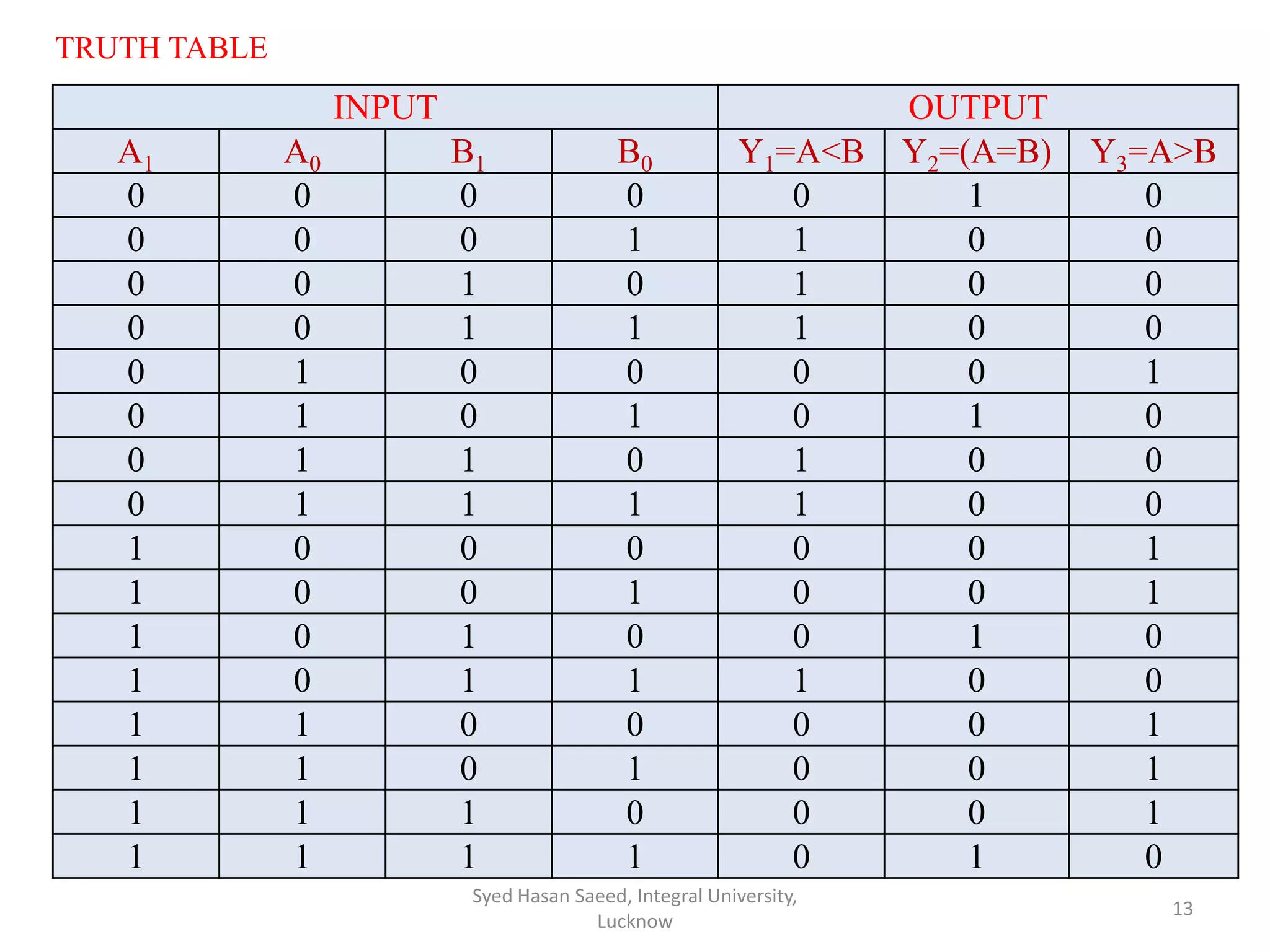

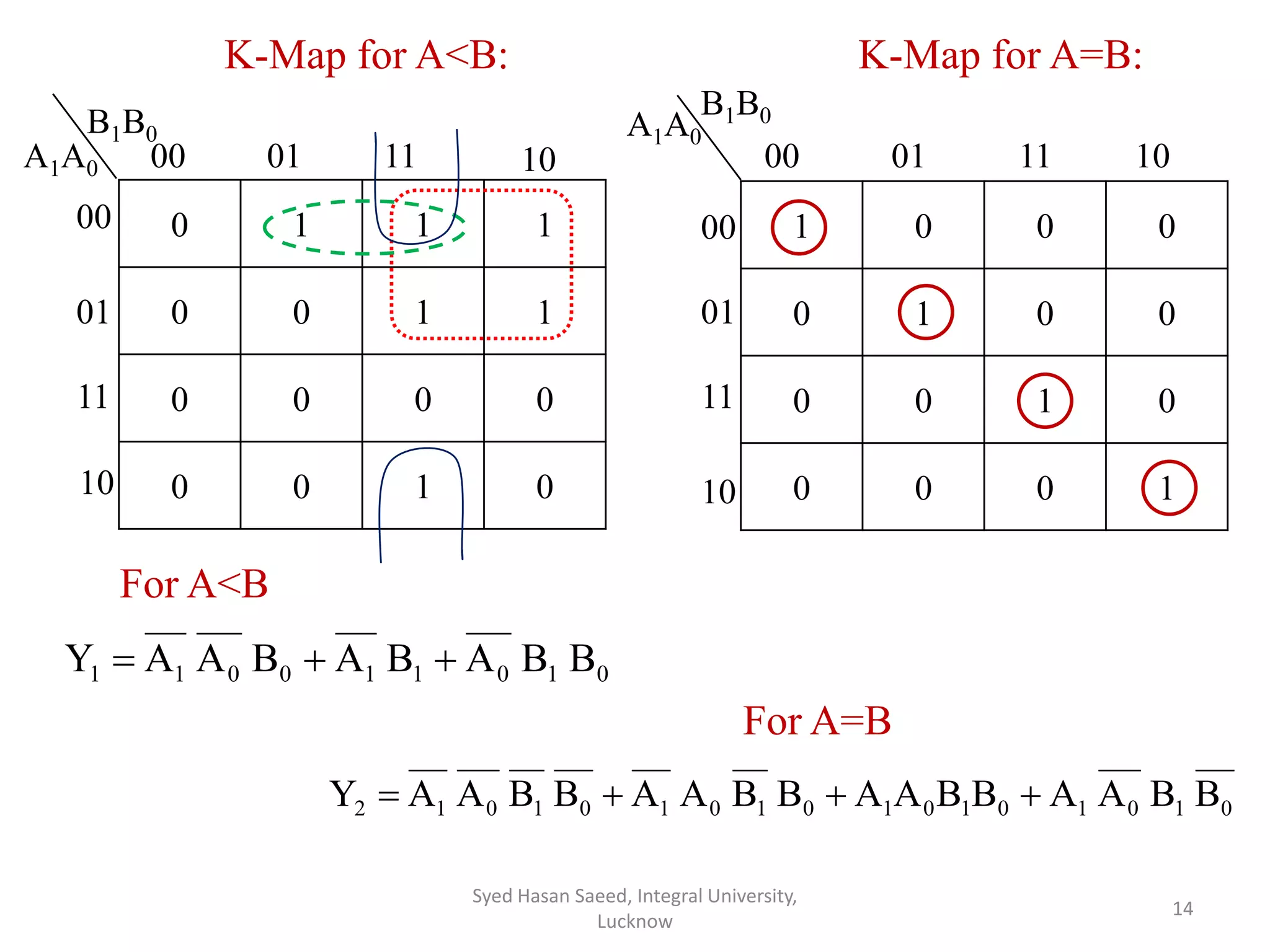

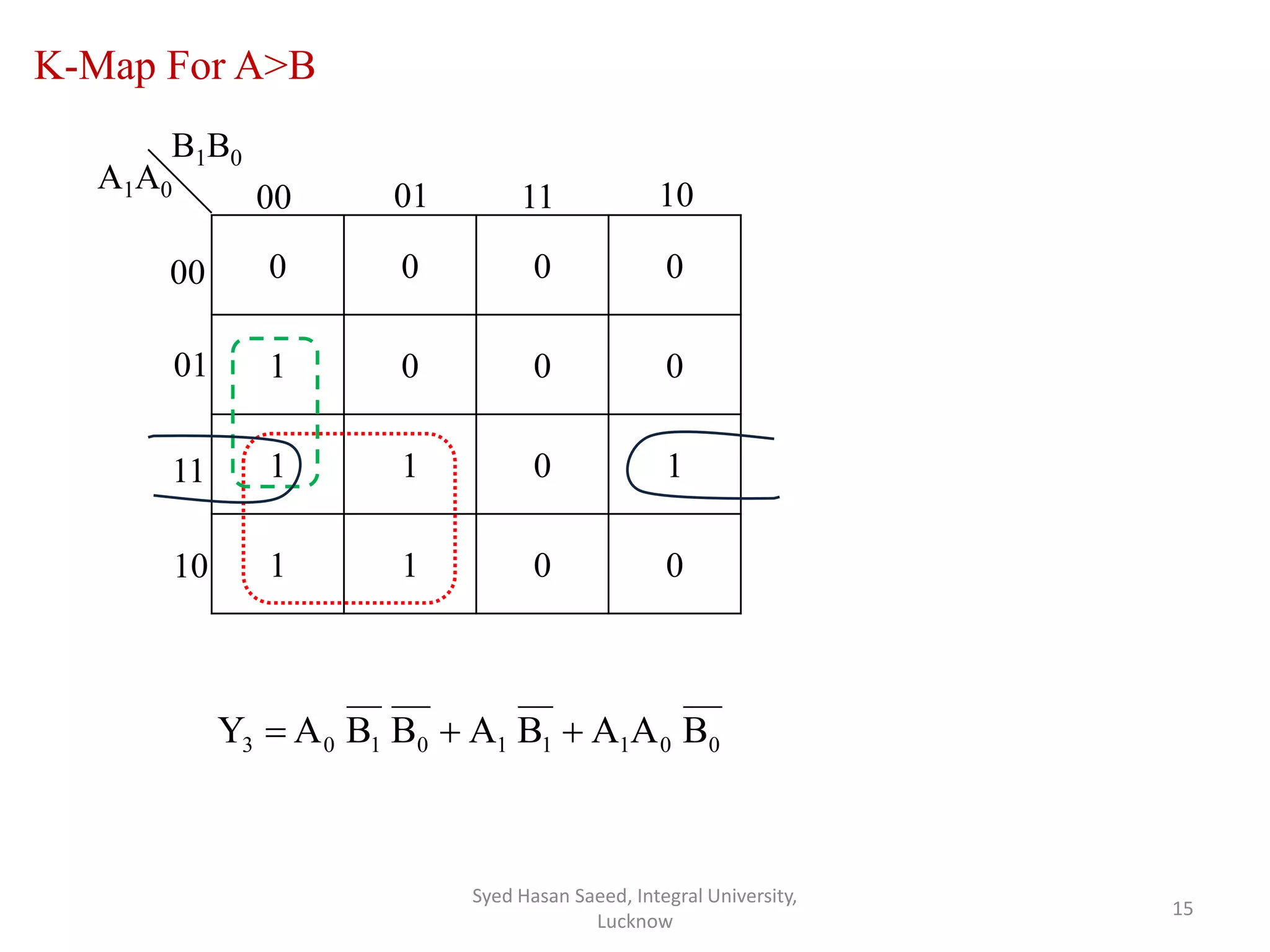

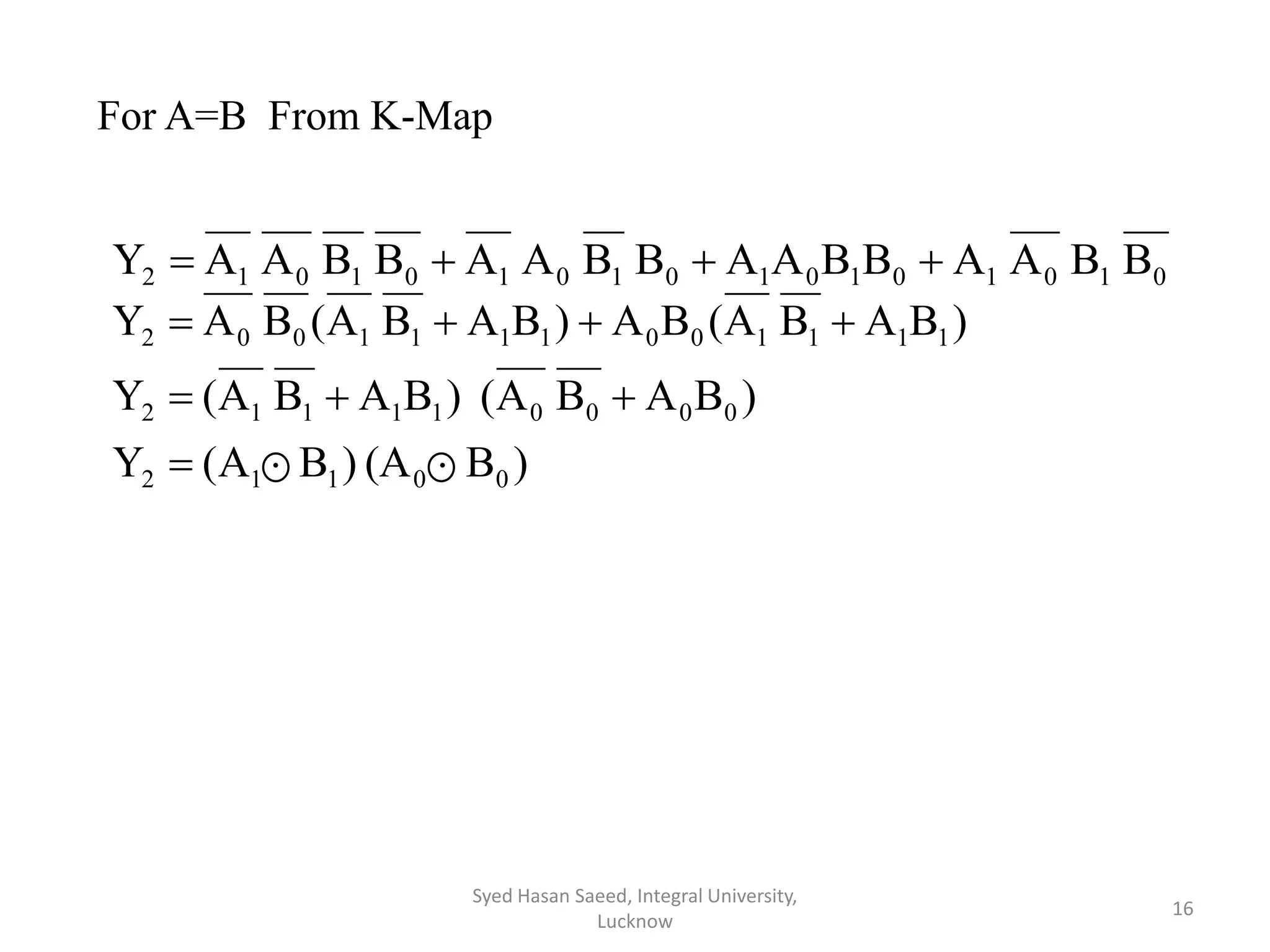

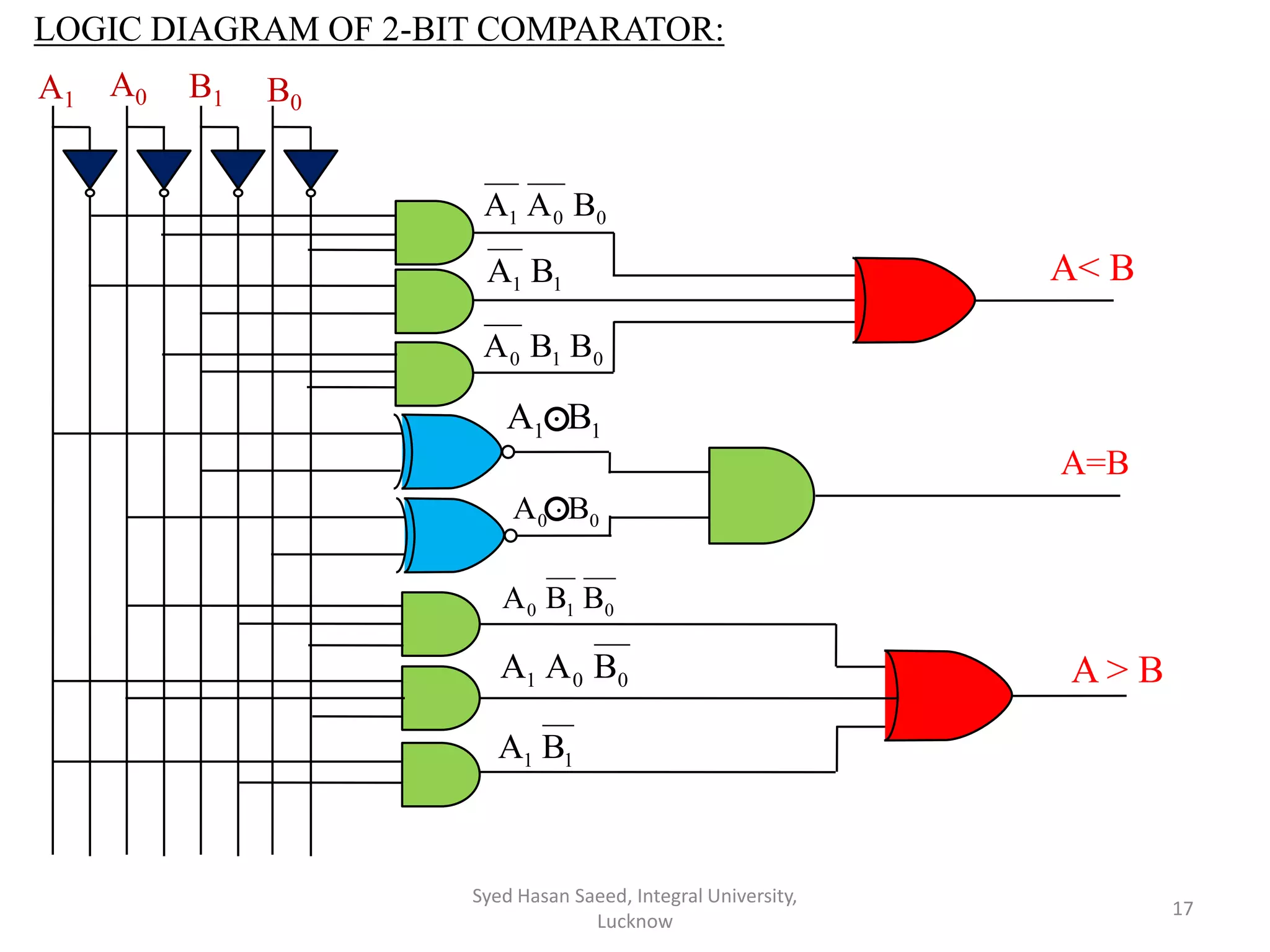

The document discusses magnitude comparators, which are digital circuits used to compare the values of two binary numbers. There are two types: identity comparators and magnitude comparators. Magnitude comparators have three outputs - A>B, A=B, and A<B to indicate the relationship between the inputs. The document then discusses the design and implementation of 1-bit and 2-bit magnitude comparators using logic gates like AND and XOR. Truth tables and K-maps are used to derive the logic expressions for the three outputs in each case. Finally, the logic diagram of a 2-bit magnitude comparator is presented.