LinuxCNC is open source CNC software that runs on Linux. It provides motion control, I/O control, and multiple graphical user interfaces. LinuxCNC uses a real-time kernel extension called RTAI to ensure precise timing. It is configured using INI, HAL, VAR, TBL, and NML files that define hardware connections, parameters, tools, and communications. The HAL abstraction layer connects LinuxCNC signals to physical hardware pins.

![Configuring LinuxCNC

Sections

[EMC] general information

[DISPLAY] settings related to the graphical user interface

[FILTER] settings input filter programs

[RS274NGC] settings used by the g-code interpreter

[EMCMOT] settings used by the real time motion

controller

[TASK] settings used by the task controller

[HAL] specifies .hal files

[HALUI] MDI commands used by HALUI

[TRAJ] additional settings used by the real time motion

controller

[AXIS_n] individual axis variables

[EMCIO] settings used by the I/O Controller

Example

16](https://image.slidesharecdn.com/linuxcncoverview-140123113227-phpapp02/85/LinuxCNC-16-320.jpg)

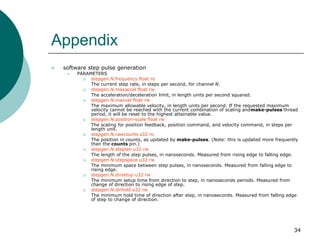

![Appendix

software step pulse generation

installing

loadrt stepgen step_type=type0[,type1...]

[ctrl_type=type0[,type1...]] [user_step_type=#,#...]

FUNCTIONS

stepgen.make-pulses (no floating-point)

Generates the step pulses, using information computed

by update-freq. Must be called as frequently as possible, to

maximize the attainable step rate and minimize jitter.

Operates on all channels at once.

stepgen.capture-position (uses floating point)

Captures position feedback value from the high speed code

and makes it available on a pin for use elsewhere in the

system. Operates on all channels at once.

stepgen.update-freq (uses floating point)

Accepts a velocity or position command and converts it into a

form usable by make-pulses for step generation. Operates

on all channels at once.

32](https://image.slidesharecdn.com/linuxcncoverview-140123113227-phpapp02/85/LinuxCNC-32-320.jpg)

![AXIS

1.

2.

3.

4.

Create an .xml file that contains your

panel description and put it in your

config directory.

Add the PyVCP entry to the [DISPLAY]

section of the ini file with your .xml file

name.

Add the POSTGUI_HALFILE entry to the

[HAL] section of the ini file with the

name of your postgui HAL file name.

Add the links to HAL pins for your panel

in the postgui.hal file to connect your

PyVCP panel to LinuxCNC

63](https://image.slidesharecdn.com/linuxcncoverview-140123113227-phpapp02/85/LinuxCNC-63-320.jpg)

![AXIS

[DISPLAY] section (.ini file)

[HAL] section (.ini file)

PYVCP = spindle.xml

POSTGUI_HALFILE =

spindle_to_pyvcp.hal

links to HAL pins (.hal file)

net spindle-rpm-filtered =>

pyvcp.spindle-speed

66](https://image.slidesharecdn.com/linuxcncoverview-140123113227-phpapp02/85/LinuxCNC-66-320.jpg)