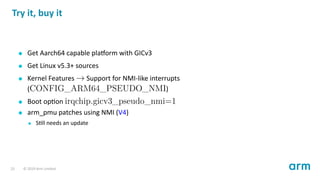

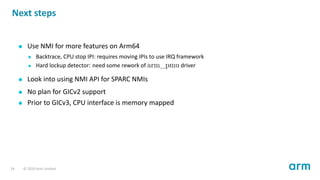

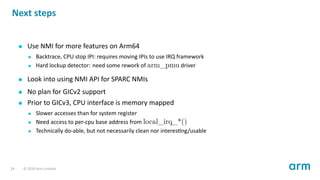

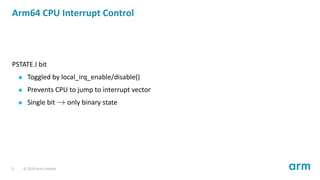

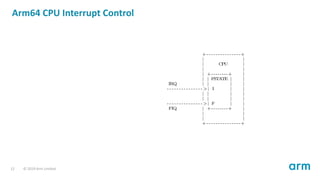

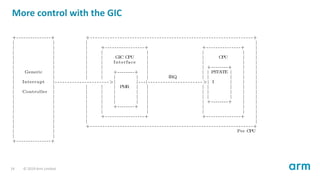

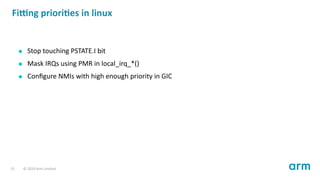

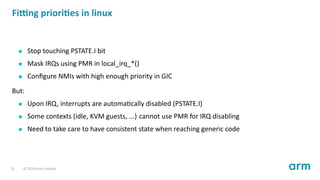

This document discusses the implementation of pseudo-non-maskable interrupts (pseudo-NMI) for ARM64 architecture by addressing the need for non-maskable interrupts and outlining their behavior in system management. It highlights the work done by the ARM Linux kernel team to create a solution that emulates NMI functionality using interrupt request priorities and the Generic Interrupt Controller (GIC). The presentation also outlines future steps for enhancing NMI features on ARM64, including backtrace functionality and integration with CPU stop interrupts.

![Timeline

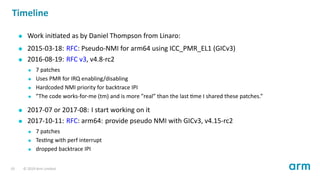

2018-05-21: V3, v4.17-rc6

6 patches

Review

As i t is , t h i s patch i s almost i mp oss ib le to review . I t turns the

i n t e r r u p t masking upside down , messes with the GIC , hacks KVM . . . Too

many t h i n g s change at once , and I f i n d i t very hard to b u i l d a mental

p i c t u r e of the changes j u s t by s t a r i n g at i t .

[ . . . ]

Thanks ,

M.

20 © 2019 Arm Limited](https://image.slidesharecdn.com/jthierry-191004102035/85/Kernel-Recipes-2019-No-NMI-No-Problem-Implementing-Arm64-Pseudo-NMI-28-320.jpg)