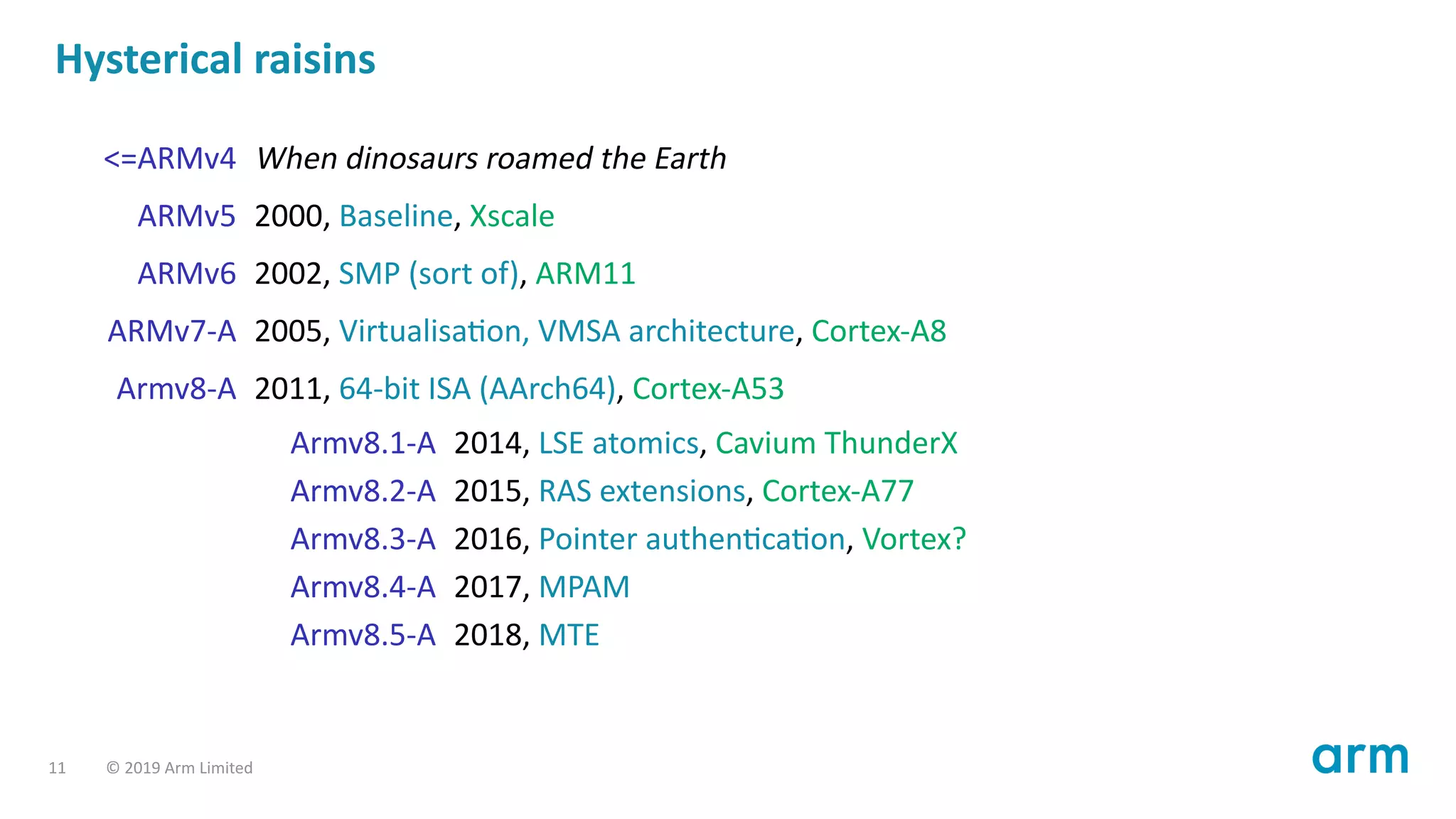

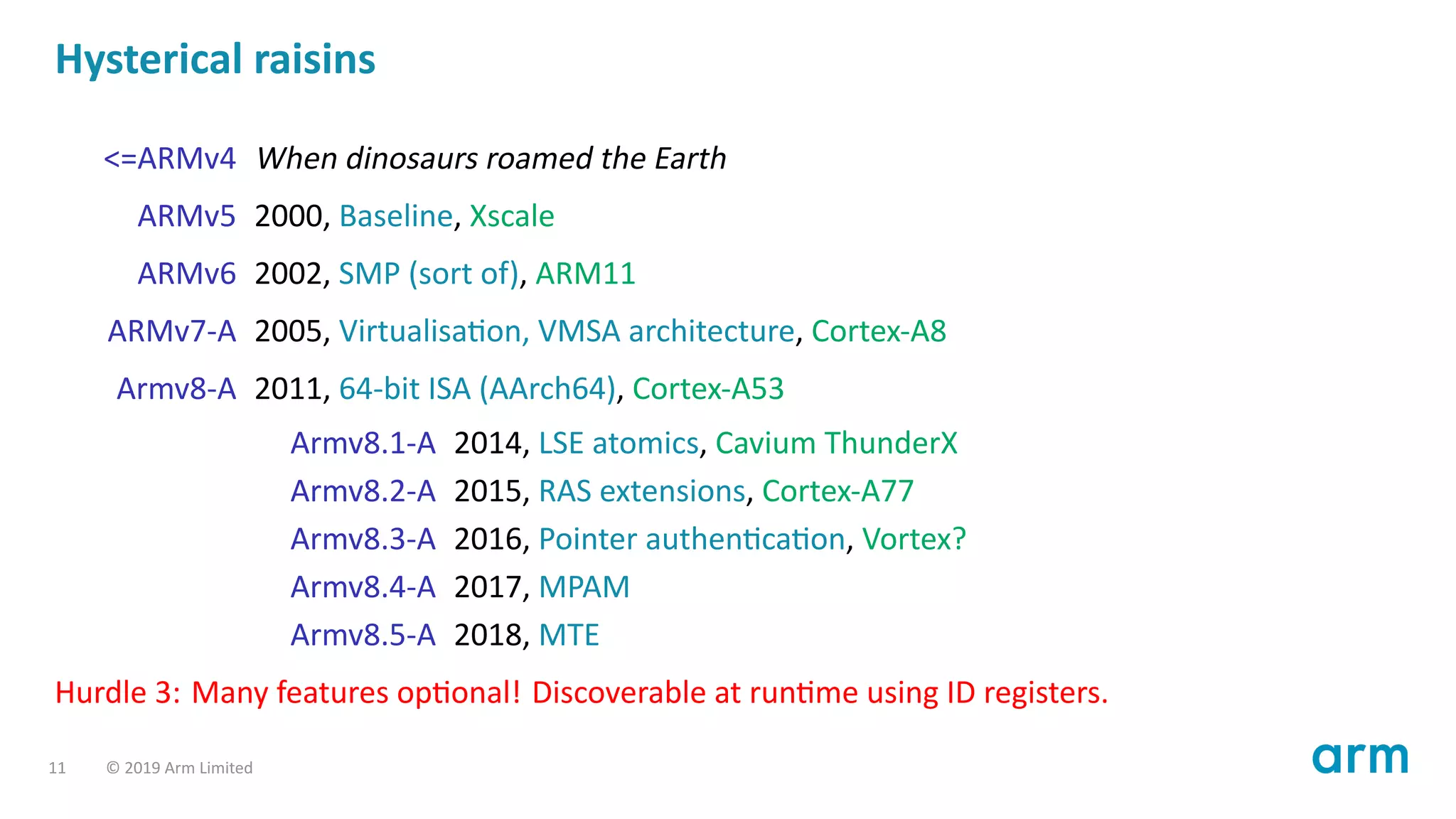

The document is a presentation by Paris Will Deacon on identifying CPU features in ARM architecture, detailing the historical context and complexities of ARM's diverse hardware and software ecosystem. It highlights challenges faced by developers in understanding ARM's architecture versus micro-architecture distinction, licensing models, and the resulting fragmentation causing inconsistencies in product naming. It also discusses the ARM kernel's coping mechanisms for various CPU features in the Linux environment.