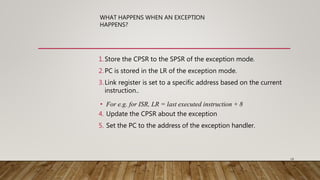

1) When an exception occurs, the processor stores the current CPSR to the SPSR, stores the PC to the LR, and sets the PC to the exception handler address.

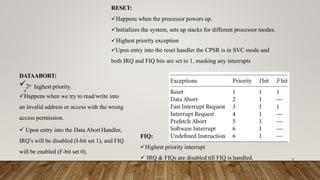

2) There are several types of exceptions including reset, data abort, FIQ, IRQ, undefined instruction, and SWI. FIQ has the highest priority while reset is handled first during startup.

3) Interrupts are higher priority events that pause normal instruction execution. IRQs can be handled by nested or non-nested interrupt handlers depending on whether interrupts are enabled during handling.

![• B<address> provides a branch relative from the pc.

• LDR pc, [pc, #offset]—This load register instruction

loads the handler address from memory to the pc.

• LDR pc, [pc, #-0xff0]—This load register instruction

loads a specific interrupt service routine address from

address 0xfffff030 to the pc.

• MOV pc, #immediate—This move instruction copies

an immediate value into the pc. MOV pc, #immediate](https://image.slidesharecdn.com/armmhi-201012112315/85/ARM-exceptions-and-interrupt-controls-4-320.jpg)