More Related Content

PDF

PDF

PDF

PDF

SDSoC勉強会_170128_スライド「SDx 2016.3のプラグマによるハードウェアと性能」 PDF

PDF

PDF

PDF

What's hot

PPTX

ラプラシアンフィルタをZedBoardで実装(ソフトウェアからハードウェアにオフロード) PPTX

PDF

PDF

PDF

FPGAで作るOpenFlow Switch (FPGAエクストリーム・コンピューティング 第6回) FPGAX#6 PPT

PDF

PDF

高位合成ツールVivado hlsのopen cv対応 PDF

ACRi_webinar_20220118_miyo PDF

PDF

PDF

PDF

Pynqでカメラ画像をリアルタイムfastx コーナー検出 ODP

PDF

PDF

PDF

PPTX

PPTX

研究者のための Python による FPGA 入門 PDF

Viewers also liked

PPTX

20161120_HPCでFPGAを使ってみたい_fpgastartup PPTX

PDF

PDF

PPTX

PDF

PDF

SDSoC 2016.3+yocto project PDF

PPTX

PDF

Xilinx SDSoC(2016.3)解体新書ソフトウェア編 PDF

Moving computation to the data (1) PPTX

PPT

PDF

FPGAの部屋、slide share、xilinxツールのご紹介 PDF

15.06.27 実録 ソフトウェア開発者が FPGAを独習した最初の3歩@RTLを語る会(9) PPTX

PDF

PDF

PPTX

PDF

Tensor flow usergroup 2016 (公開版) Similar to FPGA startup 第一回 LT

PDF

PDF

PPT

PDF

PDF

FPGAベースのソーティングアクセラレータの設計と実装 PDF

Halide, Darkroom - 並列化のためのソフトウェア・研究 PDF

FPGAを用いた世界最速のソーティングハードウェアの実現に向けた試み PDF

PDF

FPGAをロボット(ROS)で「やわらかく」使うには PDF

PDF

FPGAによる津波シミュレーション -- GPUを超える高性能計算の手法 PPTX

PDF

PPTX

Androidとfpgaを高速fifo通信させちゃう PDF

PDF

High-speed Sorting using Portable FPGA Accelerator (IPSJ 77th National Conven... PDF

Altera SDK for OpenCL解体新書 : ホストとデバイスの関係 PDF

第3回ローレイヤー勉強会 : FPGAでコンピュータを作ってみた PDF

IEICE technical report (RECONF), January 2015. PDF

FPGA startup 第一回 LT

- 1.

- 2.

- 3.

- 4.

- 5.

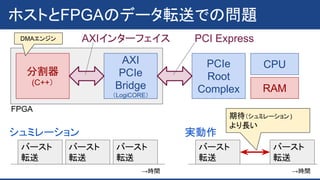

● Xilinx Virtex-7XC7VX690T-2

○ ALPHA DATA ADM-PCIE-7V3

■ PCI Express: x8, Gen3

● Vivado

● Vivado HLS (高位合成コンパイラ)

○ C++で記述

デバイスと開発環境

- 6.

- 7.

- 8.

- 9.

- 10.