Flip flops

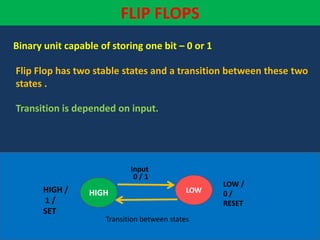

- 1. FLIP FLOPS Binary unit capable of storing one bit – 0 or 1 Flip Flop has two stable states and a transition between these two states . Transition is depended on input. Input 0/1 HIGH / 1/ SET HIGH LOW Transition between states LOW / 0/ RESET

- 2. Types of FLIP FLOPS FLIP FLOP RS Flip Flop JK Flip Flop T Flip Flop D Flip Flop

- 3. RS - FLIP FLOP Block Diagram R S RS Flip Flop Q Q

- 4. RS - FLIP FLOP RS Latch using NOR Gate A R S Q Q B

- 5. RS - FLIP FLOP TRUTH TABLE R S Q Case 1 0 0 NC Case 2 0 1 SET Case 3 1 0 RESET Case 4 1 1 * R 0 A 1 0 0 1 1 0 S 0 1 B 0 Q Q NO CHANGE

- 6. RS - FLIP FLOP TRUTH TABLE R S Q Case 1 0 0 NC Case 2 0 1 SET Case 3 1 0 RESET Case 4 1 1 * R 0 A 1 SET Q 0 01 S 1 B 0 Q

- 7. RS - FLIP FLOP TRUTH TABLE R S Q Case 1 0 0 NC Case 2 0 1 SET Case 3 1 0 RESET Case 4 1 1 * R 1 0 01 0 S 0 RESET A 1 B Q Q

- 8. RS - FLIP FLOP TRUTH TABLE R S Q Case 1 0 0 NC Case 2 0 1 SET Case 3 1 0 RESET Case 4 1 1 * R 1 A 0 0 0 S 1 0 B Q Q

- 9. RS - FLIP FLOP RS Latch using NAND Gate (RS Flip Flop) A R S Q Q B R S Q 0 0 * 0 1 SET 1 0 RESET 1 1 NC

- 10. RS - FLIP FLOP RS Latch using NAND Gate 0 R 0 0 S 1 A Q 1 1 1 Q B 0 R S Q 0 0 * 0 1 SET 1 0 RESET 1 1 NC Race Condition

- 11. RS - FLIP FLOP RS Latch using NAND Gate (RS Flip Flop) R 0 A 01 01 S 1 Q 01 Q B 1 R S Q 0 0 * 0 1 SET 1 0 RESET 1 1 NC

- 12. RS - FLIP FLOP RS Latch using NAND Gate 1 R A 10 10 Q 10 S B 0 1 R S Q 0 0 * 0 1 SET 1 0 RESET 1 1 NC Q

- 13. RS - FLIP FLOP RS Latch using NAND Gate R 1 10 A 10 Q 10 S 1 10 B R S Q 0 0 * 0 1 SET 1 0 RESET 1 1 NC Q

- 14. Clocked RS Flip Flop What is the Difference ???? A Clock signal is added to the input What Clock Signal will do ???? Clock Signal controls the instant at which flip flop changes the state How to Design ??? Basic NOR- Flip Flop + Two AND Gates + A Clock Signal R Q CLK nnn Q S

- 15. Clocked RS Flip Flop Block Diagram of Clocked RS Flip Flop R Q CLK S Q Rule of RS Flip Flop : Q is always complement of Q

- 17. Clocked RS Flip Flop Case 1 R S CLK Qn Qn+1 ACTION 0 0 0 0 0 NC 0 R 0 Q 10 0 CLK 10 nnn 10 S 0 0 10 Q

- 18. Clocked RS Flip Flop Case 2 R CLK Qn Qn+1 ACTION 0 R S 0 0 1 1 NC 0 0 Q 0 0 CLK 1 nnn 0 S 0 0 1 Q

- 19. Clocked RS Flip Flop Case 3 R S CLK Qn Qn+1 ACTION 0 0 1 0 0 NC 0 0 R CLK 10 Q 10 1 nnn 10 S 0 0 10 Q

- 20. Clocked RS Flip Flop Case 4 R S CLK Qn Qn+1 ACTION 0 0 1 1 1 NC 0 R CLK 0 1 Q 0 1 nnn 0 S 0 0 1 Q

- 21. Clocked RS Flip Flop Case 5 R S CLK Qn Qn+1 ACTION 0 1 0 0 0 NC 0 R Q nnn 10 S 1 0 0 10 0 CLK 0 1 0 10 Q

- 22. Clocked RS Flip Flop Case 6 R CLK Qn Qn+1 ACTION 0 R S 1 0 1 1 NC 0 Q 0 CLK S 1 nnn Q

- 23. Clocked RS Flip Flop Case 7 R S CLK Qn Qn+1 ACTION 0 1 1 0 1 SET R Q CLK nnn Q S

- 24. Clocked RS Flip Flop Case 8 R S CLK Qn Qn+1 ACTION 0 1 1 1 1 SET R Q CLK nnn Q S

- 25. Clocked RS Flip Flop Case 9 R S CLK Qn Qn+1 ACTION 1 0 0 0 0 NC R Q CLK nnn Q S

- 26. Clocked RS Flip Flop Case 10 R S CLK Qn Qn+1 ACTION 1 0 0 1 1 NC R Q CLK nnn Q S

- 27. Clocked RS Flip Flop Case 11 R S CLK Qn Qn+1 ACTION 1 0 1 0 0 RESET R Q CLK nnn Q S

- 28. Clocked RS Flip Flop Case 12 R S CLK Qn Qn+1 ACTION 1 0 1 1 0 RESET R Q CLK nnn Q S

- 29. Clocked RS Flip Flop Case 13 R S CLK Qn Qn+1 ACTION 1 1 0 0 0 NC R Q CLK nnn Q S

- 30. Clocked RS Flip Flop Case 14 R S CLK Qn Qn+1 ACTION 1 1 0 1 1 NC R Q CLK nnn Q S

- 31. Clocked RS Flip Flop Case 15 R S CLK Qn Qn+1 ACTION 1 1 1 0 ? ERROR R Q CLK nnn Q S

- 32. Clocked RS Flip Flop Case 16 R S CLK Qn Qn+1 ACTION 1 1 1 1 ? ERROR R Q CLK nnn Q S

- 33. D – Flip Flop (Delay Flip Flop) (Clocked) 1. Stores digital info 2. Has Single input 3. It does not have Race Condition D Flip Flop = One RS Latch + One Inverter Single Input D Clk D Flip Flop Q Q

- 34. D – Flip Flop (Delay Flip Flop) (Clocked) D Flip Flop using NAND Gate When Clock is LOW : AND gates of Flip Flop are ENABLE When Clock is HIGH : AND gates of Flip Flop are DISABLE Single Input D Q CLK Q

- 35. D – Flip Flop (Delay Flip Flop) (Clocked) Truth Table Clock Input ( D) Output (Q) 1 0 0 1 1 1 0 x No Change 0 1 D 10 Q 10 CLK bb 10 1 Q 1 0 1

- 36. D – Flip Flop (Delay Flip Flop) (Clocked) Truth Table Clock Input ( D) Output (Q) 1 1 1 0 CLK 0 1 D 0 x No Change 1 0 1 Q 1 0 1 fff 1 0 Q 0 1 10

- 37. D – Flip Flop (Delay Flip Flop) (Clocked) Truth Table Clock Input ( D) Output (Q) 1 0 0 1 1 1 0 x No Change 0 1 D CLK 1 0 Q 1 0 0 1 0 Q 1 1 1 0

- 38. D – Flip Flop (Delay Flip Flop) (Clocked) Truth Table Clock Input ( D) Output (Q) 1 0 0 1 1 1 0 x No Change 1 1 D CLK 1 Q 1 0 0 1 0 Q 0 1 1

- 39. D – Flip Flop (Delay Flip Flop) (Clocked) State Transition Diagram Q (t) D Q (t+1) 0 0 0 0 1 1 1 0 0 1 1 1 D D 0 D 1 D

- 40. JK Flip Flop • Similar to SR Flip Flop •Input J and K behaves like SET and RESET When J = K = 1, the Flip Flop Output Toggles If Q = 0, it switches to 1 if Q = 1, it switches to 0

- 41. JK Flip Flop using SR Flip Flop S=J.Q J CLK K Q S R =K. Q J CLK Q R Q CLK K Q

- 42. JK Flip Flop X S J X CLK K Clock Q CLK R X X S=J.Q Inputs Q R =K. Q J K Output Qn+1 Action X 0 0 Qn NC 1 0 1 0 RESET 1 1 0 1 SET 1 1 1 Qn TOGGLE

- 43. JK Flip Flop 0 S=J.Q 0 J CLK K 1 S 0 0 0 Q CLK R 0 1 0 0 Q R =K. Q 0 Clock Inputs J K Output Qn+1 Action X 0 0 Qn NC 1 0 1 0 RESET 1 1 0 1 SET 1 1 1 Qn TOGGLE

- 44. JK Flip Flop S=J.Q 0 J 1 1 CLK K S0 1 Q CLK Q R0 0 0 0 R = K. Q Clock Inputs J K Output Qn+1 Action X 0 0 Qn NC 1 0 1 0 RESET 1 1 0 1 SET 1 1 1 Qn TOGGLE

- 45. JK Flip Flop S=J.Q Q S J CLK K CLK Q R R =K. Q Clock Inputs J K Output Qn+1 Action X 0 0 Qn NC 1 0 1 0 RESET 1 1 0 1 SET 1 1 1 Qn TOGGLE