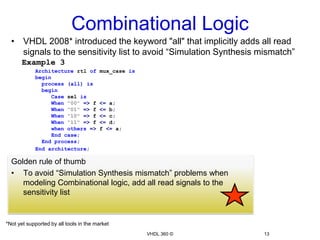

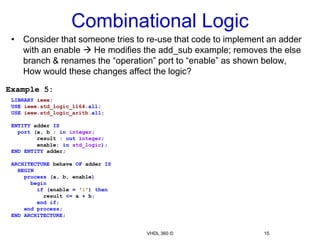

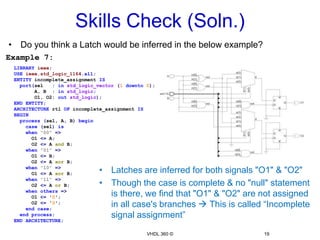

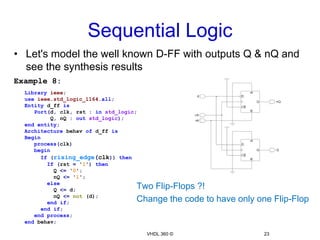

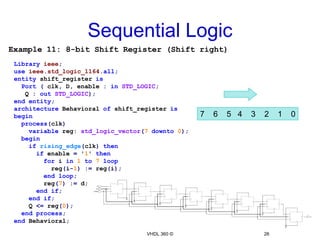

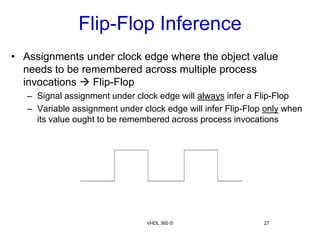

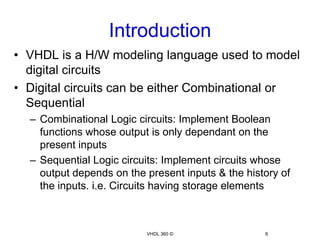

The document provides an overview of VHDL (VHSIC Hardware Description Language) focusing on its application in synthesizing digital circuits, both combinational and sequential. It includes examples of VHDL code, highlighting the significance of proper coding styles to avoid synthesis mismatches and undesired latch inference. The content serves as a guide for writing synthesis-friendly VHDL code with practical examples to understand the impact of code structure on synthesis results.

![IntroductionVHDL 360 ©7VHDL StandardSynthesizable VHDLSynthesis tools translate the VHDL code to a gate level netlist representing the actual H/W gates [and, or, not, Flip-Flops…etc]Only a subset of the language is synthesizableA model can be eitherSynthesizable: Used for both Simulation & SynthesisNon-Synthesizable: Used for Simulation only](https://image.slidesharecdn.com/4-synthesisexamplesversion1-8-110114164510-phpapp02/85/Synthesis-Examples-7-320.jpg)