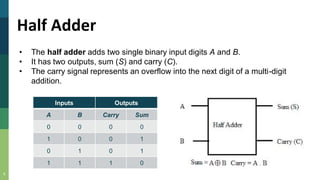

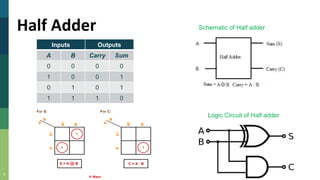

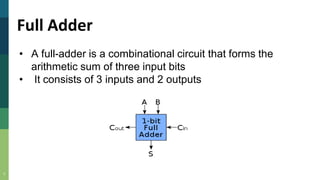

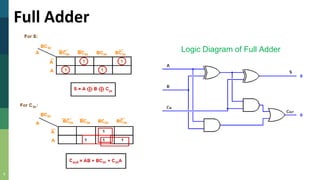

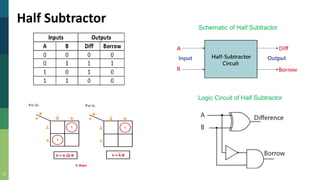

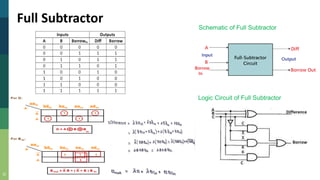

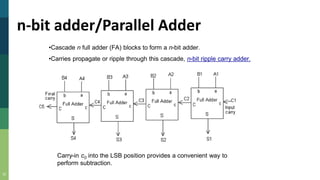

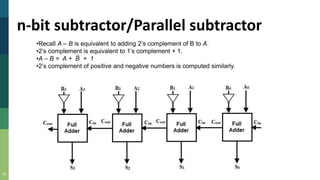

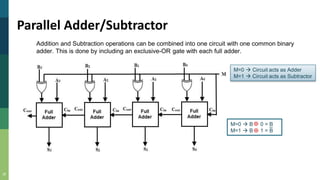

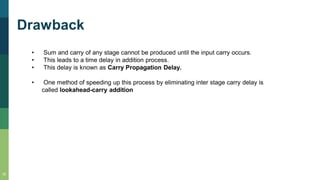

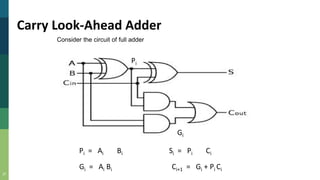

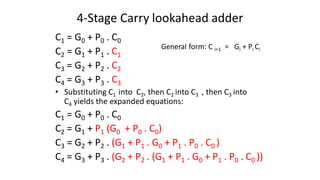

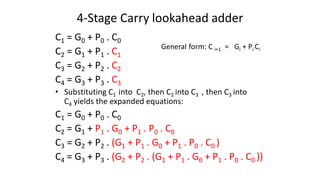

This document discusses combinational and sequential circuits. It begins by defining combinational logic circuits as memoryless digital logic circuits whose output depends only on the current input combination. It then covers various combinational circuits including half adders, full adders, half subtractors, full subtractors, and parallel adders/subtractors. It also discusses sequential circuits including flip-flops and registers. Finally, it covers carry lookahead adders which can speed up the addition process by eliminating inter-stage carry delays.