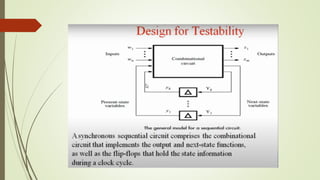

Design for testability is important as chip complexity increases. It involves making chips easier to test by improving controllability and observability of internal signals. Controllability refers to the ability to set a node to a specific value, while observability refers to the ability to observe a node's value. Test generation algorithms aim to improve testability by making internal signals easier to control and observe.