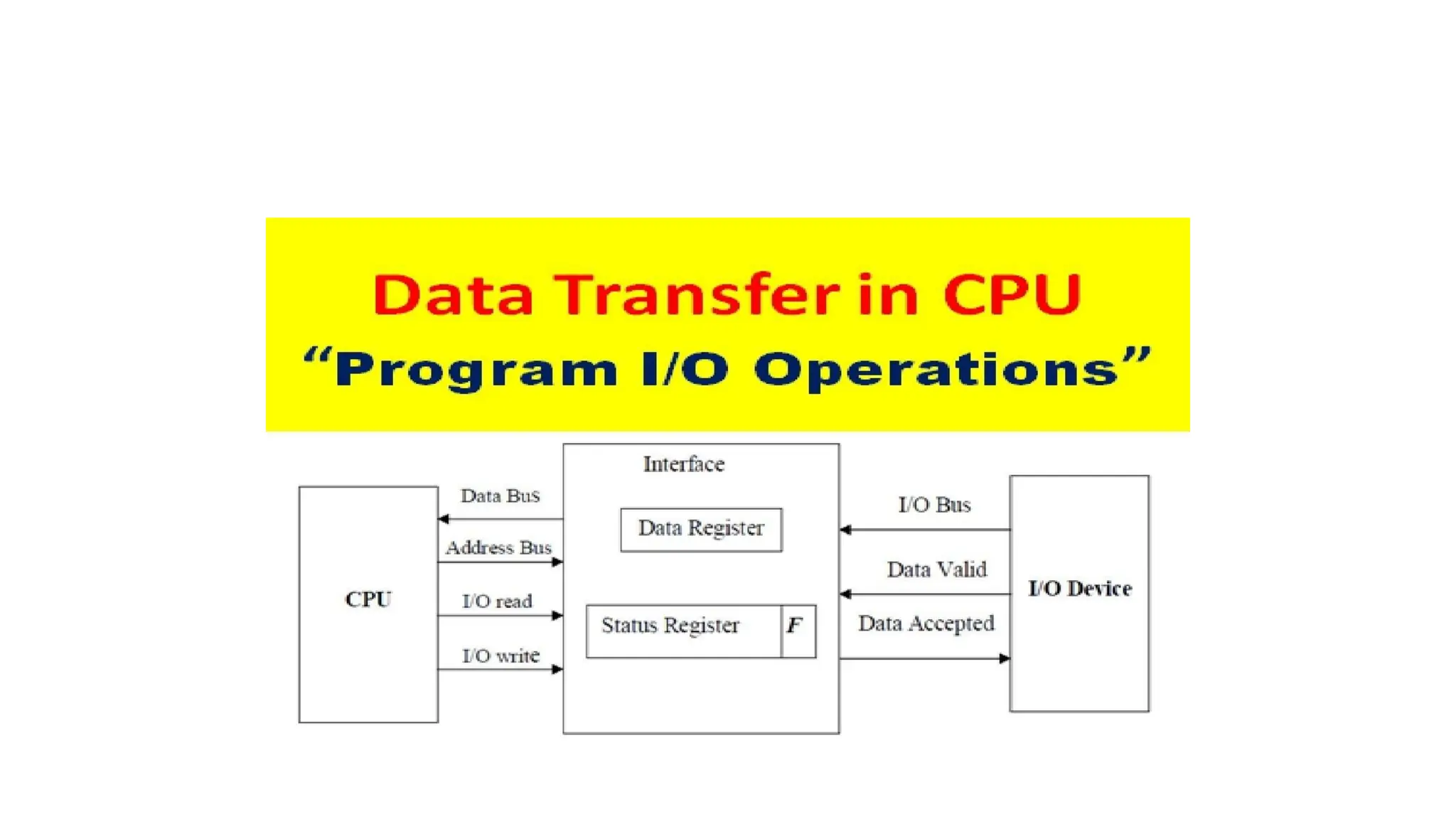

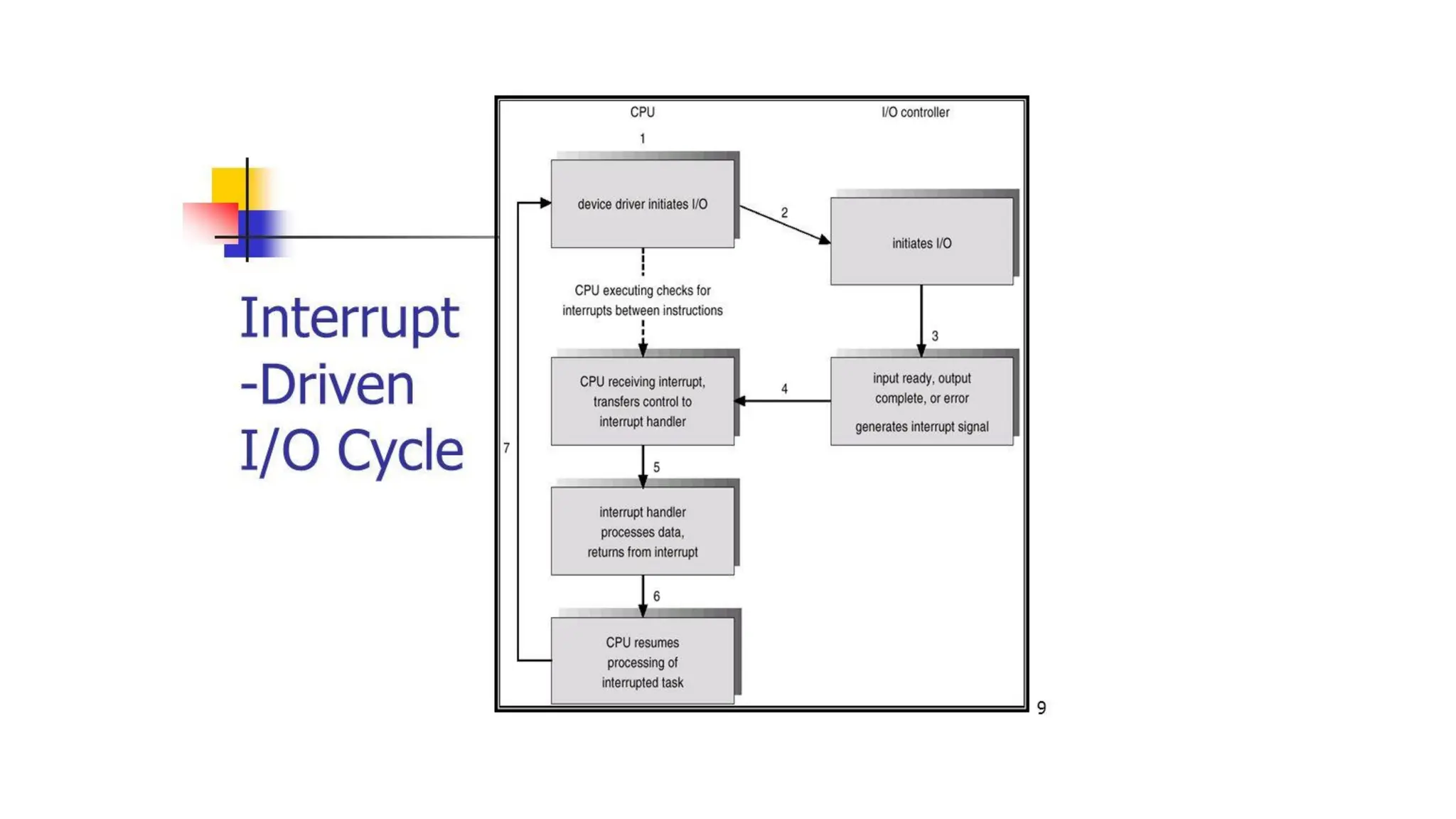

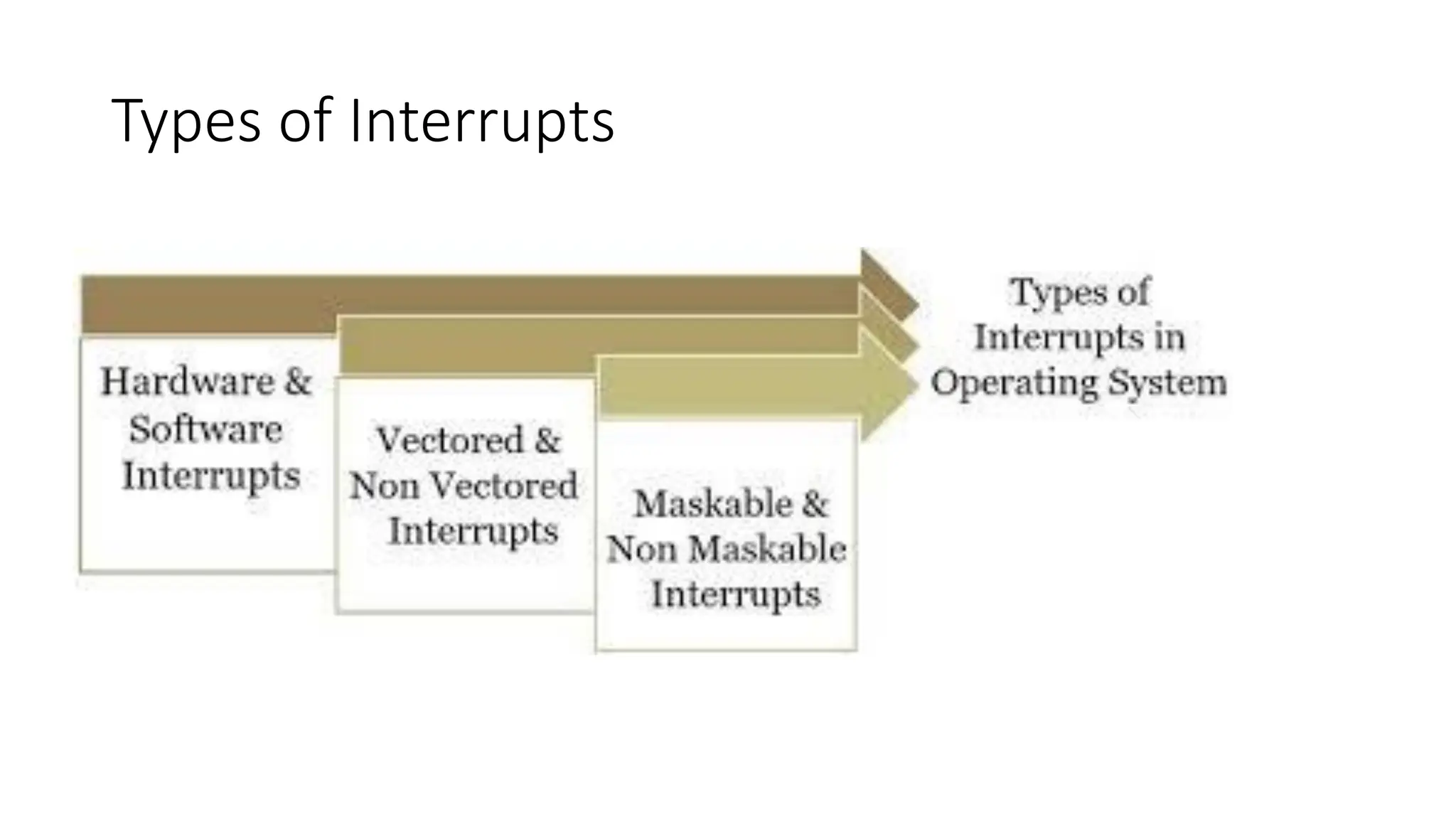

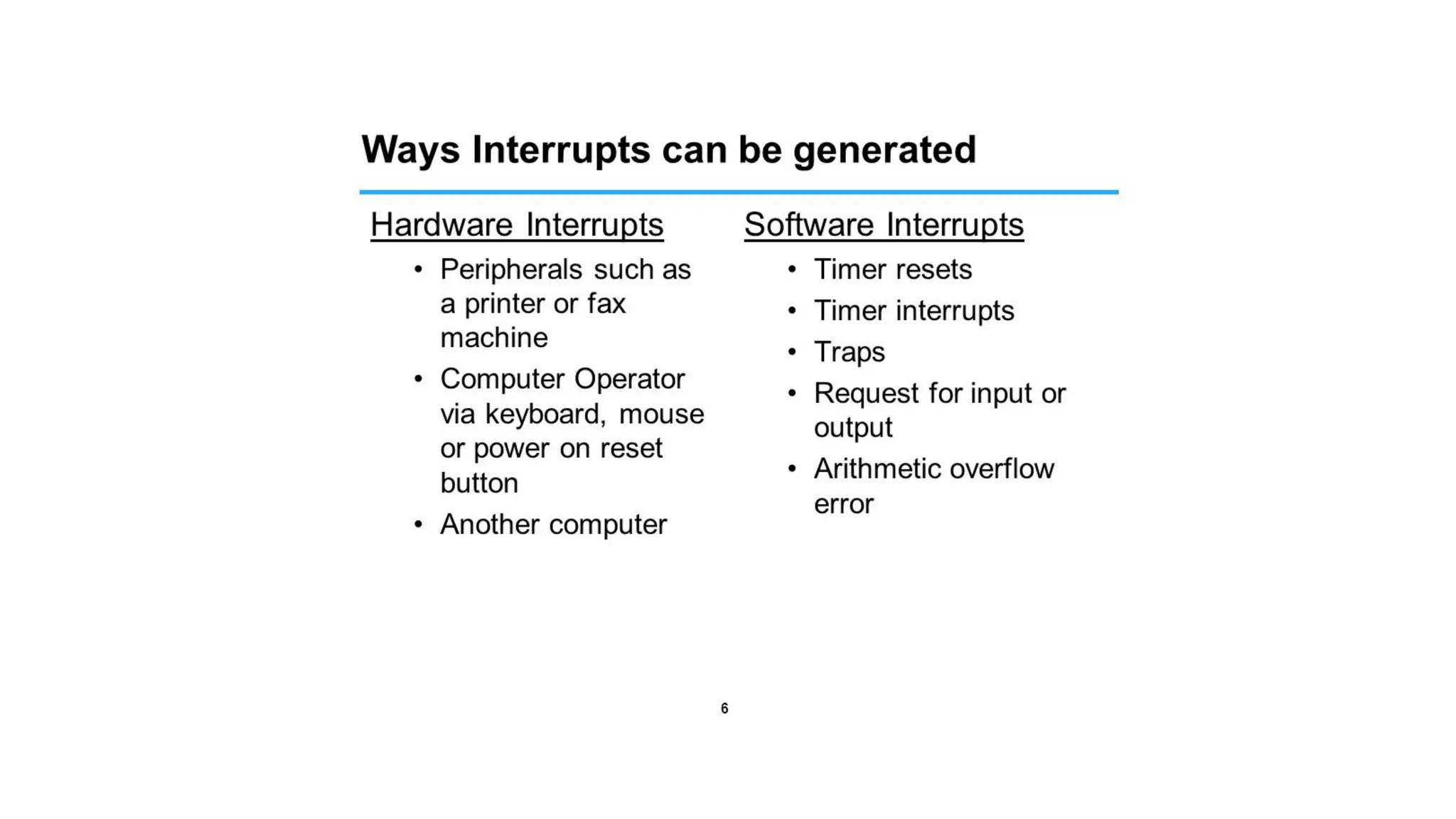

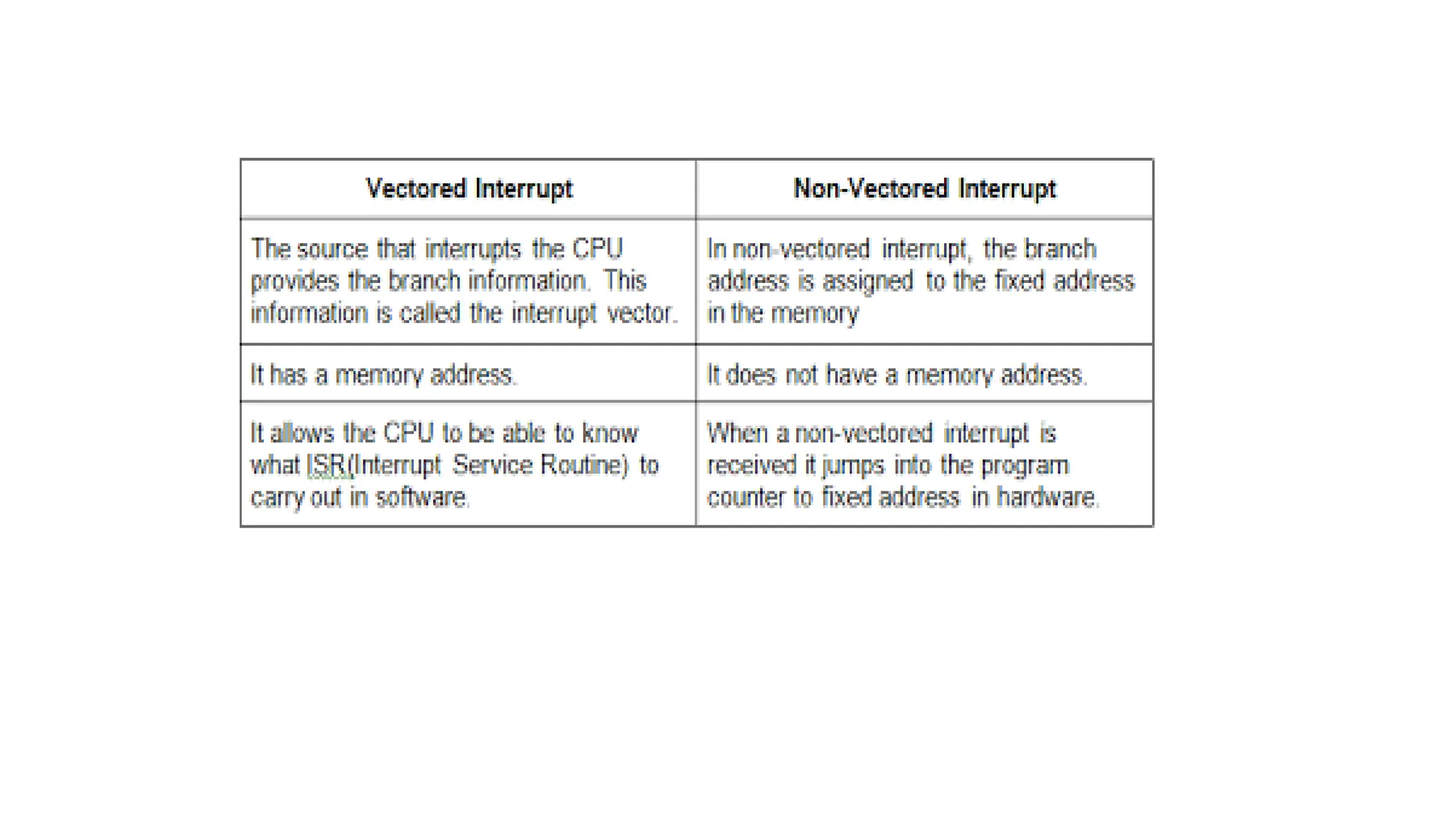

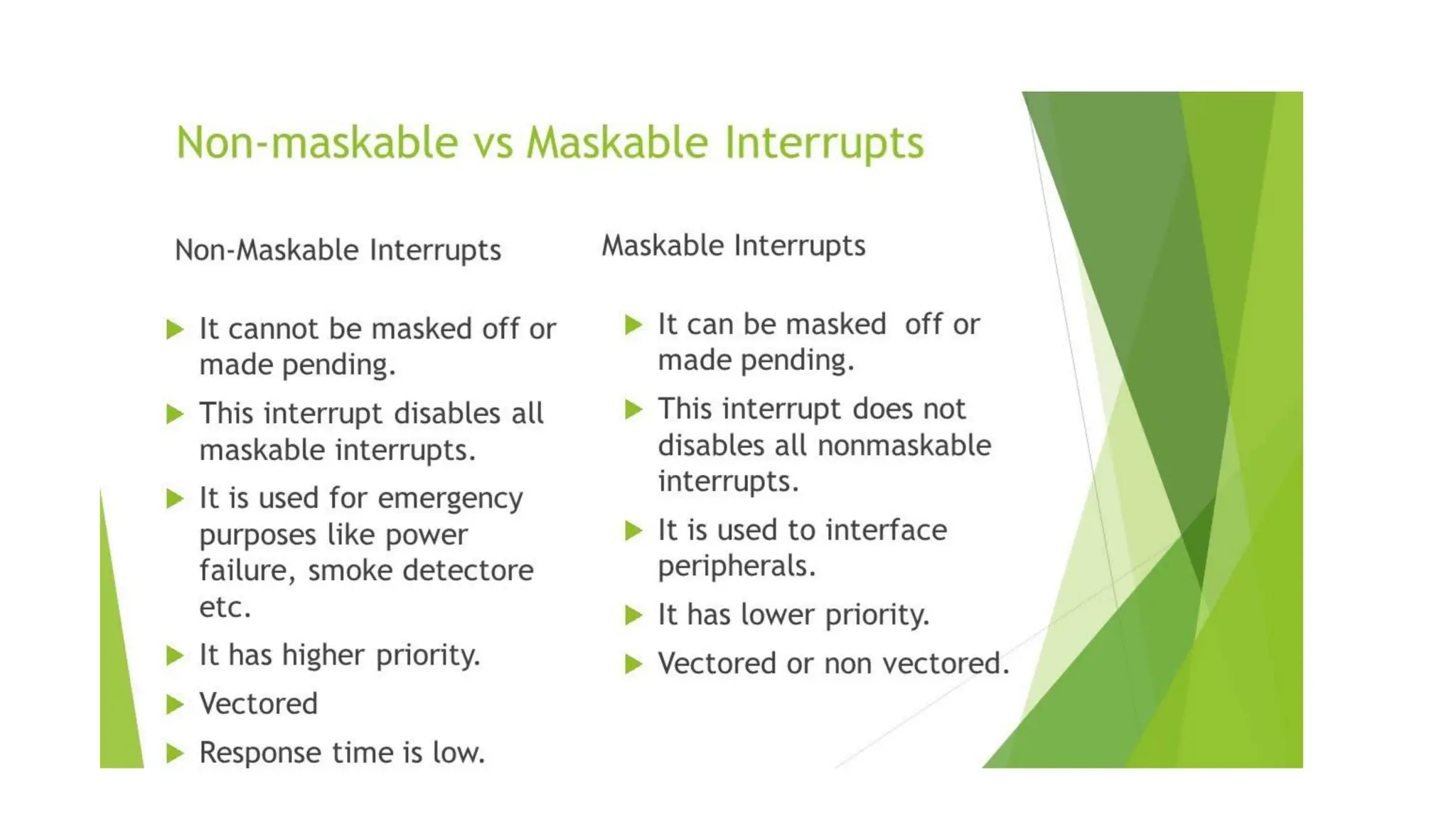

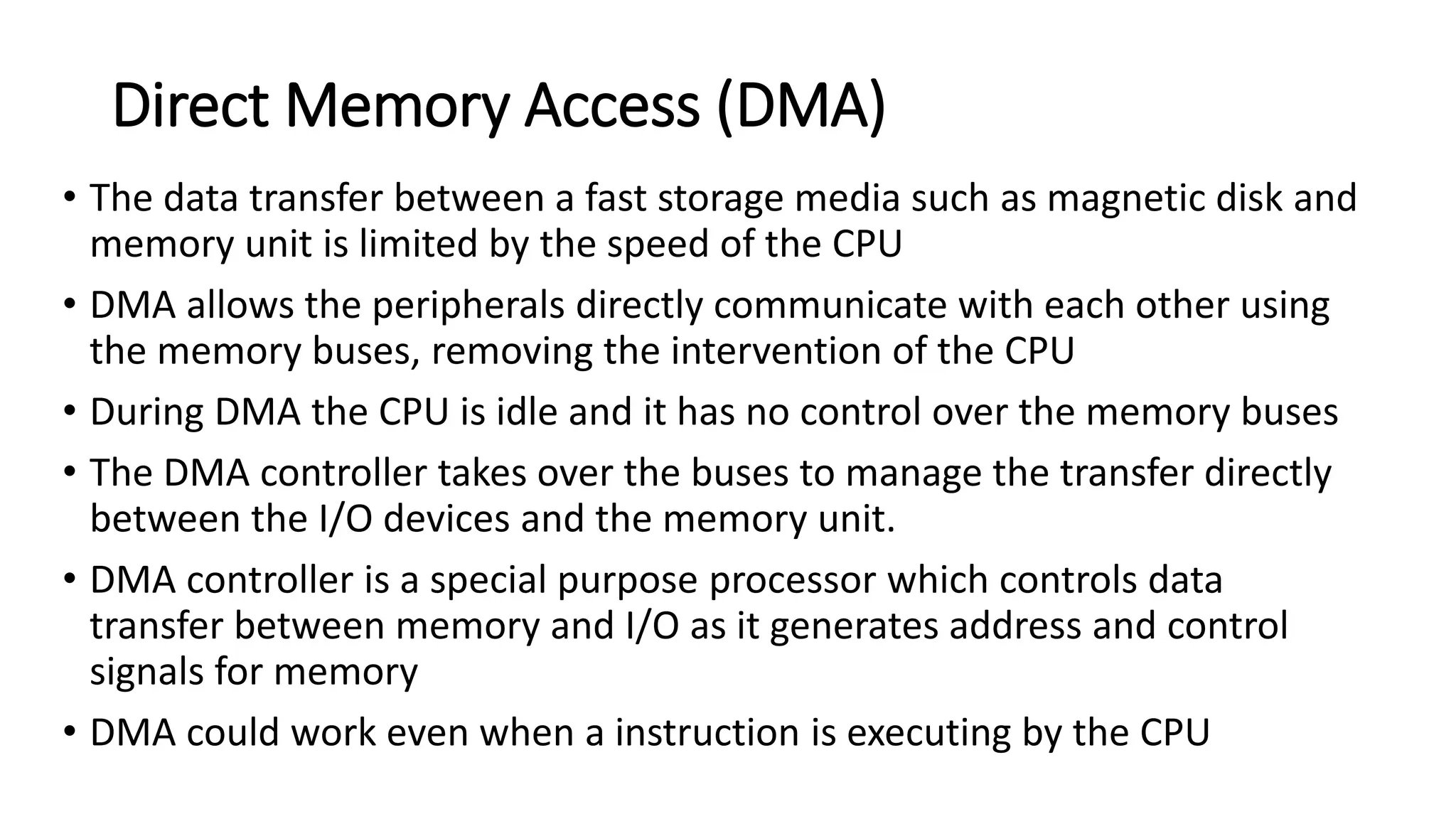

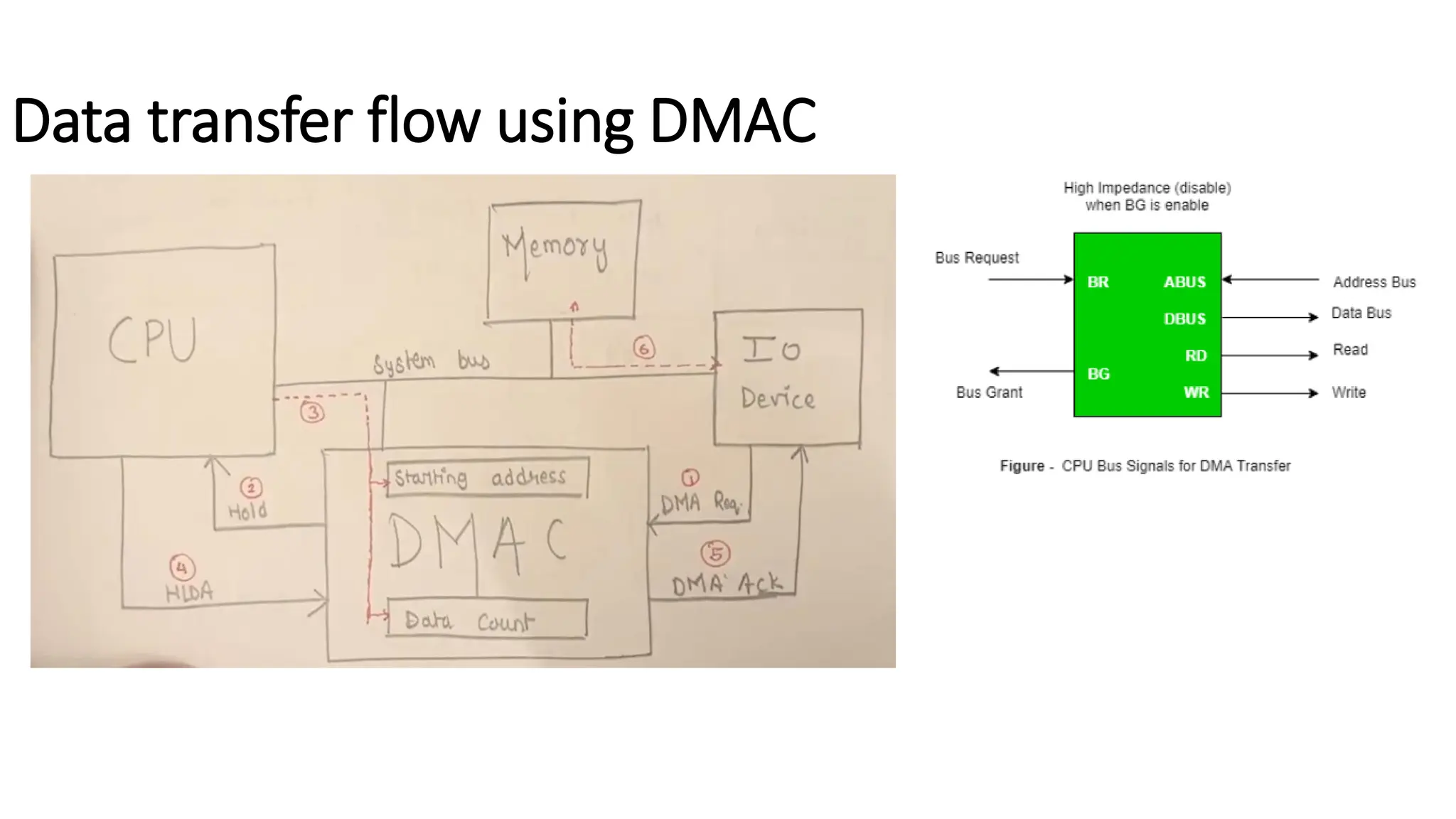

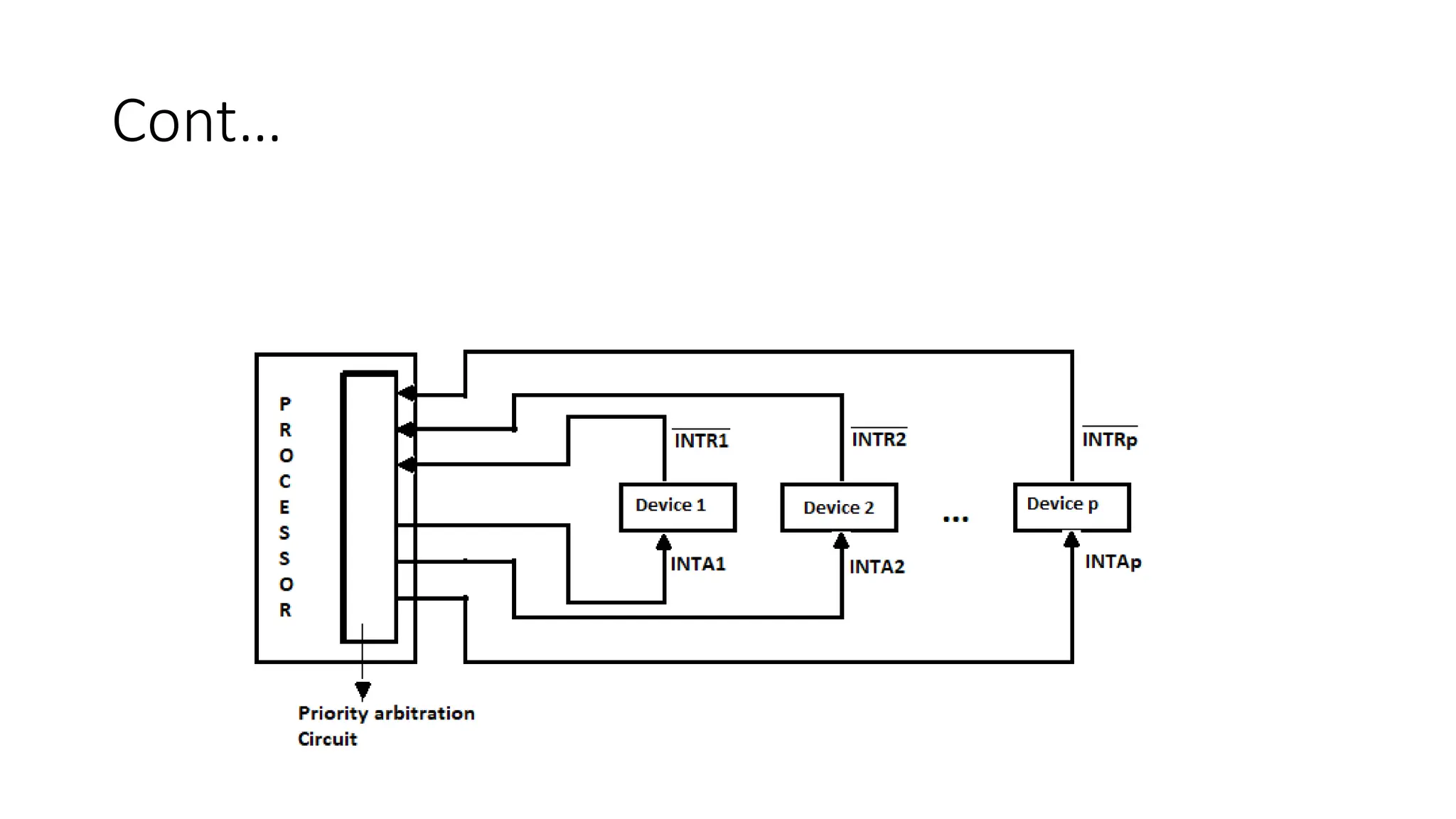

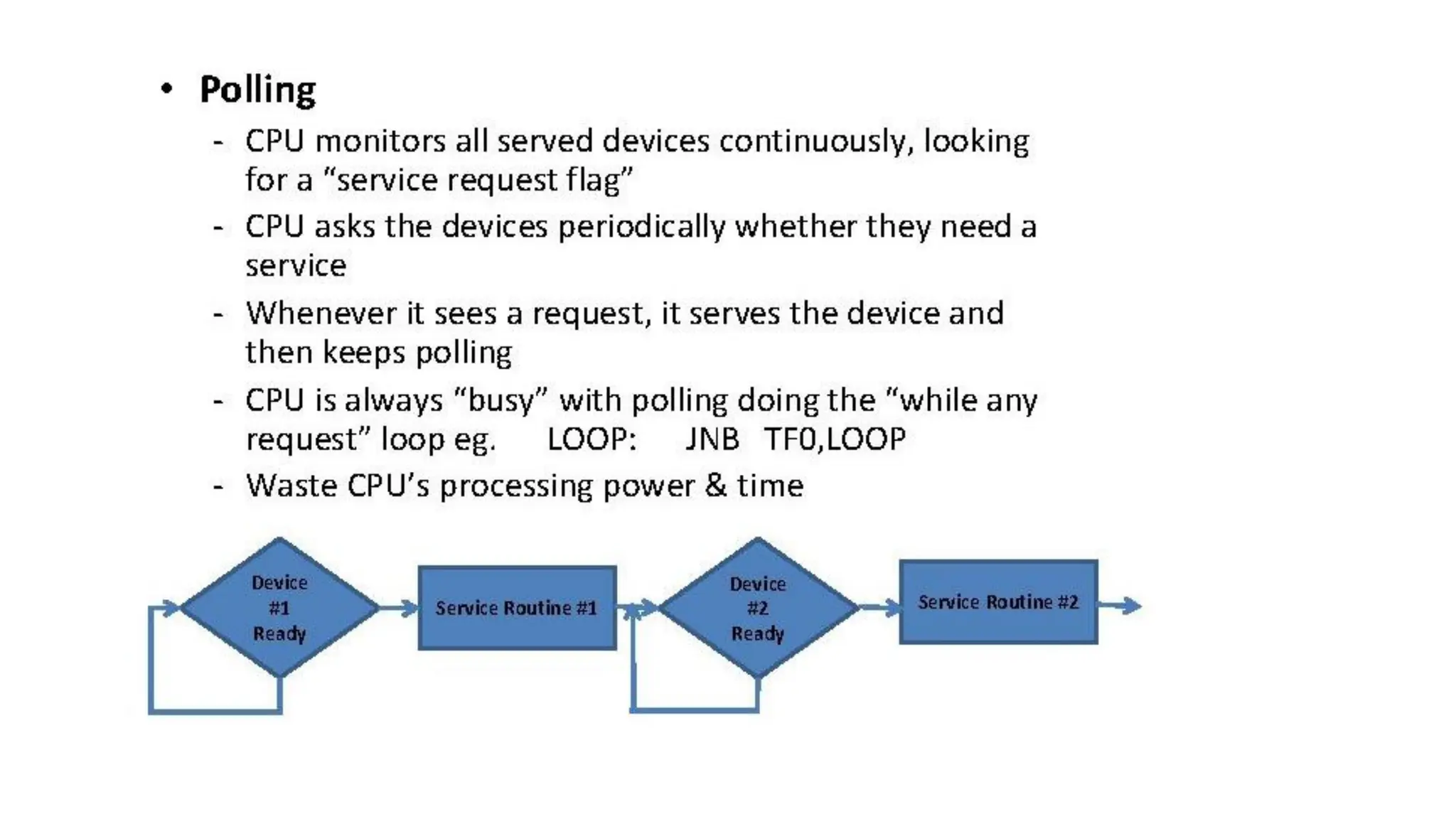

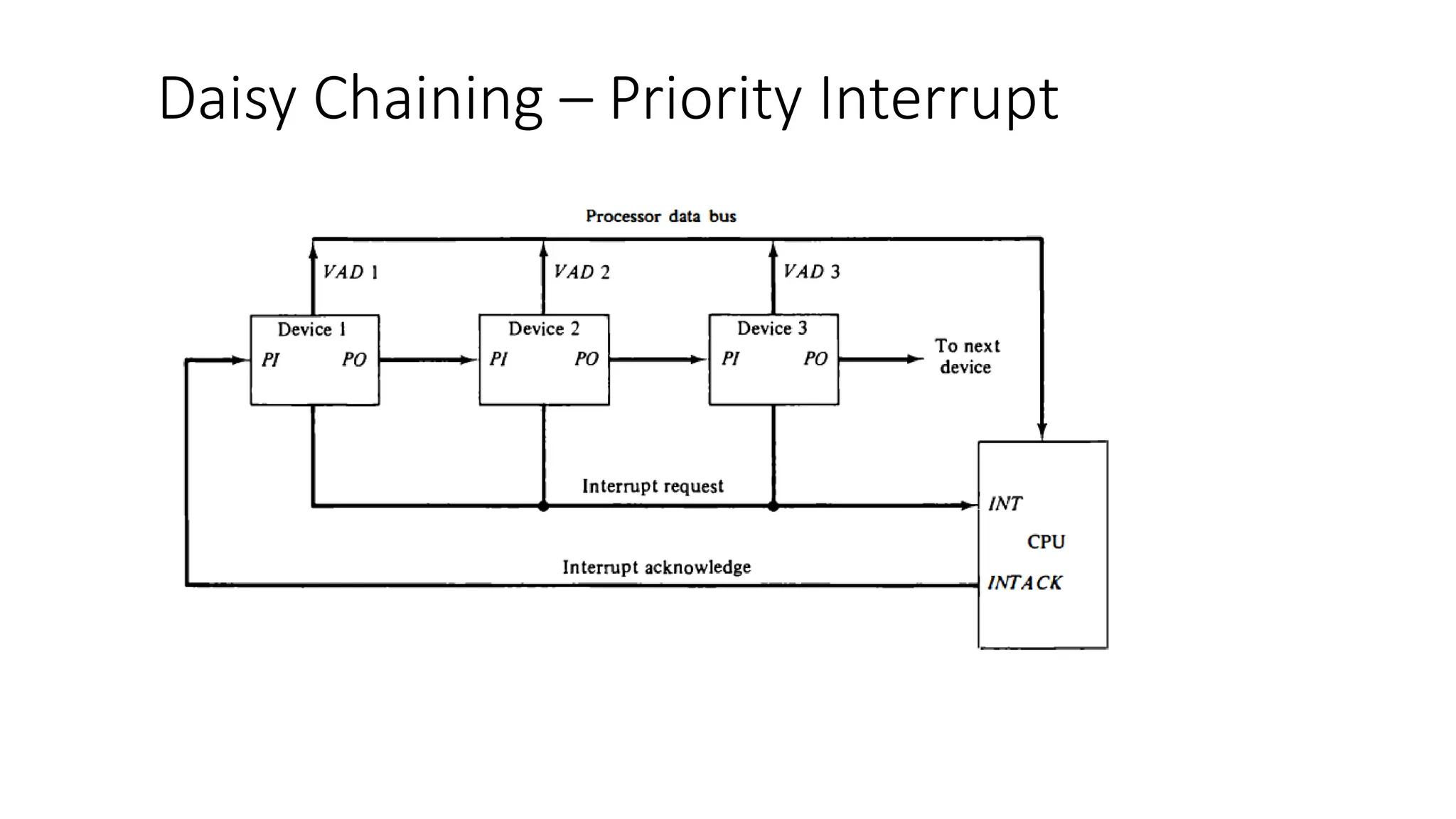

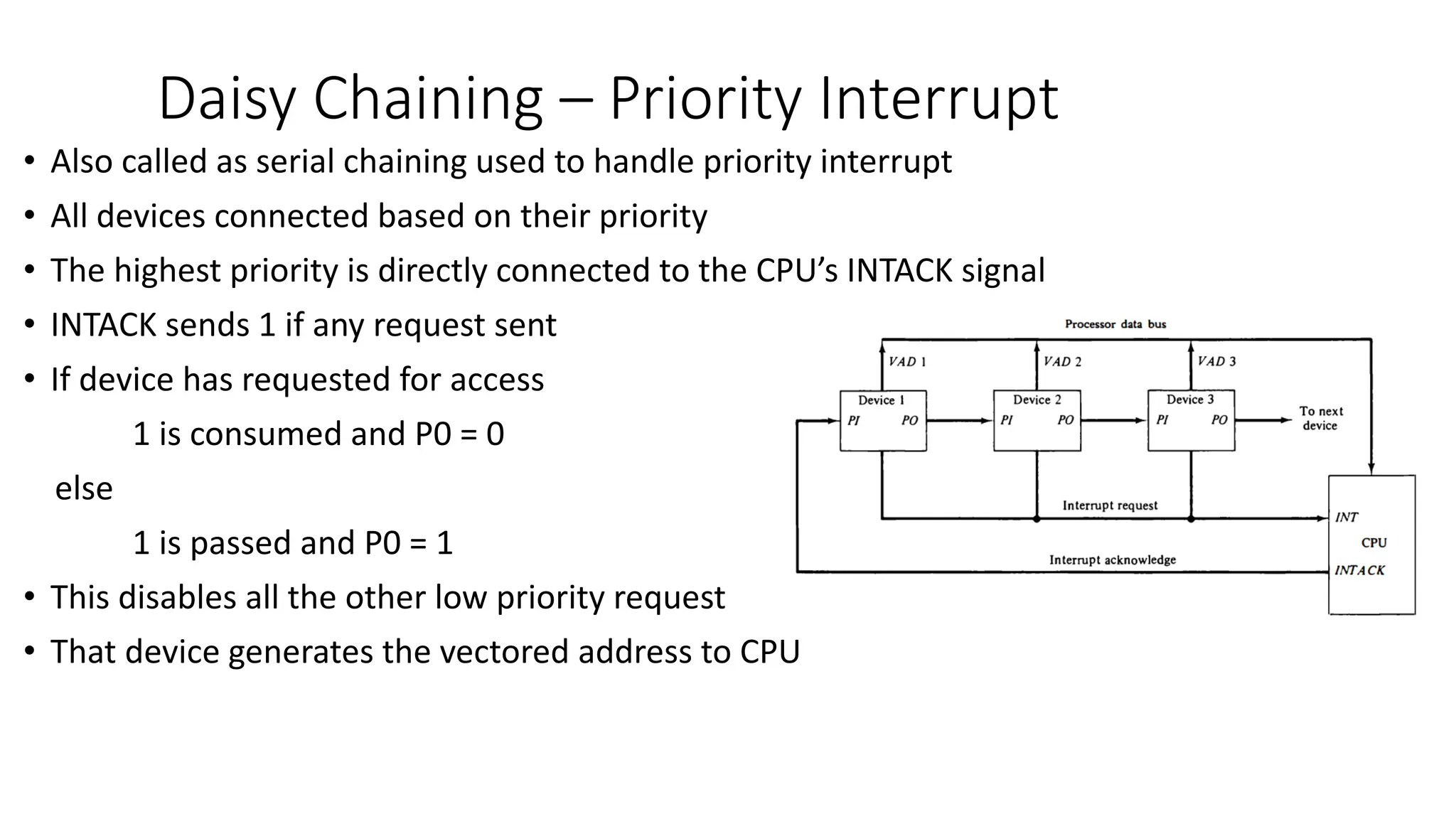

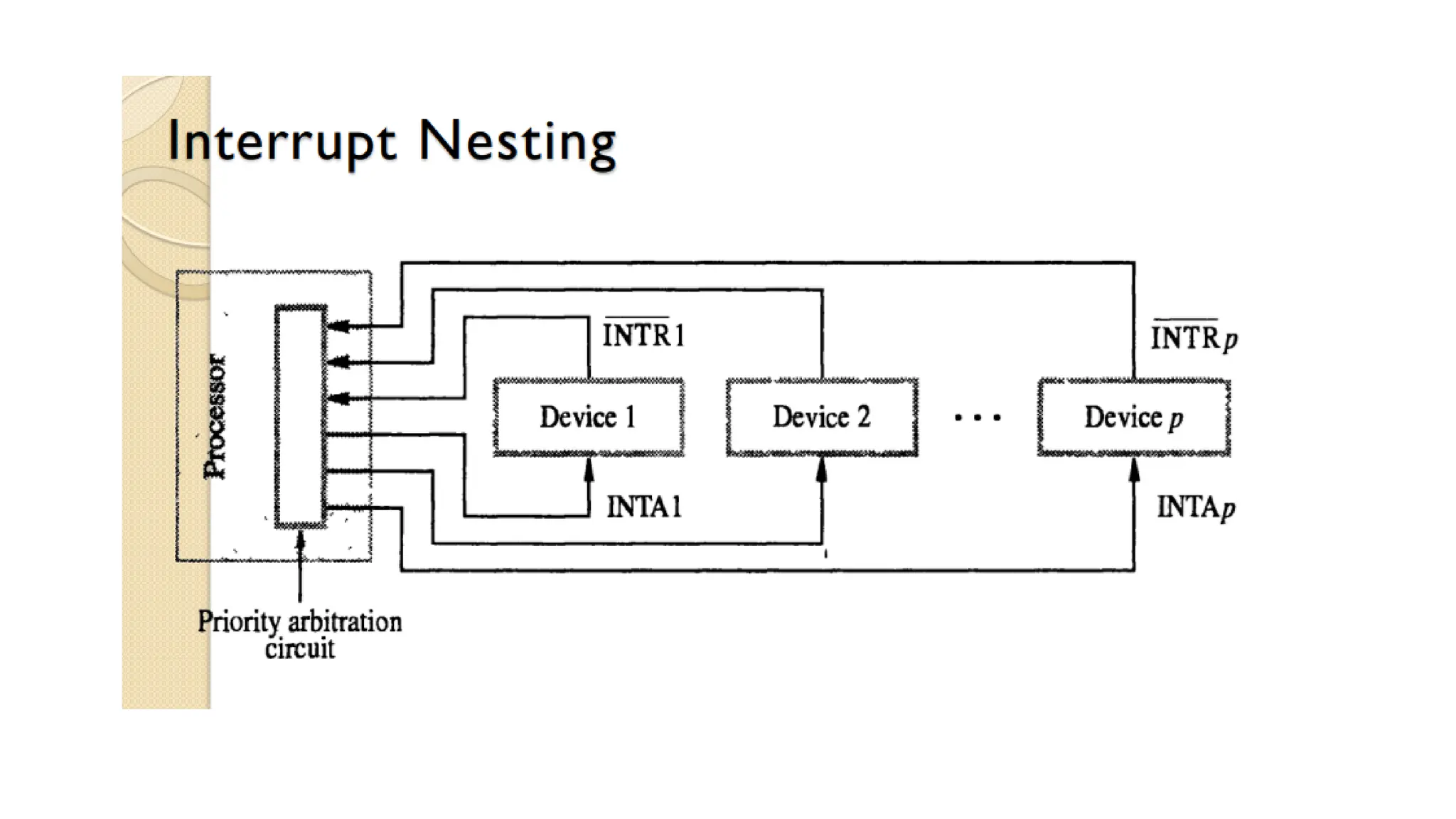

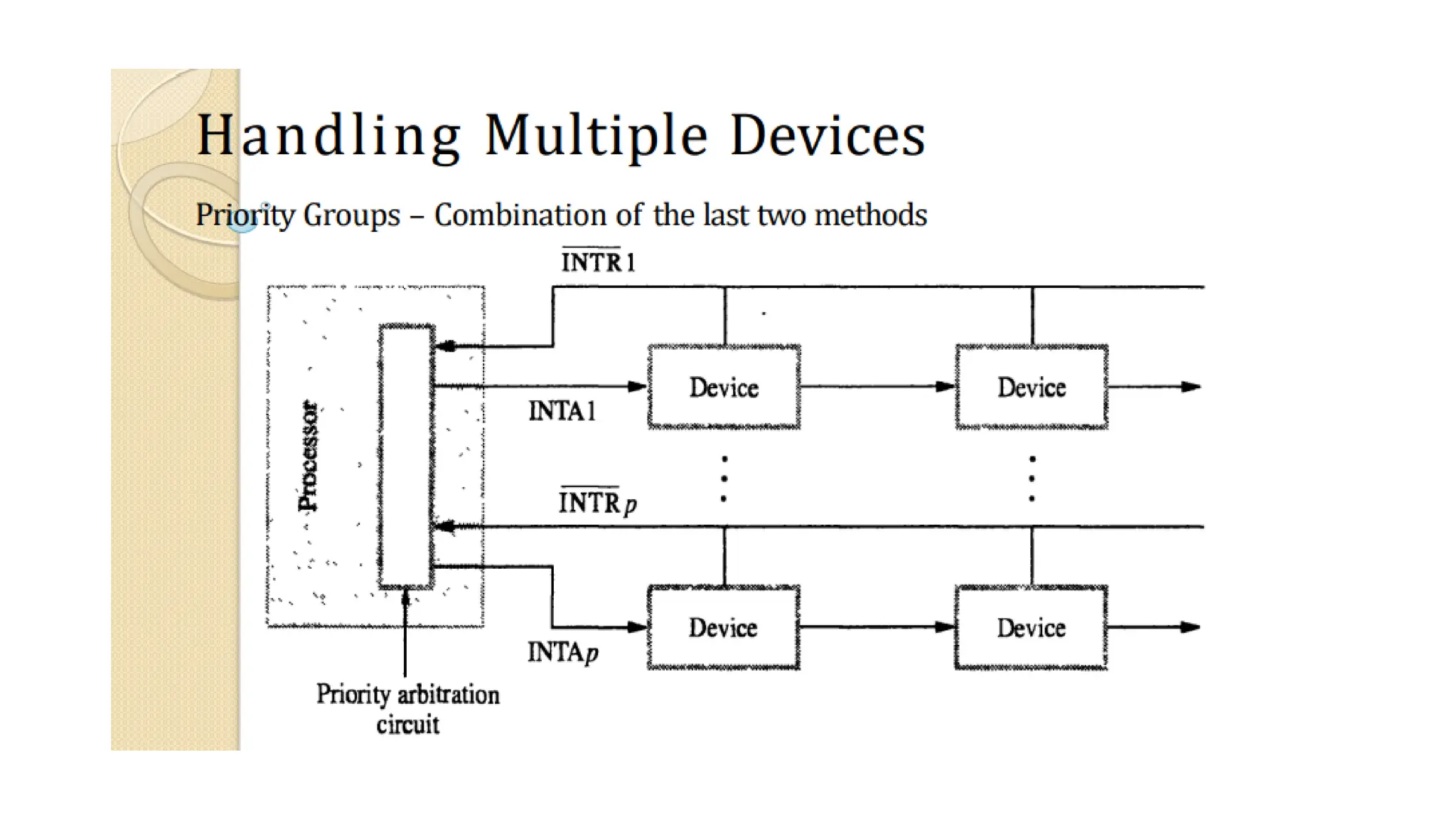

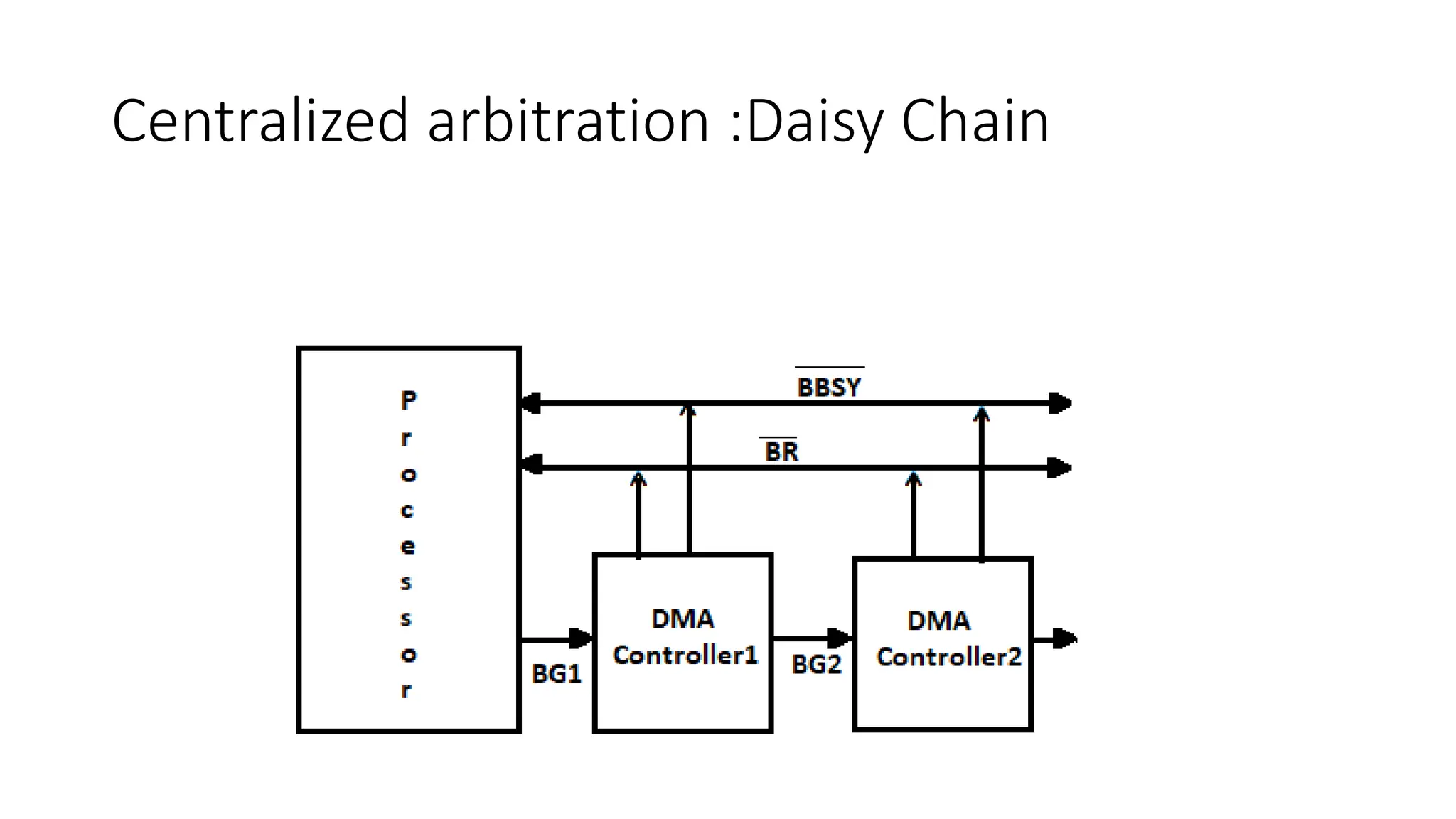

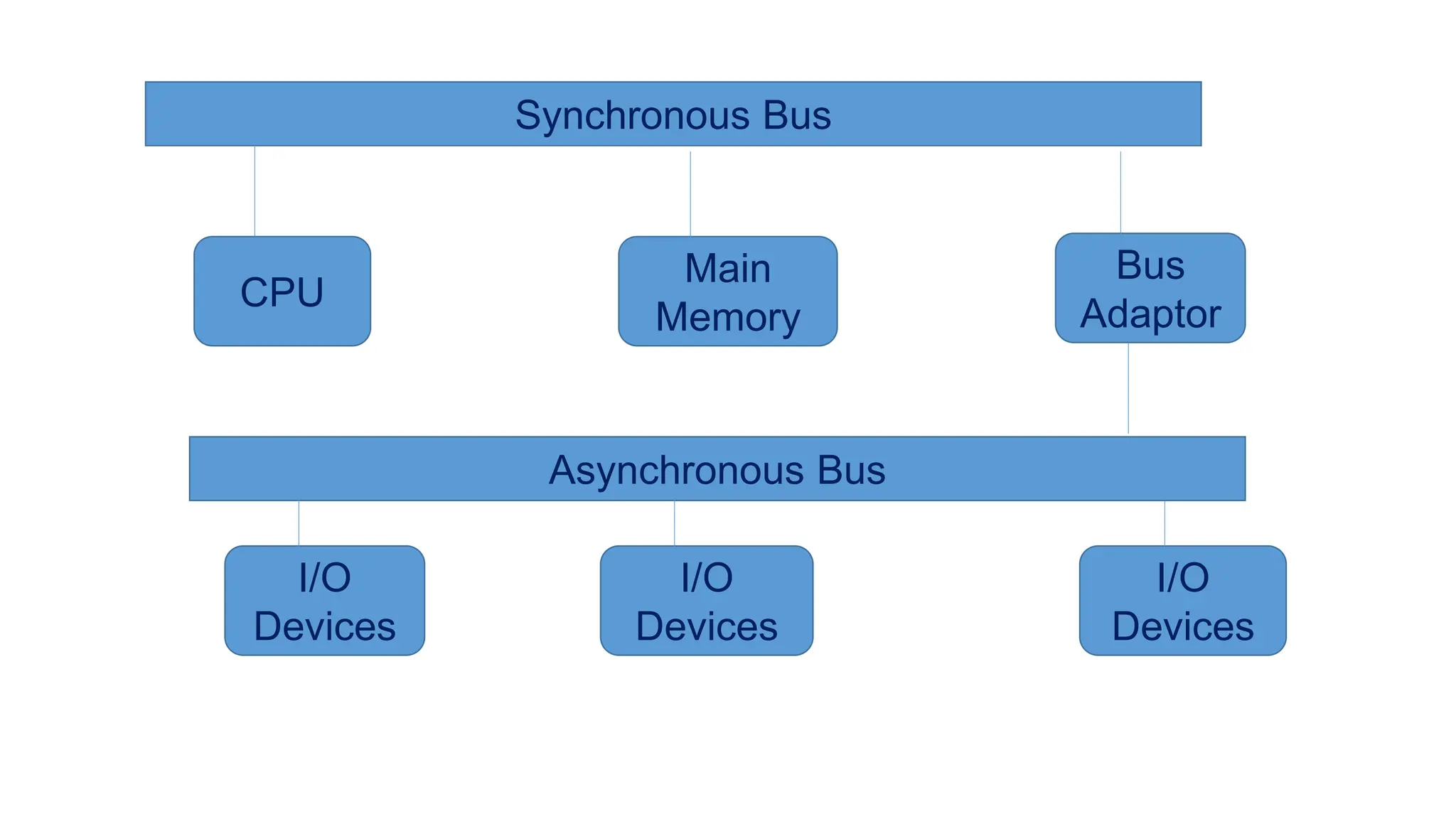

The document describes the I/O interface used for transferring information between internal storage and external devices, highlighting methods such as programmed I/O, interrupt-initiated I/O, and direct memory access (DMA). Each method has its own advantages and drawbacks regarding CPU utilization and transfer efficiency. Additionally, the document discusses interrupt handling strategies, including vectored interrupts and priority management in device requests.