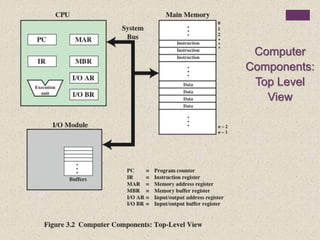

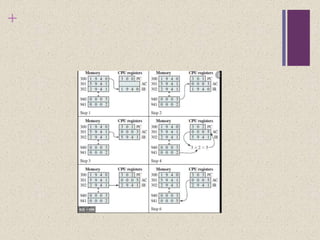

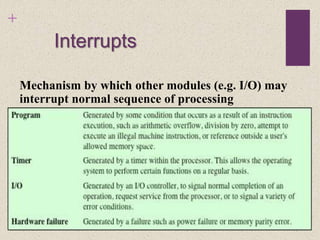

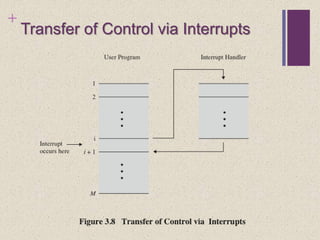

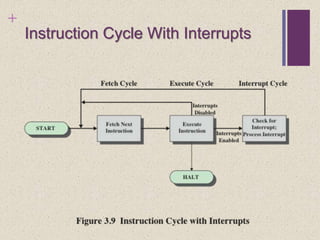

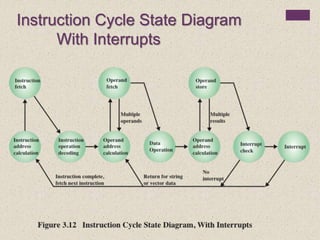

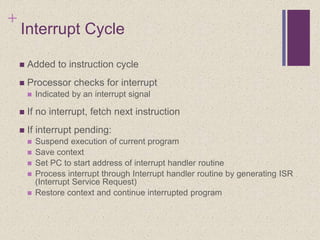

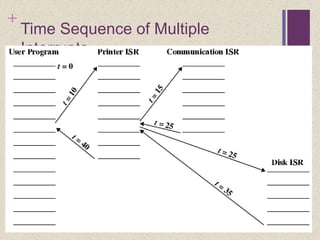

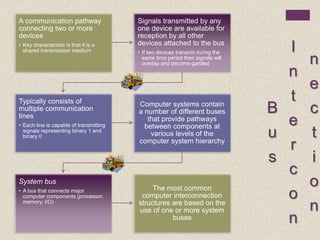

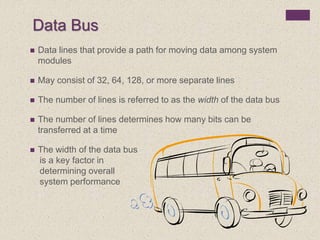

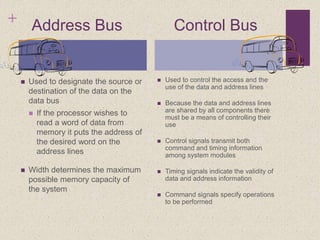

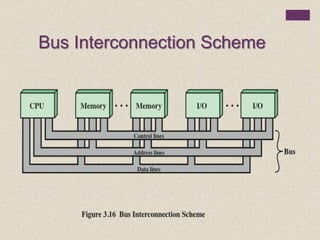

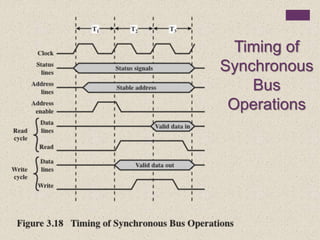

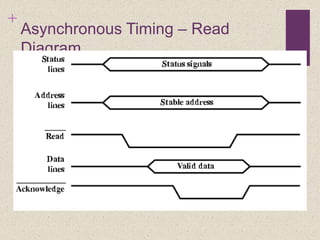

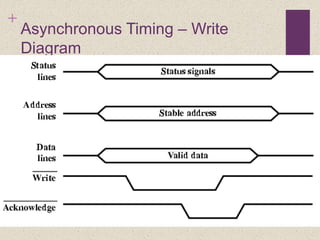

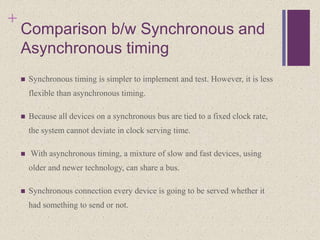

The document discusses the von Neumann architecture and basic components of a computer system. It describes how the CPU, memory, and I/O devices are interconnected via buses. The key buses are the data bus, address bus, and control bus. It explains synchronous and asynchronous timing of bus operations, with synchronous relying on a shared clock and asynchronous using handshaking signals between devices. Interrupts allow I/O devices to signal the CPU to pause normal instruction execution.