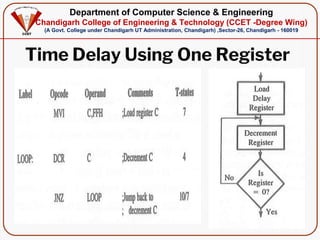

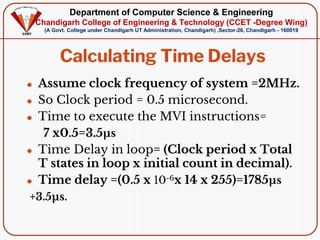

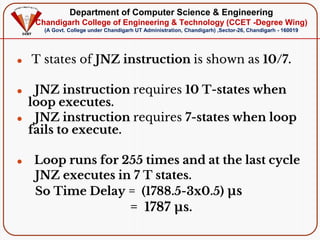

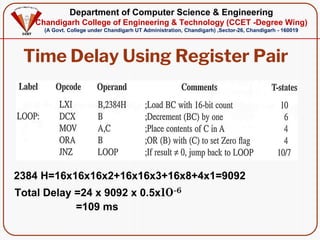

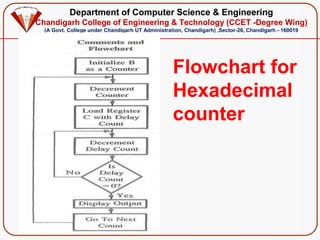

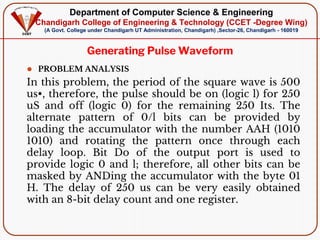

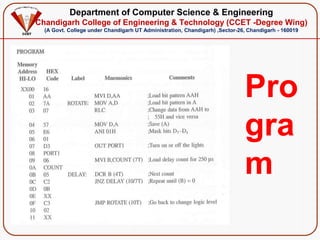

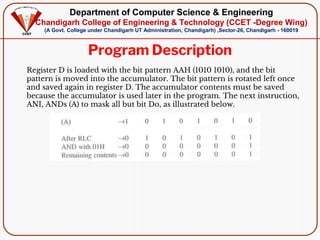

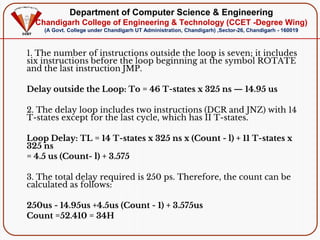

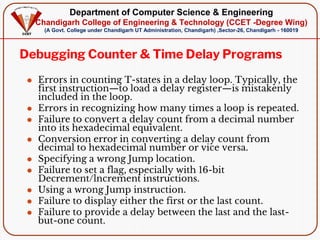

The document covers the design and programming of counters and time delays, highlighting their applications in traffic signals and digital clocks. It explains the procedures for designing counters and time delays, as well as methods for calculating time delays using register pairs. Additionally, it addresses common debugging errors encountered when implementing counter and time delay programs.