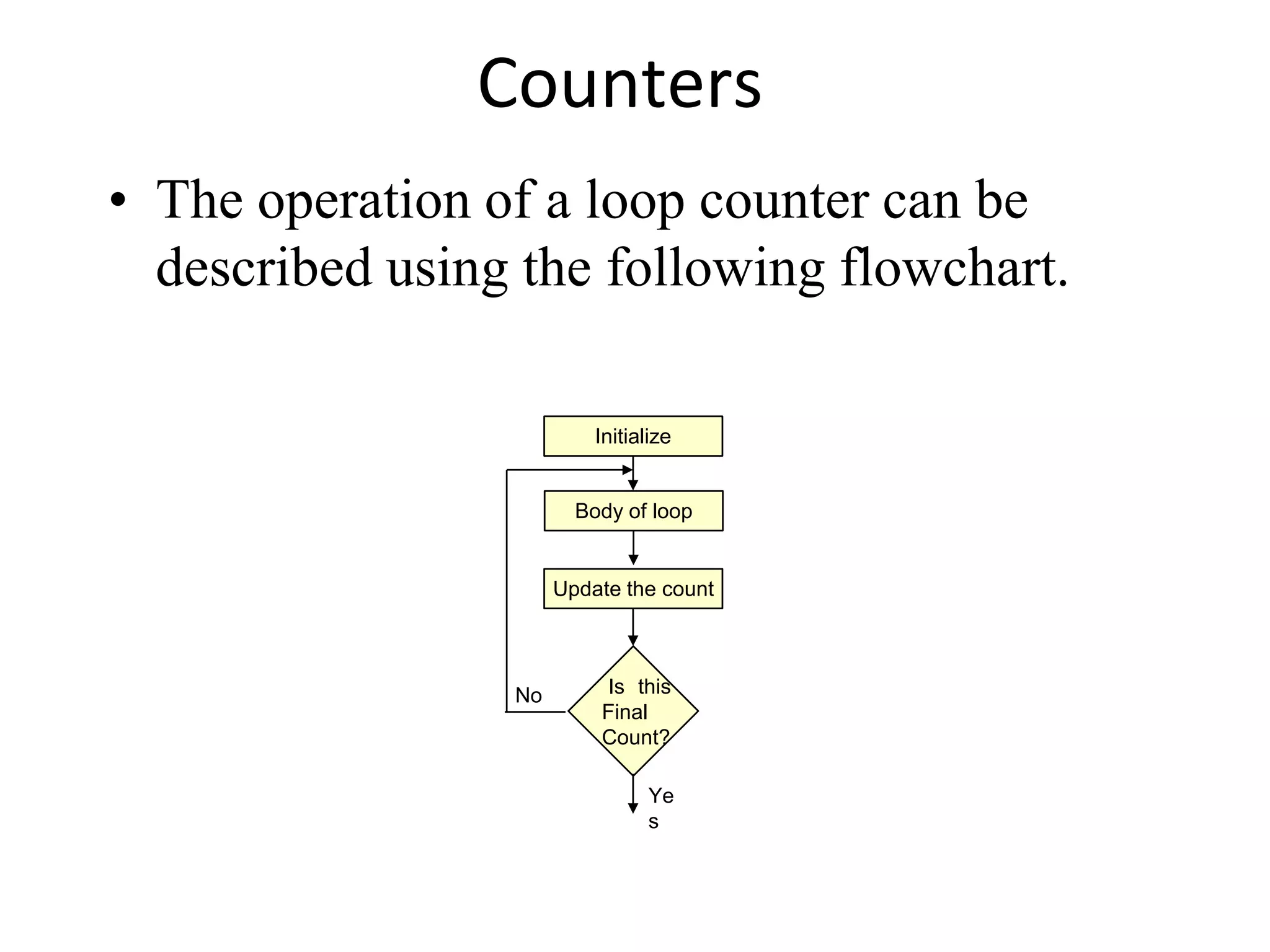

- Counters and time delays can be implemented using loops in assembly language. A loop counter is initialized and decremented/incremented at each iteration.

- Using a single register allows looping up to 255 times. A register pair can extend this by ORing the registers and checking the zero flag.

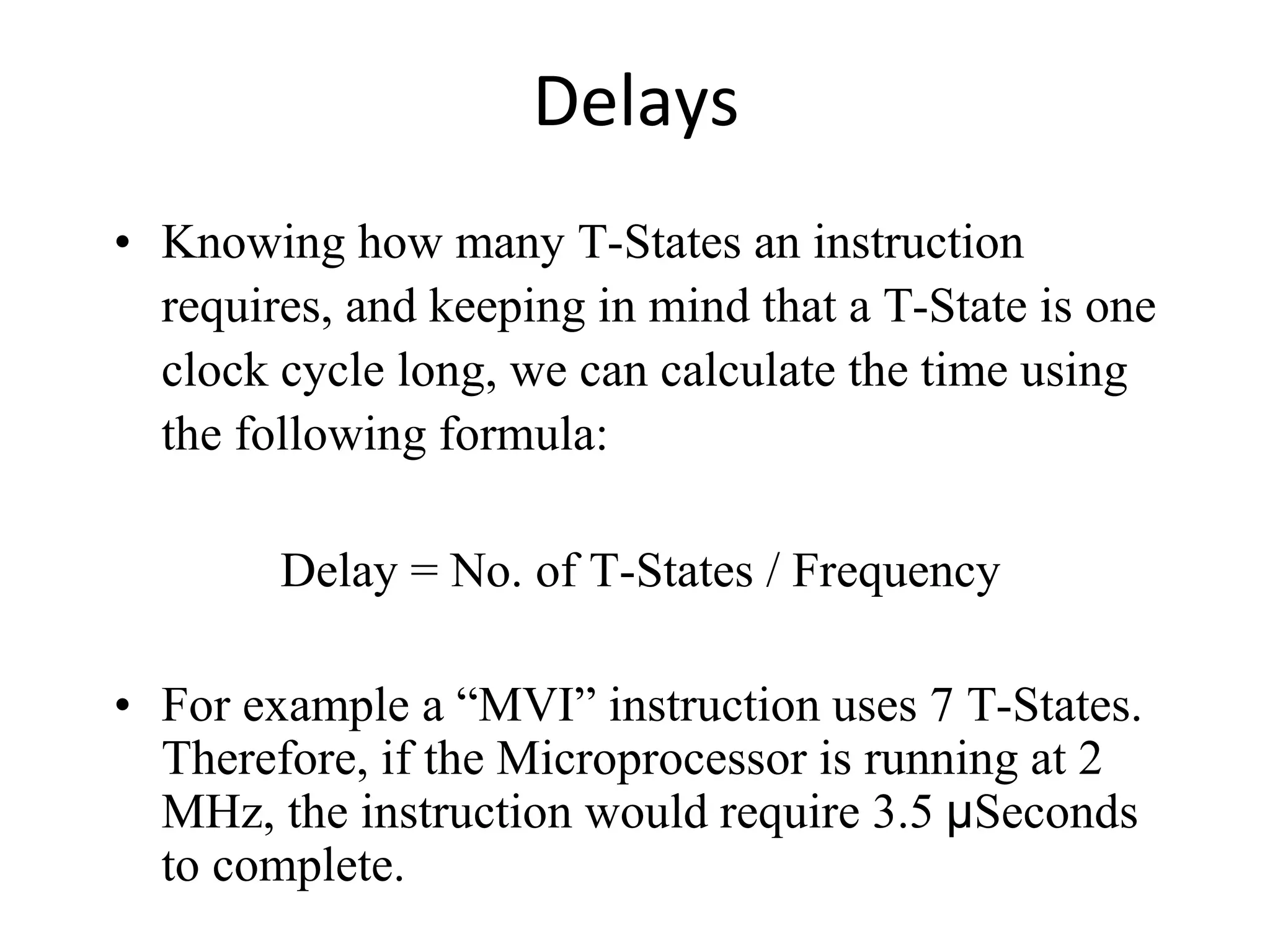

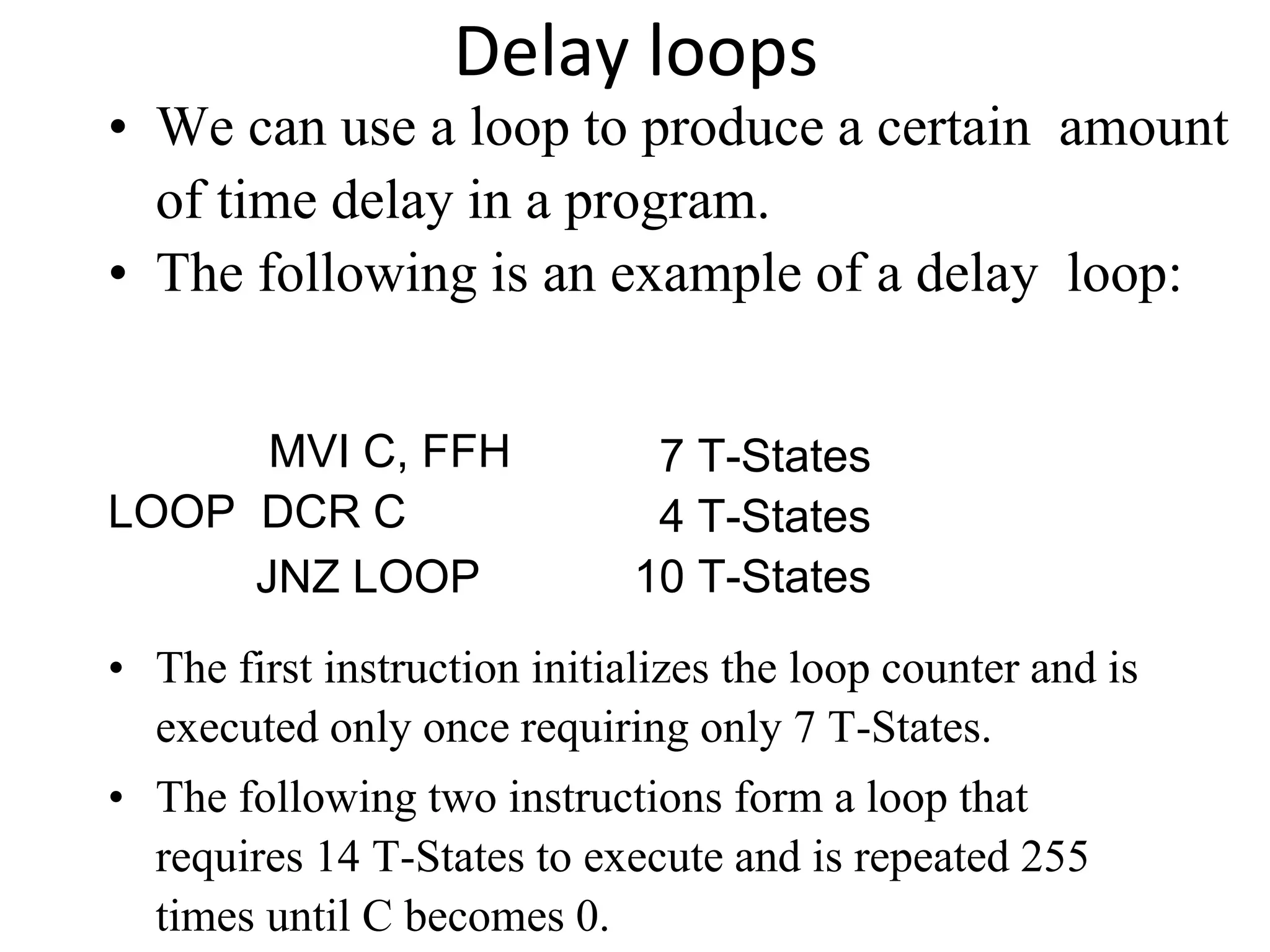

- Instruction timing is measured in T-states. Delay loops produce a timed delay by repeating instructions a set number of times.

- Nested loops place one loop inside another to further increase delay time by repeating the inner loop multiple times.