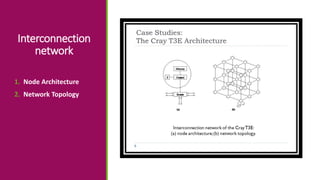

The document summarizes the Cray T3E supercomputer architecture. It discusses that the Cray T3E uses Alpha EV5 RISC microprocessors across multiple processing elements. It has its own local memory per processing element ranging from 64MB to 2GB. The architecture supports scalability to add more processors, memory, I/O and interconnect bandwidth. It uses a distributed operating system and has features like multiple ports for input/output and an interconnect network between processing nodes.